Hardware-Debugging

Low-Power-Designs unter der Lupe

Fortsetzung des Artikels von Teil 3

Low-Power-Designs unter der Lupe

Darüber hinaus muss die Lösung folgende Funktionen bieten:

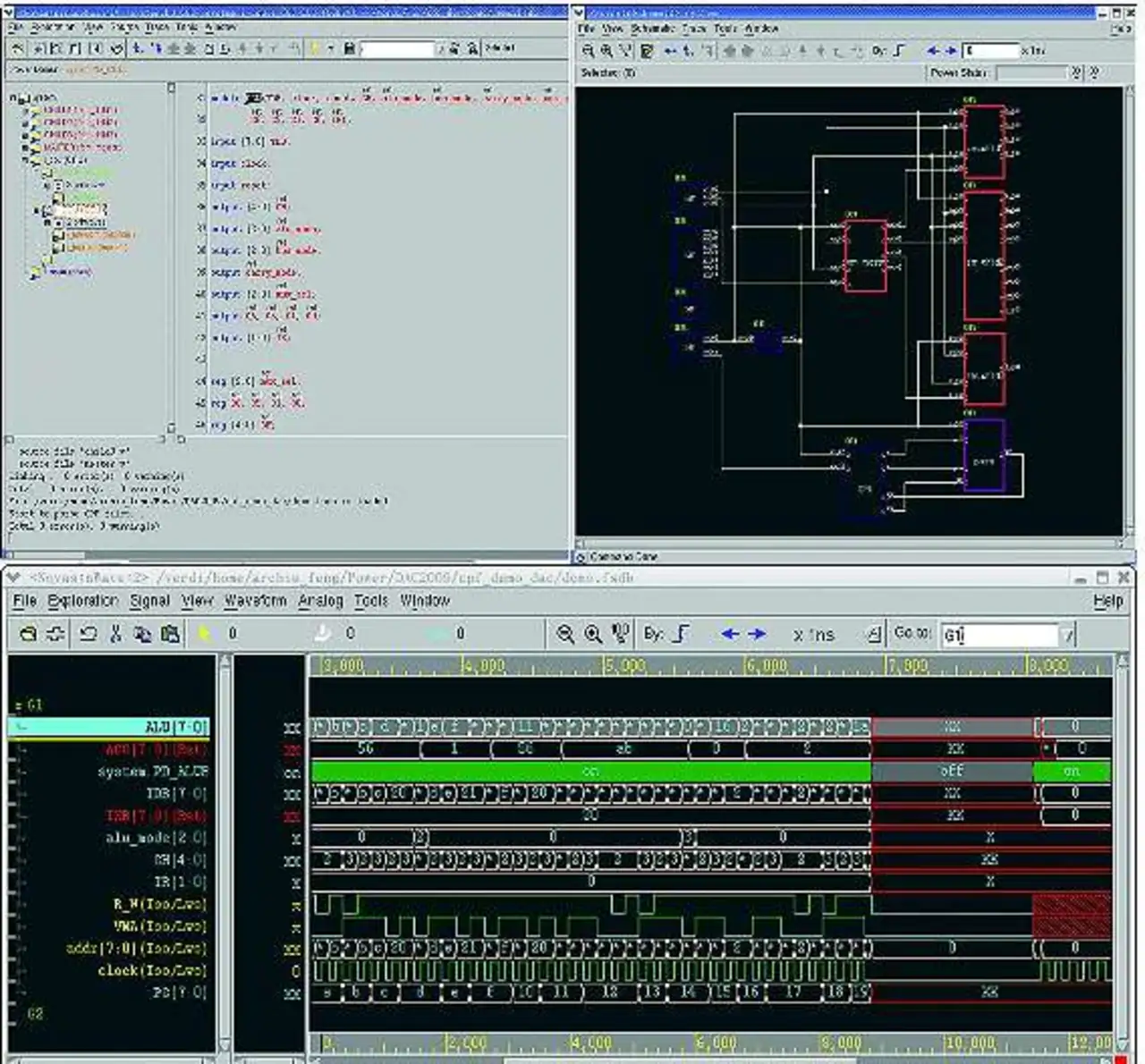

■■ Eine UPF/CPF-basierte Darstellung, sodass sich die spezifizierten Power-Elemente wie Schaltregeln, Regeln für Retention-und Isolationszellen sowie Pegelumsetzer leicht lokalisieren lassen. Eine Annotation der Power-Merkmale in RTL-, Schaltplan- und Wellenform-Darstellungen, mit deren Hilfe der Anwender die Power-Merkmale mit den zugehörigen Designblöcken korrelieren kann. Dadurch kann er bestimmen, welche Blöcke zu welchen Spannungsinseln gehören und welche Signale zur Erhaltung eines Signalwertes oder als Pegelumsetzer für eine Spannungsinsel dienen.

■■ Eine simultane Anzeige (Cross Probing) zwischen der UPF/CPF-Darstellung und den RTL-, Schaltplan- und Wellenform-Darstellungen, damit sich ein Design- oder Power-Objekt in jeder Darstellung lokalisieren lässt. So kann mit Hilfe der Cross-Probing-Funktion ein in UPF/CPF formuliertes Retention-Signal in der schematischen Darstellung visualisiert und der zugehörige Signalpfad anschließend untersucht werden.

■■ Eine Visualisierung von Spannungsinseln und Power-Status bzw. -Modi (Bild 3). Um dem Ingenieur seine Arbeit zu erleichtern, muss eine Debug-Lösung, die auch für die Analyse und Behebung von Power-Problemen geeignet sein soll, folgende automatisierte Funktionen für die Suche nach der Fehlerursache im RTL-Code oder der Power-Spezifikation bieten:

■■ Eine Möglichkeit zur automatischen Lokalisierung von Treibern/Lasten in RTL- und CPF/UPF-Code.

■■ Eine Visualisierung von Signalen, deren Treiber in CPF/UPF spezifiziert sind. Dadurch können Anwender auch Fehler in der CPF/UPF-Spezifikation finden und beheben.

Jobangebote+ passend zum Thema

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe