Hardware-Debugging

Low-Power-Designs unter der Lupe

Fortsetzung des Artikels von Teil 1

Low-Power-Designs unter der Lupe

Power-Merkmale verstehen

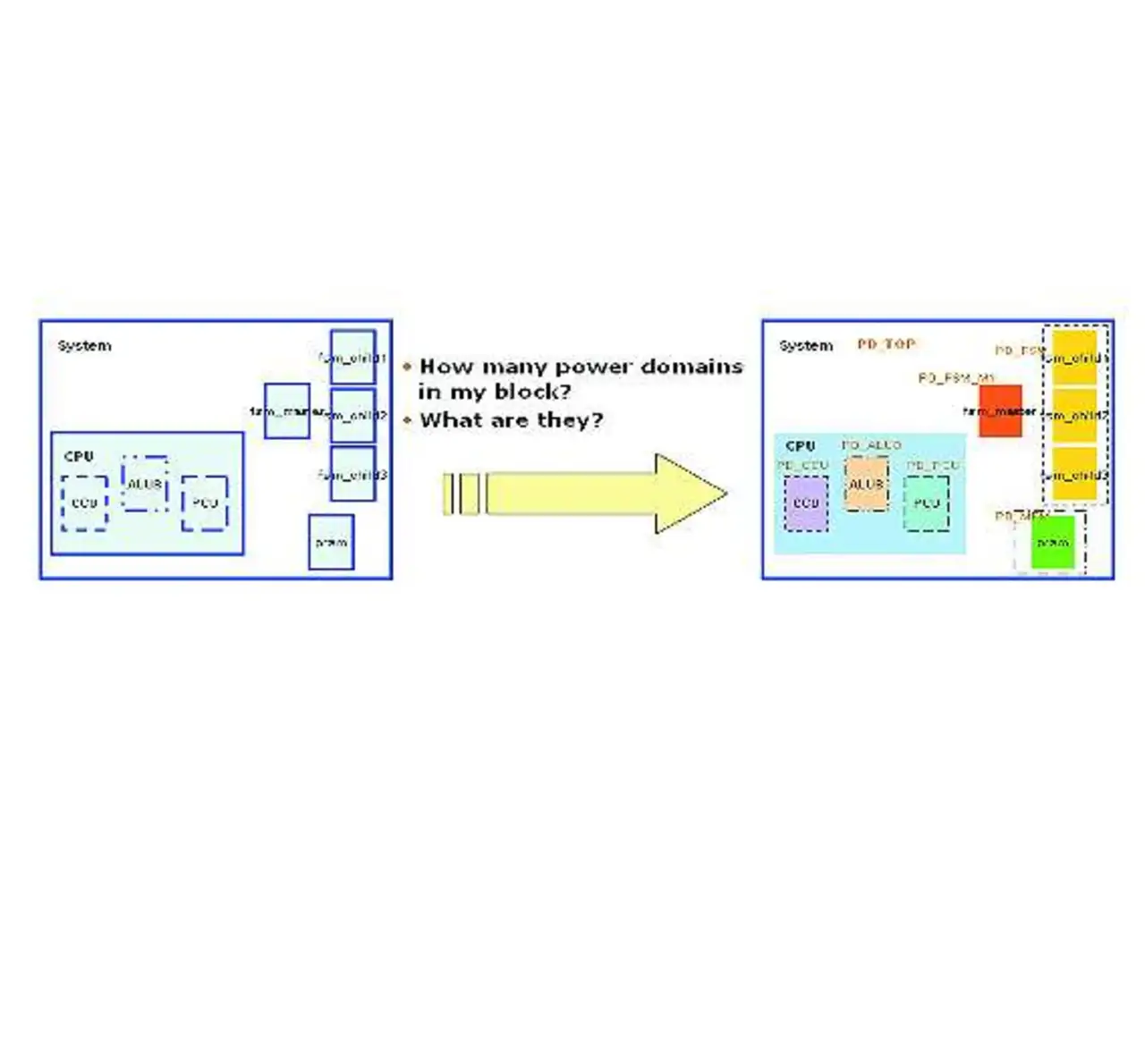

Nicht selten wird die Aufgabe, UPFund CPF-Spezifikationen zu erstellen, den System- und Chip-Level-Designern übertragen. Ein nicht beteiligter RTL-Ingenieur kann dann die Auswirkungen der Spezifikationen auf das Block-Level-Design nicht ohne weiteres nachvollziehen. Ein Subblock in einem hierarchischen RTL-Design kann beispielsweise mehrere Spannungsinseln beinhalten, die jeweils unterschiedlichen Regeln für das Ein- und Ausschalten der Spannungsversorgung unterliegen. Für jede Insel gelten wiederum individuelle Vorschriften für die dort verwendeten Pegelumsetzer sowie Gatter zur Isolation und Erhaltung von Signalen. Eine so geartete Schaltung zeigt in einer Simulation, die Power-Aspekte berücksichtigt, ein Verhalten, das sich von dem einer Schaltung unterscheidet, bei der es nicht auf den Stromverbrauch ankommt und bei der daher alle Elemente während des Betriebs eingeschaltet bleiben. Letzteres war bislang der Normalfall für RTL-Ingenieure. Es ist daher besonders wichtig, dass ihnen das Verständnis der Power-Merkmale eines Blocks erleichtert wird, an dem sie arbeiten sollen. Angenommen, ein RTL-Entwickler arbeitet an einem CPU-Block, wie er in Bild 1 zu sehen ist, und er will wissen, zu welchen Spannungsinseln dieser mit seinen untergeordneten Blöcken gehört. Im Falle der Beispielschaltung würde er feststellen, dass der CCU-Subblock der Domäne PD_CCU, der Subblock ALUB der Domäne PD_ALUB und der Subblock PCU der Domäne PD_PCU zugeordnet ist.

Jobangebote+ passend zum Thema

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe