Demoboard für A/D-Wandler

Formel 1 der Datenwandlung

Fortsetzung des Artikels von Teil 2

Demo-Kits

Beim Design von Systemen mit schnellen A/D-Wandlern sind die vielfältigsten Aspekte zu berücksichtigen, wie etwa Konzepte der digitalen Signalverarbeitung, das Design ultrabreitbandiger Verstärker und der Entwurf stabiler, rauscharmer Taktsysteme und von Leiterbahnen mit konstanter Impedanz. Ein Referenzdesign-Board, das alle diese Erwägungen berücksichtigt und zu einem Wandlersystem mit voller Leistung bündelt, macht somit ein zeitsparendes Design möglich.

Eine solche Lösung kann ebenfalls zum Benchmarking der Bauelemente mit Testergebnissen und zur Herstellung eines Prototyps genutzt werden, der als eine Art Machbarkeitsstudie für das endgültige System dient. Das Design sollte dabei außerdem so flexibel sein, dass es an das vom Kunden bevorzugte DSP-System angeschlossen werden kann. Normalerweise wird bei diesen hohen Datenraten ein FPGA verwendet.

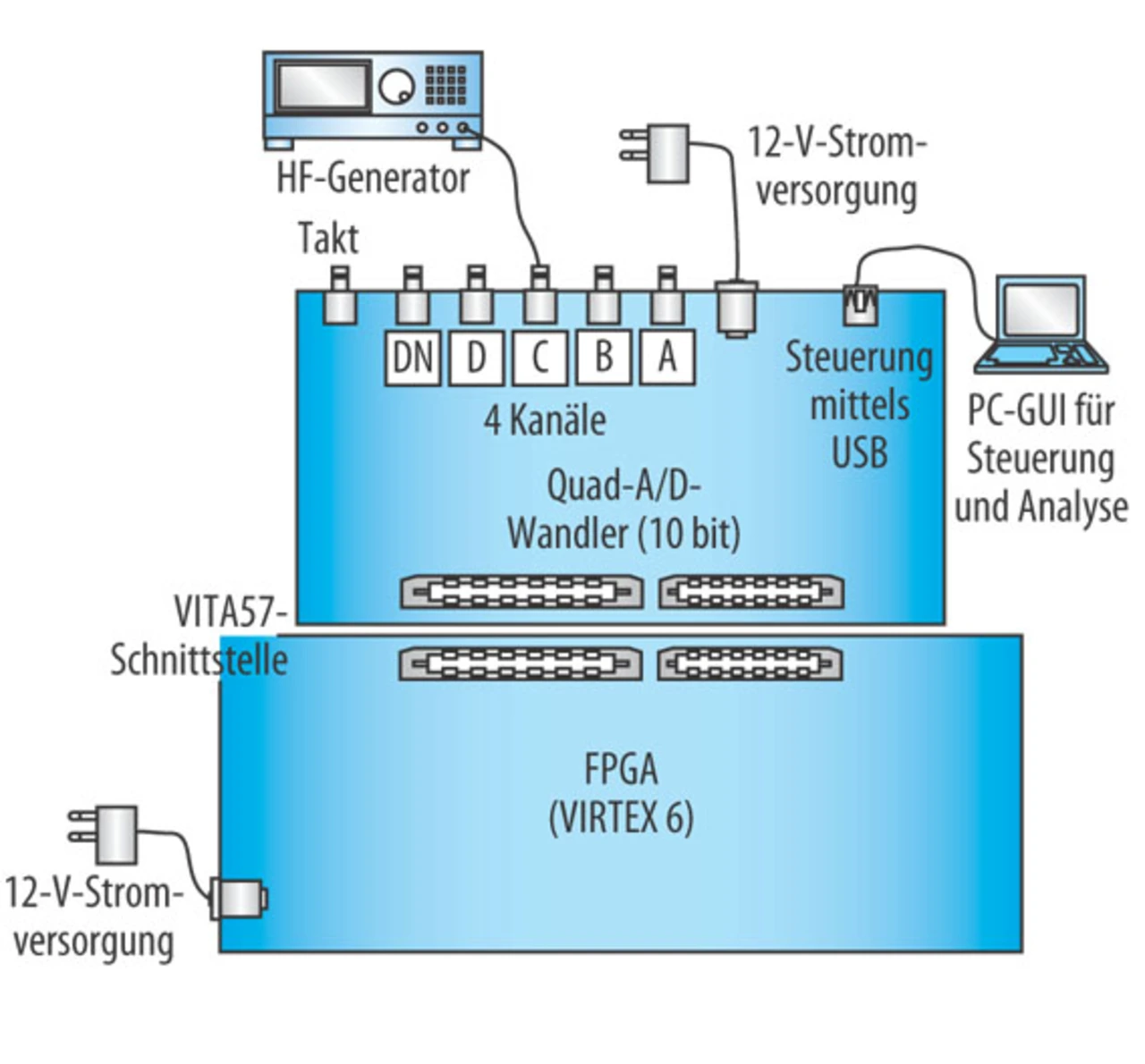

Der Standard VITA57 legt die Norm für I/O-Mezzanine-Module fest, die mit einem FPGA-Verarbeitungsmodul verbunden werden. Ziel ist dabei die Maximierung des Datendurchsatzes, die Senkung der Systemkosten und die Möglichkeit zur Verwendung eines weniger komplexen FPGA.

Der Standard nutzt eine Familie von Hochgeschwindigkeits-Steckverbindern für I/O-Mezzanine-Module. Diese stellen die Verbindung zum FPGA her und unterstützen Single-Ended- und differenzielle Datenraten bis zu 10 Gbit/s. Dank des flachen mechanischen Profils kann der Standard im Verbund mit populären Motherboard-Standards wie VME oder Compact-PCI eingesetzt werden.

Wenn er beim Design seines Demo-Boards diesen Standard zugrunde legt, hat der Endanwender somit die Auswahl unter einer ganzen Reihe von FPGA-Mezzanine-Cards verschiedener Hersteller [3], was eine zügige Evaluierung des Prototypsystems mit dem geforderten Verarbeitungs-Algorithmus gestattet.

Seinen Einstand gibt dieses flexible Konzept unter Verwendung der Quad-Hochgeschwindigkeitswandler EV8AQ160 Quad8 und EV8AQ190 Quad10. Diese enthalten jeweils 4 Cores mit einer maximalen Abtastrate von 1,25 GS/s. Durch internes Interleaving kann die Abtastrate auf zwei Kanäle mit jeweils 2,5 GS/s oder einen Kanal mit 5 GS/s angehoben werden.

Jobangebote+ passend zum Thema

Sämtliche Aspekte der Kalibrierung zwischen den Cores sind chip-intern durch Einstellmöglichkeiten für Verstärkung, Phase und Offset berücksichtigt. Durch die große Eingangsbandbreite von bis zu 3,5 GHz eröffnet sich ein weites Anwendungsfeld. Hervorzuheben ist dabei, dass sich die Bandbreite durch den Interleaved-Betrieb mehrerer Cores nicht reduziert. Bild 6 zeigt einen typischen Systemaufbau für das Quad8/Quad10-Demo-Kit.

Ein weiteres Thema für die Anwender von High-Speed-Wandlern ist die Komplexität der Peripherie-Bauelemente, die benötigt werden, damit der Wandler seine volle Leistung erreicht. Das Demo-Board enthält deshalb sämtliche Peripherie-Komponenten für ein eigenständiges System. Die PLL-Stufe wurde mit Blick auf das angestrebte Phasenrauschen ausgewählt, das sich bei bekannter Wandlerauflösung als Jitter angeben lässt. So setzt der 8-Bit-Wandler einen Gesamt-Taktjitter von 400 fs voraus, während der 10-bit-Wandler einen deutlich geringeren Jitter von 150 fs erfordert.

Die Eingänge bestimmter Kanäle wurden mit Verstärkern bestückt, die genau auf die Anforderungen der Wandler in Sachen Bandbreite, harmonische Verzerrungen und Rauschverhalten abgestimmt sind. Andere Kanäle sind dagegen mit einem breitbandigen Symmetrierglied versehen, und auch ein vom Anwender individuell konfigurierbarer Direkteingang steht zur Verfügung.

Notwendig zur Optimierung der Systemleistung sind ferner hochstabile und rauscharme Spannungsregler für die PLL-Stufe und die Verstärker. Die Leiterbahnen wurden in ihrer Länge und Impedanz sorgfältig aufeinander abgestimmt, um den zeitlichen Versatz zwischen den Bits auf ein Minimum zu reduzieren.

Die FPGA-Schnittstelle, die während der Design-Integration große Schwierigkeiten aufwerfen kann, ist bereits fertig ausgearbeitet. Die Referenz-Schnittstelle nutzt ein Xilinx ML605 Evaluation Board mit einem FPGA des Typs Virtex6. Eine Anpassung an Altera-Stratix-FPGAs ist geplant. Der A/D-Wandler gibt ein LVDS-Signal mit 1:1 oder 1:2 DMUX und Source-Sync-DDR-Signalisierung mit einer Datenrate von 1,25 Gbit/s aus. Um hierfür gerüstet zu sein, enthält das FPGA an jedem Eingang einen SerDes, wodurch sich die intern benötigte Taktfrequenz um den Faktor 8 verringert.

Literatur & Autor

[1] Standard für FMC: American National Standards Institute (ANSI) www.ansi.org

[2] Bore, F.; Bruel, S.; Wingender, M.: A 10bit 2.2Gsps ADC Operating over First and Second Nyquist Zones (http://www.armms.org/images/conference/f_cabanes_e2v_high_speed_adc_10b2_2g.pdf)

[3] Xilinx Demo-Board ML605: http://www.xilinx.com/products/boards-and-kits/EK-V6-ML605-G.htm

| Andrew Glascott-Jones |

|---|

| ist Applikationsingenieur im Geschäftsbereich High-Reliability-Semiconductors (HRS) bei e2v in Grenoble, Frankreich. Dort ist er zuständig für die Entwicklung von Demo-Kits, mit welchen e2v seine Kunden bei der Prototyp-Entwicklung unterstützt. Zudem ist er im Bereich Application-Support tätig. Er verfügt über 27 Jahre Erfahrung in der Entwicklung von elektronischen Systemen für die Präzisionsmesstechnik, die militärische Funkkommunikation sowie sichere Weitverkehrsnetzwerke, Röntgenverfahren und die Laser-Spektroskopie. |

andrew.glascott-jones@e2v.com

- Formel 1 der Datenwandlung

- Anwendungsgebiete

- Demo-Kits