Schaltplanentwurf

Fehler mit automatischer Verifikation eliminieren

Fortsetzung des Artikels von Teil 1

Vollständig automatisierte Schaltplanverifizierung

ECAD-Verifikationstools haben sich in der Vergangenheit auf die Layout- und Fertigungsaspekte des Entwurfs konzentriert, nicht auf den Schaltplan.

Jobangebote+ passend zum Thema

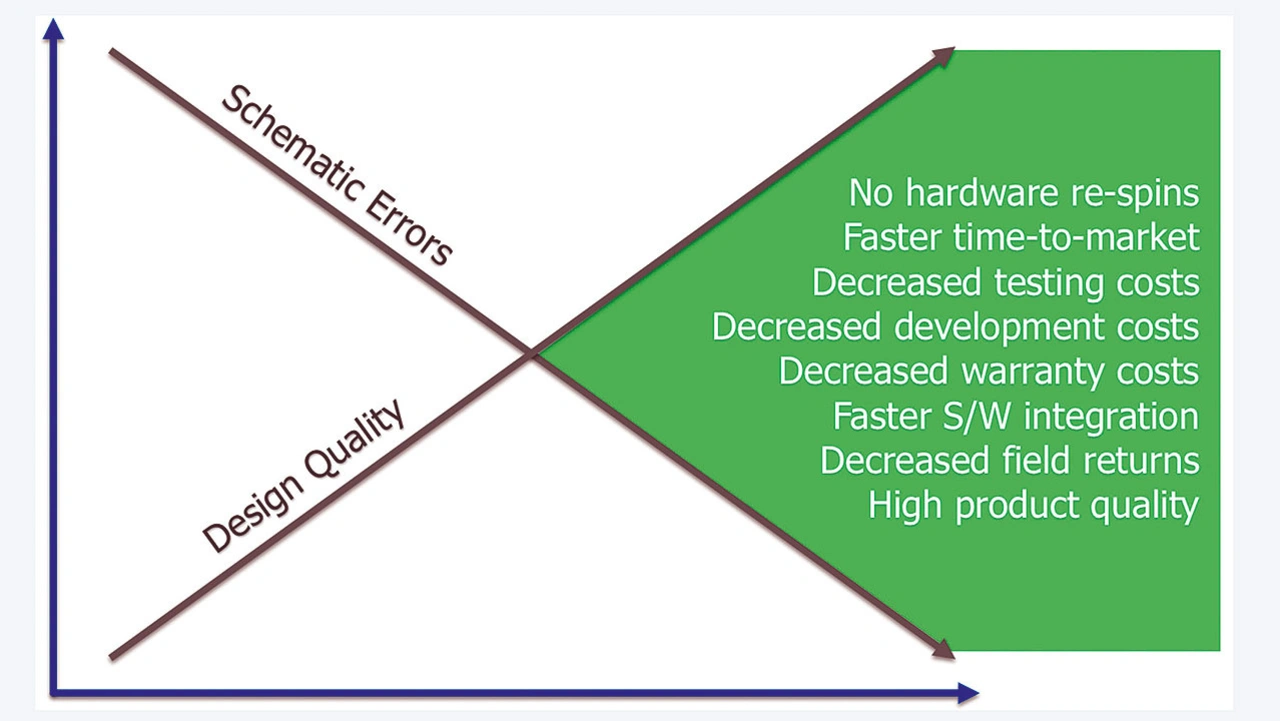

In Anbetracht der Tatsache, dass 78 % aller Projekte zwei oder mehr Wiederholungen erfahren und die Ursache für viele dieser Wiederholungen auf Fehler im Schaltplan zurückgeführt werden kann, ist die Zeit für eine vollautomatische Schaltplanverifizierung gekommen. Die Beseitigung von Schaltplanfehlern kann zu erheblichen Kosten- und Zeiteinsparungen führen, was eine frühe Markteinführung, eine bessere Produktqualität und ein geringeres Risiko zur Folge hat (Bild 3).

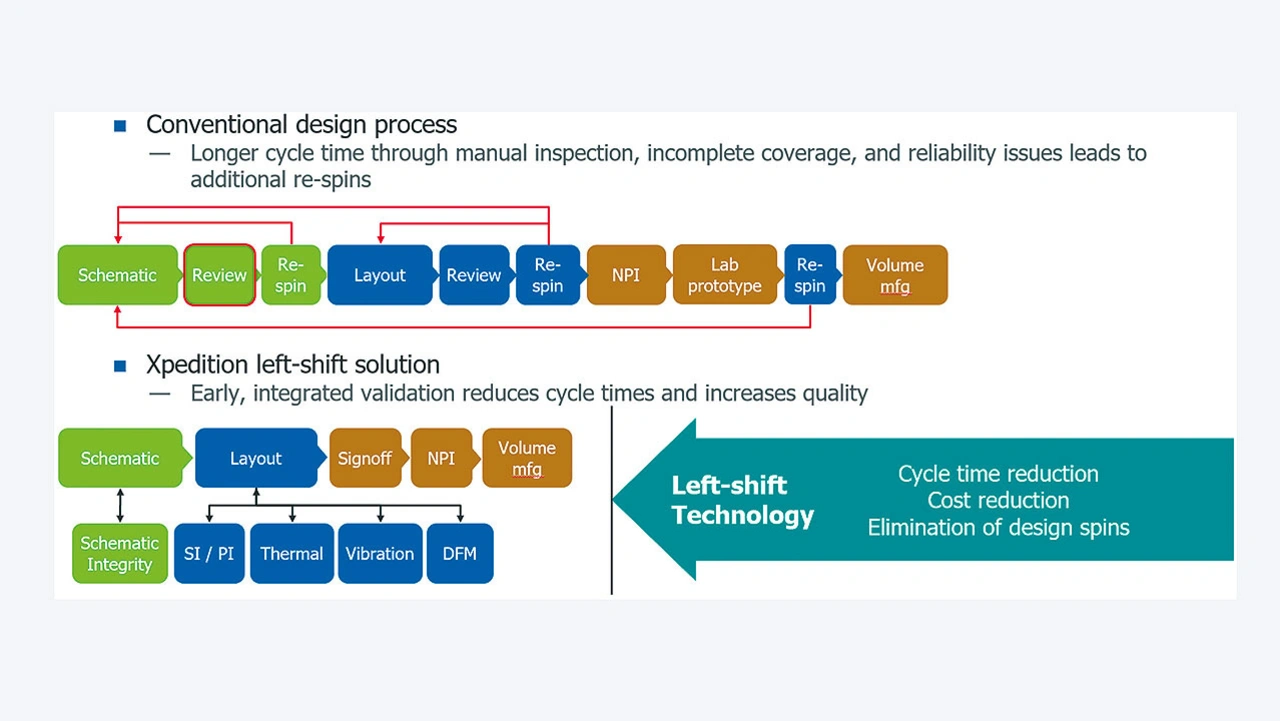

Durch die vollständige Automatisierung der Schaltplanverifizierung, die während der Schaltplanerfassung und nicht erst danach erfolgt, verschiebt sich der Entwicklungsprozess (Bild 4), was nachweisliche Vorteile mit sich bringt, wie z.B. reduzierte Zykluszeiten, geringere Kosten und die Eliminierung von Korrekturschleifen (Design spins).

Mit der Xpedition-Schaltplanintegritätsanalyse von Siemens EDA, einem Teil von Siemens Digital Industries Software, können Ingenieure alle Netze auf einem Schaltplan mithilfe vordefinierter Checks und einer umfangreichen Modell-Bauteilbibliothek vollständig überprüfen. Die Checks werden schnell und parallel zur Schaltplanerfassung ausgeführt, sodass das Layout mit maximaler Sicherheit starten kann, um auf Anhieb erfolgreich zu sein.

Die über 125 proprietären Schaltplanintegritätsprüfungen von Xpedition wurden entwickelt, um sowohl parametrische Fehler als auch schlechte Entwurfspraktiken zu identifizieren. Sie funktionieren mit allen wichtigen PCB-CAD-Programmen. Dieser Grad an automatisierter Schaltplananalyse kann Entwicklerteams Hunderte von Stunden an visueller Inspektion und Laborzeit sparen.

Die automatisierte Schaltplananalyse sollte eingesetzt werden, sobald der erste Schaltplan vollständig ist, damit jedes Bauteil und Netz vollständig analysiert werden kann. Dies kann geschehen, bevor das PCB-Layout entworfen wird. Im Verifizierungsbericht werden Schaltungsbereiche hervorgehoben, die während einer Entwurfsprüfung im Team diskutiert werden sollten.

Die Integration der Schaltplanintegritätsanalyse in Xpedition verkürzt die Zeit, die für die Überprüfung eines Schaltplans benötigt wird, und erleichtert Entwicklern gleichzeitig die Arbeit. Ein Analyseprojekt kann direkt aus dem Xpedition-Schaltplan heraus gestartet werden, Spannungen können vorausgefüllt werden, und Analyseergebnisse können sofort herangezoomt werden, ohne dass eine zusätzliche Suche nach dem Netz oder den Bauteilen erforderlich ist. Diese Funktionen reduzieren den Zeitaufwand für die Navigation in den Ergebnissen und das Sammeln von Projektdaten aus mehreren Quellen.

Zu den wichtigsten Merkmalen der Xpedition-Schaltplanintegritätsanalyse gehören:

- >125 eingebaute automatische Prüfungen.

- >6 Millionen Modelle.

- Unterstützung bei der Erstellung von benutzerdefinierten Modellen.

- Vollständige Prüfung von 100 % der Netze eines Schaltplans.

- Unterstützung für Multi-Modul-Verbindungsanalyse.

- Einfache Einrichtung und intuitive Bedienung.

- Nachbearbeitungsergebnisse und Berichte für Nachverfolgung und Audits.

- Arbeitet mit allen gängigen EDA-Tools.

- Keine zusätzliche Infrastruktur erforderlich.

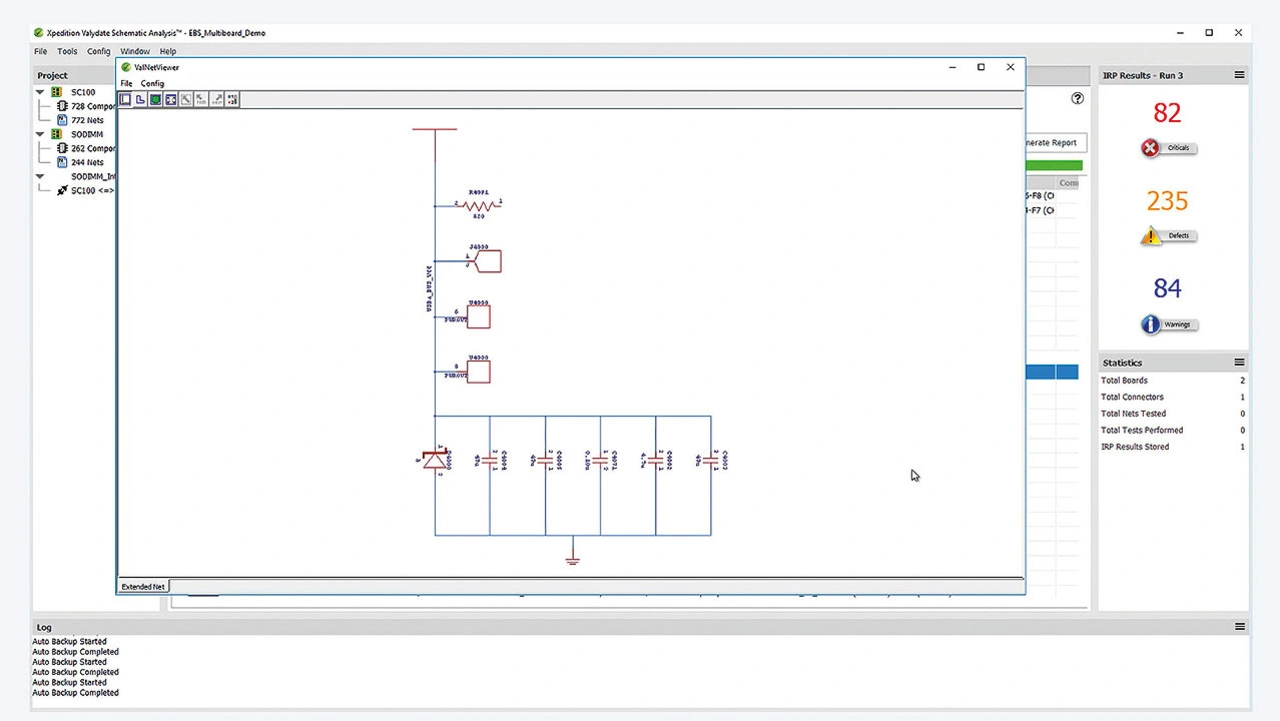

Im Durchschnitt führt die Xpedition-Schaltplanintegritätsanalyse 400.000 Prüfungen pro Schaltplan durch. Ein Beispiel für die Ergebnisse einer Xpedition-Schaltplanintegritätsanalyse eines Schaltplans ist in Bild 5 dargestellt.

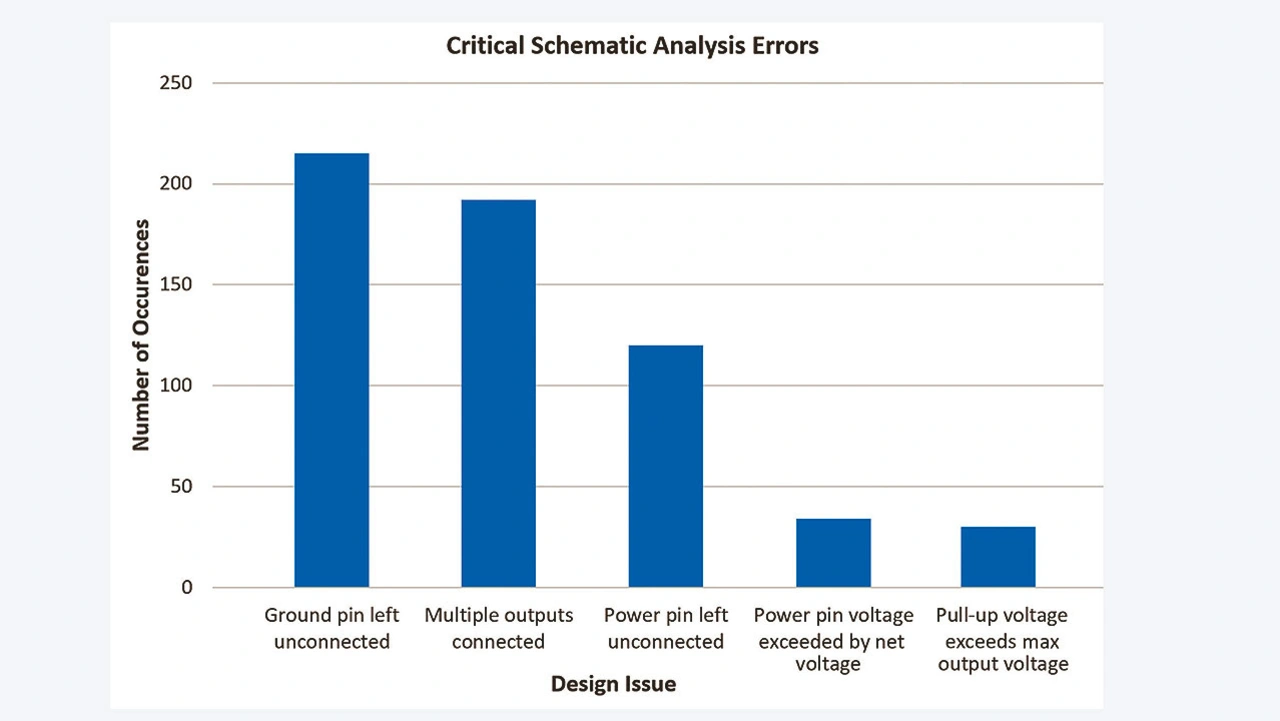

Vier Bereiche, in denen vermeidbare Fehler auftreten, sind Symbole und Bibliotheken, Netzverbindungen, Bauteilanforderungen und die Kommunikation zwischen Entwicklern. Die Xpedition-Schaltplanintegritätsanalyse kann bei jedem dieser Bereiche helfen. So gibt es beispielsweise viele Arten von Netzverbindungsproblemen, wie z.B. ein Stromversorgungs-Pin, der nicht mit der Stromversorgung verbunden ist (Bild 6), oder ein Eingang, dem ein Treiber fehlt.

Darüber hinaus werden die Anforderungen an die Bauteile in Schaltplananalysemodellen ausgedrückt, einschließlich Pull-up-/Pull-down-Anforderungen und Tipps, wie ein Pin behandelt werden soll, wenn er nicht benutzt wird. Verstöße gegen diese Regeln werden automatisch erkannt. Die Schaltplananalyse kann auch eine bessere Kommunikation zwischen den Entwicklern ermöglichen, da sie zusammenarbeiten müssen, um den Schaltplan zu verstehen und alle unklaren Details zu klären, was auch eine organisierte Dokumentation erfordern kann. Im Allgemeinen schafft diese Art der automatischen Prüfung die Voraussetzungen für eine gute Entwurfspraxis.

Aus Fehlern lernen und den Entwicklungsprozess optimieren

Eines der Hauptziele eines jeden Produktentwicklungsteams ist es, die Anzahl der Korrekturschleifen zu reduzieren, bevor ein Produkt auf den Markt gebracht wird. Da die Hauptursache für Korrekturen häufig Fehler im Schaltplan sind, kann ein Prozess, der eine vollautomatische Schaltplanverifizierung beinhaltet, die Häufigkeit dieses kostspieligen Problems erheblich reduzieren. Die Xpedition-Schaltplanintegritätsanalyse ermöglicht eine vollständige Prüfung aller Netze eines Schaltplans unter Verwendung vordefinierter Prüfungen und einer umfangreichen Modell-Bauteilbibliothek.

Die Xpedition-Schaltplanintegritätsanalyse

- automatisiert die Erkennung von kritischen Konstruktionsfehlern,

- eliminiert nachweislich 50 % bis 70 % der durch Schaltplanfehler und Marginalien verursachten Neukonstruktionen,

- bietet das Vertrauen und die Sicherheit, dass die Entwurfsabsicht gleich beim ersten Mal richtig umgesetzt wird,

- eliminiert viele Stunden manueller Überprüfung und reduziert das Risiko.

Neue Schaltungsentwürfe können modelliert und kontinuierlich analysiert werden, um sicherzustellen, dass Änderungen in letzter Minute vollständig bewertet werden. Daten von mehreren Leiterplattenentwürfen können auch integriert werden, um eine Validierung auf Systemebene durchzuführen. Darüber hinaus kann die Analyse der Schaltplanintegrität für Entwürfe auch nach der Marktfreigabe durchgeführt werden, um die Qualität der Elektronikentwicklung zu verbessern, die Ausbeute zu erhöhen und Produktrückgaben zu verringern.

Die Autorin

Nicole Kyle

arbeitet als Technical Marketing Engineer in der Electronic Board Systems Group bei Siemens EDA. Sie begann bei Mentor Graphics als Associate Rotation Engineer und arbeitet seit fünf Jahren mit Front-End-Design-Produkten im Xpedition Flow, wobei sie sich auf die Xpedition-Schaltplananalyse spezialisiert hat. Kyle ist Absolventin des Harvey Mudd College mit einem Bachelor of Science in Ingenieurwissenschaften.

- Fehler mit automatischer Verifikation eliminieren

- Vollständig automatisierte Schaltplanverifizierung