MathWorks-Tool

Automatisch zum FPGA-Code

Ein Zusatzmodul für Matlab/Simulink erzeugt FPGA-Code in den Hardware-Beschreibungssprachen VHDL oder Verilog für die Verarbeitung von Videos mit bis zu 8K-Auflösung und hohen Frame-Raten.

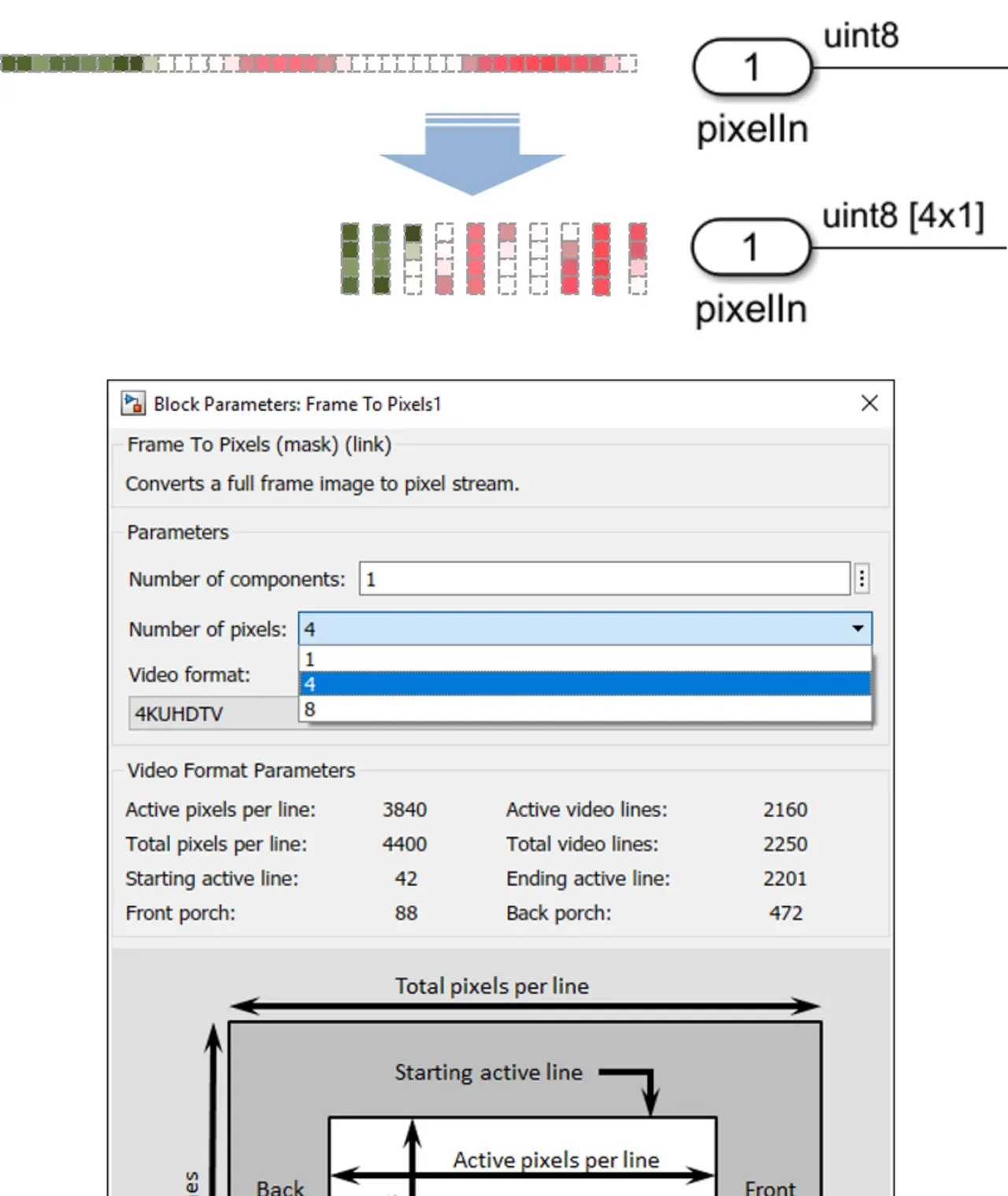

Die Produtfamilie Matlab/Simulink von MathWorks wird durch zahlreiche anwendungsspezifische »Toolboxen« ergänzt, die zur Erledigung bestimmter Aufgaben dienen. Eine davon ist die Vision-HDL-Toolbox, die sich zur Verarbeitung von Bilddatenströmen eignet und mithilfe des HDL Coders die Hardwarebeschreibung für FPGAs erzeugt. Die Toolbox stellt ein Entwicklungs-Framework bereit, das Bild- und Videodaten mit hoher Auflösung oder hoher Frame-Rate (HFR) verarbeiten kann. Mit dem Release 2019b ist eine Funktion zum Multipixel-Streaming hinzugekommen. Damit können Ingenieure, die in den Bereichen Video-/Bildverarbeitung oder FPGA-Design tätig sind, die Untersuchung und Simulation von Implementierungsalternativen beschleunigen, wenn sie 4K- oder 8K-Videos oder Videos mit Auflösungen bis 240 Frames pro Sekunde verarbeiten.

Jobangebote+ passend zum Thema

Videos mit hoher Auflösung und/oder hoher Frame-Rate werden beispielsweise bei industrieller Inspektion, medizinischer Bildgebung sowie im Bereich Aufklärung, Überwachung und Erkundung (ISR) eingesetzt. Wenn solche Videodatenströme mit FPGAs in Echtzeit verarbeitet werden, dann müssen Vorgaben für Durchsatz, Ressourcennutzung und Energieaufnahme eingehalten werden. Die Vision-HDL-Toolbox enthält Blöcke, die 4 oder 8 Pixel parallel verarbeiten können. Mit den Software-Werkzeugen lässt sich das Verhalten von Hardware für die Bildverarbeitung auf hohem Abstraktionsniveau untersuchen und simulieren.

Zu den Funktionen der Vision-HDL-Toolbox gehören typische Bildverarbeitungsalgorithem wie die Erkennung von Ecken und Kanten, die Anwendung von Filtern, die Erzeugung eines Histogramms oder die Erkennung einer »Region of Interest«. Durch Hinzufügen des HDL-Coders zum Design-Workflow lässt sich synthetisierbarer VHDL- oder Verilog-Code direkt aus den Modellen generieren. Die Algorithen der Toolbox erzeugen mithilfe des HDL-Coders lesbaren und hardware-unabhängigen Code. Der generierte HDL-Code ist auf FPGAs erprobt für Frame-Größen bis zu einer Auflösung von 8K und für HFR-Video. (jk)