Advertorial

Strahlungstolerante FPGAs für die Raumfahrt

Fortsetzung des Artikels von Teil 1

FPGA-Technologien im Vergleich

Es gibt vier Grundtypen von FPGAs:

FPGAs auf SRAM-Basis

SRAM-basierte FPGAs speichern die Konfigurationsdaten der Logikzellen im statischen Speicher. SRAM ist flüchtig und kann die Bausteinkonfiguration nicht ohne Stromzufuhr beibehalten. Daher müssen diese FPGAs beim Einschalten programmiert werden. SRAM-gestützte Technologie verbraucht tendenziell mehr Strom und ist empfindlicher gegenüber Strahlung.

FPGAs auf Flash-Basis

Reprogrammierbare Flash-basierte FPGAs nutzen Flash als primäre Ressource für den Konfigurationsspeicher. Flash-Technologie ist immun gegen SEU und eliminiert die Gefahr strahleninduzierter Störungen im Konfigurationsspeicher des FPGAs. Im Vergleich zu SRAM-basierten FPGAs verbrauchen RTG4 Flash-basierte FPGAs bis zu 50 Prozent weniger Energie. Die Flash-Technik vereinfacht das Design in mehrfacher Hinsicht, da kein externer Speicher, keine Redundanz und keine kontinuierliche Überwachung der Konfiguration nötig sind. Außerdem ist kein Kühlkörper erforderlich, was Größe und Gewicht der Designs reduziert und gleichzeitig den Stromverbrauch senkt – besonders wichtig, wenn ein elektronisches Modul mit Solarzellen betrieben wird.

SONOS-basierte FPGAs

Die Microchip RT PolarFire FPGAs zum Beispiel bieten Strahlungsperformance mit qualifizierten Strahlungsdaten, geringen Stromverbrauch, SEU-Konfigurationsimmunität und hoch zuverlässige Komponenten mit einem Pfad zur QML-V-Qualifizierung. Diese FPGAs wurden auf Basis einer nichtflüchtigen Silizium-Oxid-Nitrid-Oxid-Silizium (SONOS)-Technologie auf einem 28nm-Technologieknoten entwickelt. Anhand einer Messung der Signallaufzeit eines Inverters verglich man die Leistung von 28nm und früheren 65nm-Technologien. Tests belegten eine um den Faktor 2,5 höherer Leistungsfähigkeit der28nm-SONOS-Technologie im Vergleich zur 65nm-Flash-Technologie. FPGAs auf SONOS-Basis bieten zudem hervorragende Strahlungsperformance und SEU-Immunität und sind gleichzeitig eine stromsparende Lösung. Durch die Möglichkeit der QML-V-Qualifizierung eignen sich SONOS-basierte FPGAs bestens für Anwendungen, die eine Hochgeschwindigkeits-Signalverarbeitung erfordern.

Jobangebote+ passend zum Thema

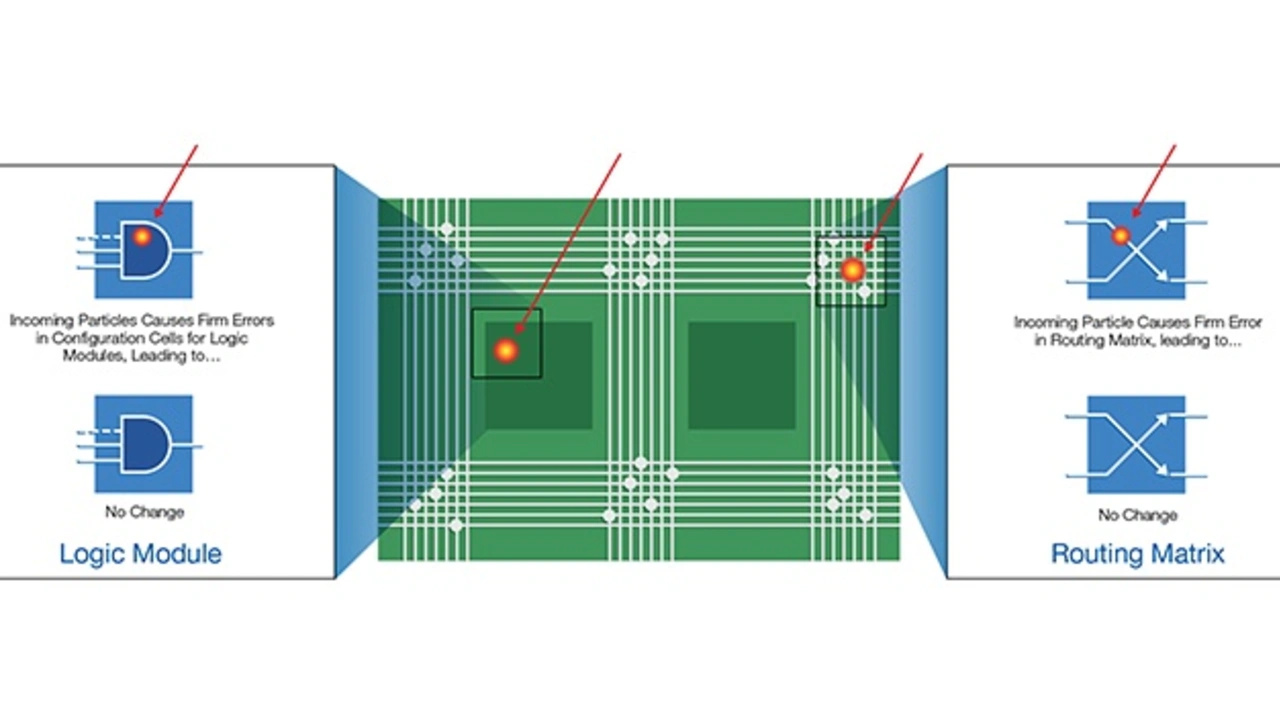

Abbildung 1 zeigt die Architektur von Flash- und SONOS-basierten FPGAs zur Sicherstellung der SEU-Immunität.

FPGAs auf Antifuse-Basis

Antifuse-basierte FPGAs werden nur einmal programmiert, was den entscheidenden Vorteil der Reprogrammierbarkeit im Vergleich zu Flash- und SONOS-basierten FPGAs einschränkt. Zunächst leiten Antifuses keinen Strom, werden aber durchgebrannt, um Strom zu leiten (das Antifuse-Verhalten ist das Gegenteil des Verhaltens einer Schmelzsicherung). Die Antifuse-Technologie ist sehr robust gegenüber Strahlungseffekten.

Vorgehensweise bei der Entwicklung von RT-FPGAs

Die Entwicklung von RT-FPGAs erfolgt auf Basis von Prozesstechnologien mit hervorragendem Strahlungs-TID-Verhalten. Sie sind oft RHBD-fähig und enthalten Flipflops mit integrierter TMR auf Schaltungsebene. TMR in Software, auch bekannt als Soft-TMR, lässt sich implementieren, wenn TMR nicht bereits auf Halbleiterebene implementiert wurde. Nach der Chip-Entwicklung durchlaufen RT-FPGAs eine strenge Qualifizierung.

Um den höchsten Qualifizierungsstandard zu erreichen, müssen die Bausteine die vom amerikanischen Verteidigungsministerium herausgegebene Norm MIL-PRF-38535 erfüllen, die einheitliche Qualifizierungs-, Test- und Zuverlässigkeitsstandards für Militär- und Raumfahrt-ICs festlegt. MIL-PRF-38535 definiert die Anforderungen für IC-Hersteller, die von der Defense Logistics Agency (DLA) in die QML-Liste aufgenommen werden wollen.

Ein weiterer Aspekt der Produktentwicklung ist die Charakterisierung der SEE-Performance, die sich bei gleichem Siliziumdesign zwischen den Waferlosen nicht ändert. Nach Einfrieren des Designs können FPGA-Hersteller mit dem SEE-Charakterisierungsprozess beginnen. Sobald der Baustein in die Produktion geht, sind keine weiteren SEE-Leistungstests erforderlich, solange das Design nicht geändert und die Komponente vollständig charakterisiert worden ist.

Bei einigen Prozesstechnologien kann sich das TID-Verhalten zwischen den einzelnen Wafern von Los zu Los unterscheiden. Daher müssen TID-Leistungstests in der Produktion auf der Basis von Wafer-Chargen durchgeführt werden, um sicherzustellen, dass ein Baustein seine Zielspezifikation für den TID-Wert (25 krad, 100 krad, 300k rad) erfüllt.

Einfluss von RT FPGAs auf das Design von Raumfahrzeugen

Die neuesten RT FPGAs bieten viele Vorteile zur Vereinfachung dieser Designs bei deutlich verbesserten Möglichkeiten für die Datenverarbeitung an Bord. Um diese Anforderungen zu erfüllen, wechselt man auf immer kleinere RT-FPGA-Technologieknoten, um eine höhere Leistung und eine schnellere Signalverarbeitung mit mehr Speicher- und DSP-Funktionen zu ermöglichen. RT-FPGAs bieten gegenüber ASICs darüber hinaus weitere wichtige Vorteile wie Reprogrammierbarkeit und kürzere Entwicklungszeiten. In der Regel programmiert man FPGAs nicht neu, sobald sie im Weltraum fliegen; dies ist aber bei komplizierteren Designs eine Option, solange Systementwickler die Richtlinien befolgen und die Erfolgsrate sowie die Risiken einer Reprogrammierung im Orbit sorgfältig abwägen.

Mehr Informationen finden Sie hier: https://bit.ly/388n7lm

- Strahlungstolerante FPGAs für die Raumfahrt

- FPGA-Technologien im Vergleich