Signalintegrität in Embedded-Anwendungen

Simulieren lohnt sich

Fortsetzung des Artikels von Teil 1

Vergleichssimulation und absolute Bewertung

Hat man erst einmal die Hürde eines abweichenden Stackups genommen, stellt sich die nächste Frage: Wie viel schlechter ist die Performance wirklich? Die einfachste Variante, das herauszufinden, ist eine Vergleichssimulation. Hierbei werden eine zum Design-Guide konforme Implementierung und die abgeänderte Variante simuliert. Sinnvollerweise erfolgt das als Pre-Layout-Simulation basierend auf der Schaltung und Topologie. Beispiele für solche Schematic-Simulatoren sind »ADS« von Agilent sowie »LineSim« und »HyperLynx« von Mentor Graphics. Die Änderungen betreffen üblicherweise nicht nur den Lagenaufbau. Ist beispielsweise aus Platzgründen ein geringerer Abstand der Leiterbahnen nötig, ist die Frage, wie lange die Leitungen noch sein dürfen, um die gleiche Performance zu erzielen, die ein Design entsprechend dem Design-Guide liefern würde.

Die Simulation eines Taktsignals (Clock Pattern, 0101…) oder einer kurzen Zufallsbitfolge und der visuelle Vergleich der transienten Spannungsverläufe reicht zum Vergleich nicht aus. In der Simulation muss der Entwickler die Kombination aus maximalem Nebensprechen und Inter-Symbol-Interferenz (ISI) berücksichtigen. Unter ISI versteht man die Beeinflussung der Signalintegrität eines Bits durch zuvor gesendete Daten. Beides addiert sich im System zum Jitter des Transmitters und ergibt ein gesamtes »Jitter Budget« der Übertragungsstrecke. Eine Simulation mit Variationen der Leitungslängen und -abständen ergibt eine zweidimensionale Matrix an Ergebnissen. Das Ergebnis der Simulation muss der Entwickler dann »nur« noch bewerten. Am einfachsten ist es, der Entwickler erstellt ein Augendiagramm und vergleicht Höhe und Weite des Datenauges. Diese Daten kann er zum Beispiel mit einer transienten Simulation eines PRBS-Musters (Pseudo Random Bit Stream) oder der Simulation einer Sprungantwort (Step Response) mit statistischer Auswertung erzeugen. Während die Simulation eines aussagekräftigen Pseudo-Zufallsmusters relativ lange dauert, ist ein Datenauge basierend auf einer Sprungantwort schnell erzeugt. Das Vermessen und Vergleichen der Augendiagramme zeigt die Performance relativ zur Implementierung nach dem Design-Guide. Unbekannt ist dann aber immer noch die absolute Performance des Designs. Funktioniert das Design beispielsweise nur bei 667 MBit/s, oder kann man es auch für 800 MBit/s verwenden? Möglicherweise ist zwar die Signalintegrität schlechter als in der Referenzimplementierung, aber für ein funktionierendes System kann es trotzdem ausreichen.

Jobangebote+ passend zum Thema

Die Bewertung der Daten erfordert eine genaue Kenntnis der Spezifikation der eingesetzten Komponenten. Wann beginnt der »Ringback« einer Reflektion wirklich kritisch zu werden? Wann addieren sich ISI und Nebensprechen so weit auf, dass sie das System zum Ausfall bringen können? Hierzu kann nur eine vollständige Worst-Case-Simulation eine Aussage liefern. Die kritischsten Parameter für Pattern, Nebensprechen, Chips und Platinenfertigung werden gemeinsam in eine Simulation gesteckt. In einer Timing-Budget-Berechnung werden dann noch Transmit-Jitter (tDQSQ, inhärenter Jitter des Treibers), Setup/Hold-Zeit (tSH) des Receivers und andere Fehlerquellen (Spannungsrauschen auf der Referenzspannung, Leitungslängenunterschiede, etc.) addiert. Das Ergebnis ist eine Pass/Fail-Bewertung über das simulierte System. Bei allen Einflussgrößen ist hierbei eine genaue Kenntnis der Spezifikation erforderlich. Bei DRAMs zum Beispiel ist die Auswertung der Ergebnisse zur Bestimmung der Setup/Hold-Zeiten nicht ganz trivial. Die vom Baustein benötigten Setup/Hold-Zeiten basieren auf unterschiedlichen Spannungspegeln in Abhängigkeit von Umschaltrichtung und Flankensteilheit (Derating).

Wo liegen die kritischen Punkte?

Das Ergebnis dieser Betrachtung zeigt auf, ob ein Design gerade noch so funktionieren wird oder ob es noch Einsparpotenzial bietet. Basierend auf diesen Ergebnissen kann der Entwickler sein Design nun auf Kosten oder Performance hin optimieren. Dazu sollte er die Probleme am besten einzeln betrachten. Das Datenauge gibt bereits einen Anhaltspunkt für die kritischen Punkte.

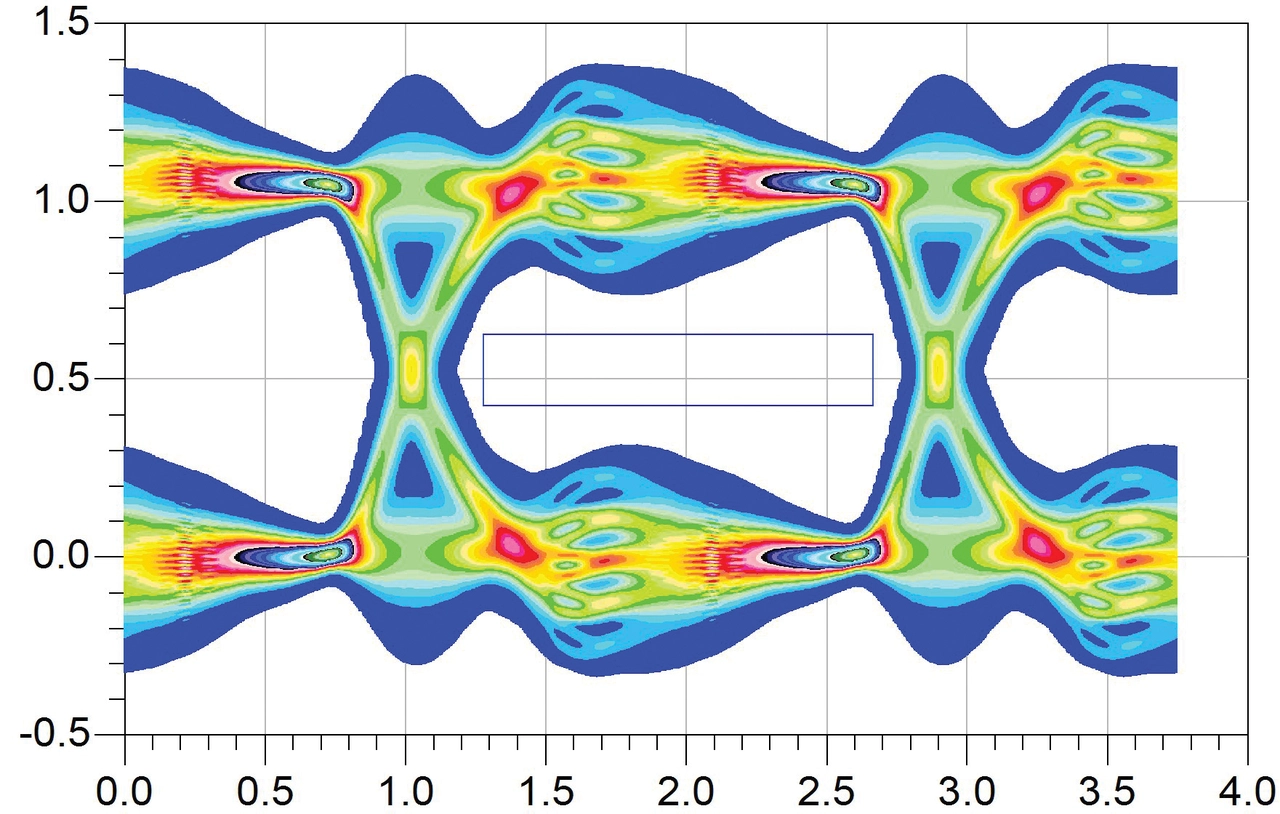

Bild 2 zeigt ein Datenauge einer nicht terminierten sourcesynchronen Punkt-zu-Punkt-Verbindung bei 533 MBit/s. In der Maske wurden Setup/Hold-Zeiten am Receiver und Transmit-Jitter bereits eingerechnet. Trotzdem reicht dies nicht für eine Pass/Fail-Entscheidung, denn es fehlt ein Timing-Budget mit Worst-Case-Parametern, die beispielsweise unterschiedliche Leitungslängen oder Jitter der zeitlichen Referenz (Strobe) mit berücksichtigt. Obwohl in dem Bild weder im Spannungs- noch im Zeitbereich die Maske verletzt wird, ist dieses System als kritisch zu betrachten. Speziell der Ringback in der Augenmitte wird auf Variationen der Simulationsparameter kritischer reagieren als der Timing-Jitter. Deshalb ist es sinnvoll, zuerst nach dem Grund für den Ringback zu suchen. Im Falle des Datenauges in Bild 2 ist ein signifikantes Nebensprechen am Nulldurchgang bei etwa 1,1 ns erkennbar. Die breite Histogrammverteilung der Spannungspegel in der Mitte des Datenauges (bei ca. 1,8 ns) könnte durch einen Überschwinger aufgrund des Schaltvorganges, einer Reflektion oder einem durch Crosstalk induzierten Schwinger erzeugt werden. Hier liegt der Vorteil der Simulation, dass eine einfache Simulation ohne Aggressoren leicht und zeitnah Klarheit verschafft: Die breite Verteilung des Original-Datenauges in Bild 2 ist durch Übersprechen verursacht.

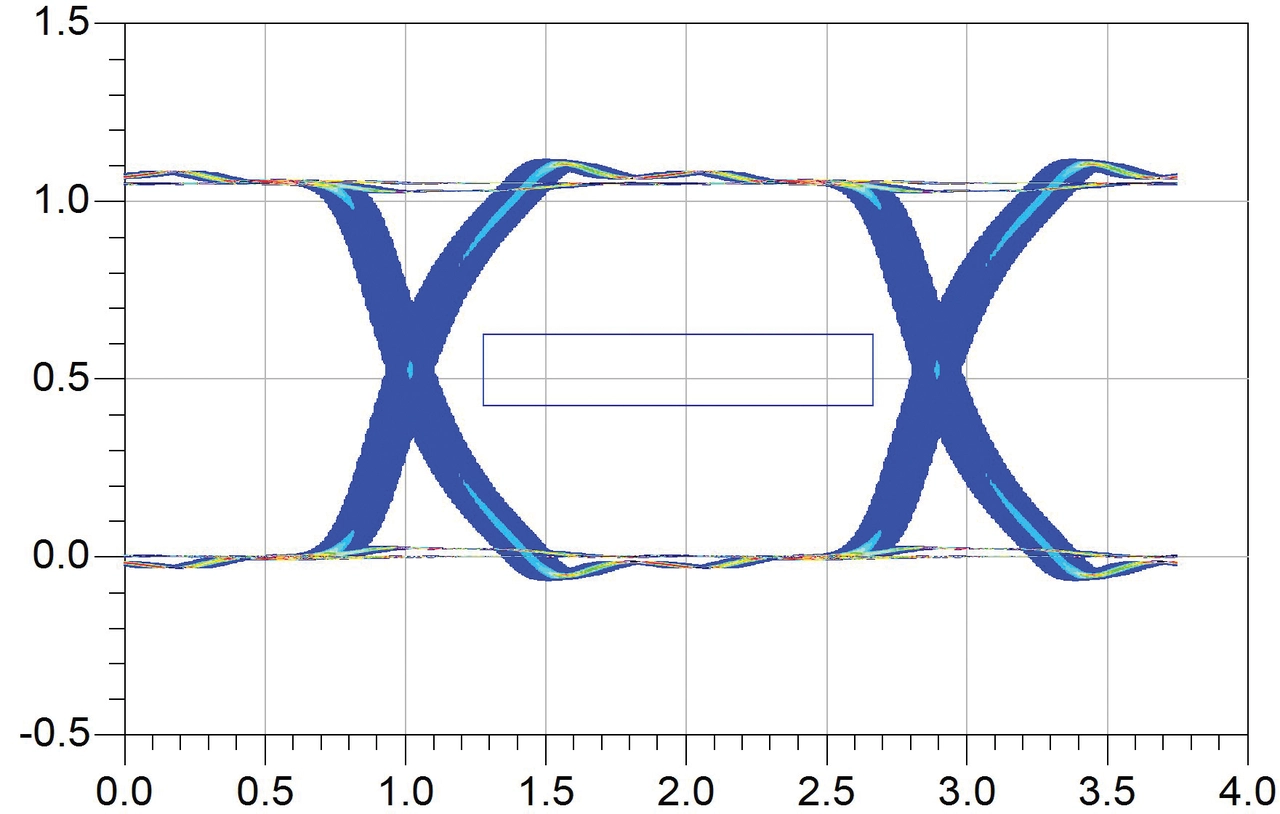

In Bild 3 ist zu erkennen, dass sich die Verteilung im Timing (Nulldurchgang bei 1,0 ns) nicht stark ändert, während die Über/Unterschwinger praktisch verschwunden sind. Beim Redesign des Boards hat der Entwickler speziell das Nebensprechverhalten verbessert.

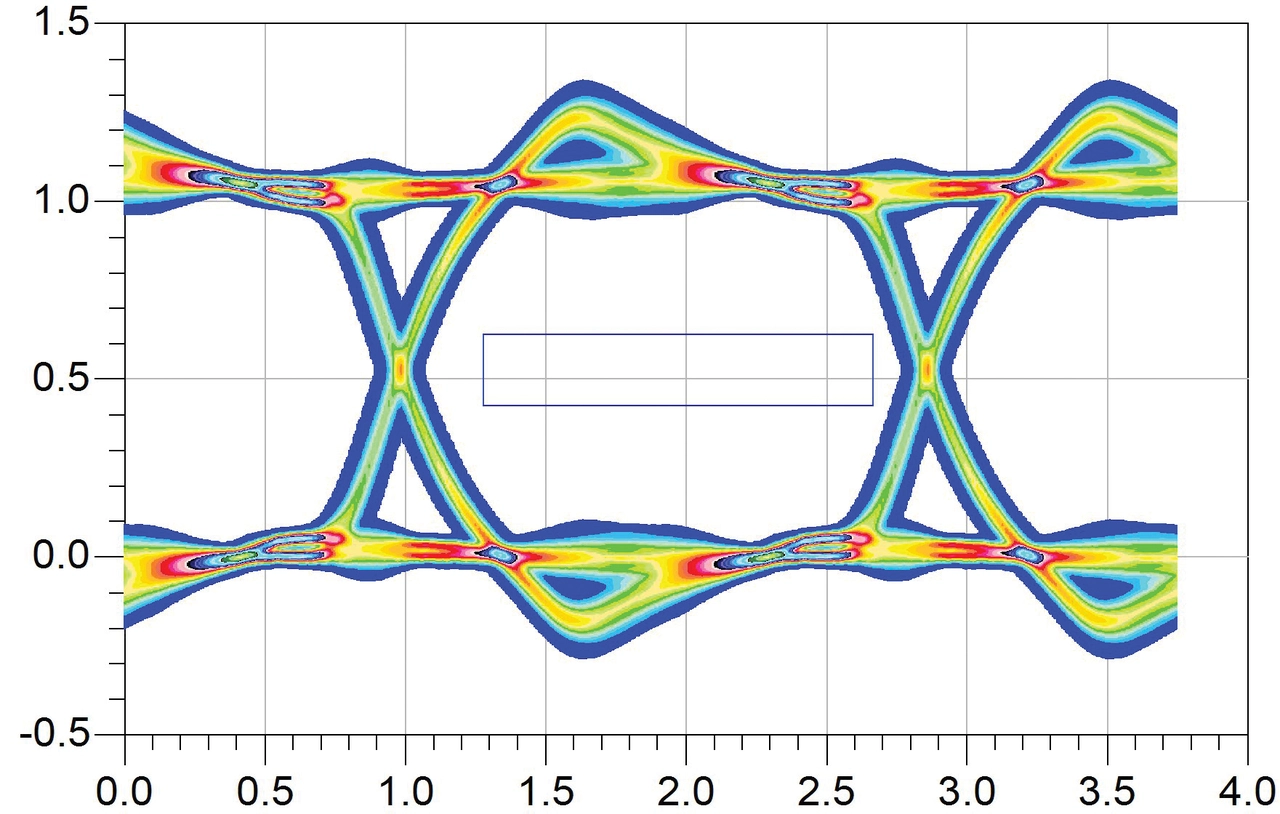

Das Simulationsergebnis in Bild 4 zeigt, dass er das Übersprechen beim Redesign fast komplett eliminieren konnte, gleichzeitig aber wurde der Überschwinger etwas größer. Ist wenig ISI im Auge erkennbar, kann der Entwickler alternativ bei der Terminierung den Rotstift anzusetzen. Ein DDR2-System mit nur vier oder acht DRAMs beispielsweise braucht nicht zwingend eine Terminierung auf dem Kommando-Adress-Bus (CA). Wieder bringt eine einfache Simulation Klarheit. Im Falle der CA-Terminierung liegt der Vorteil weniger in den paar eingesparten SMD-Bauteilen als viel mehr in der Fläche auf der Platine, die gewonnen wird, und in der verringerten Verlustleistung. Alle Einsparungen können sich durchaus zu einem interessanten Kostenvorteil aufaddieren.

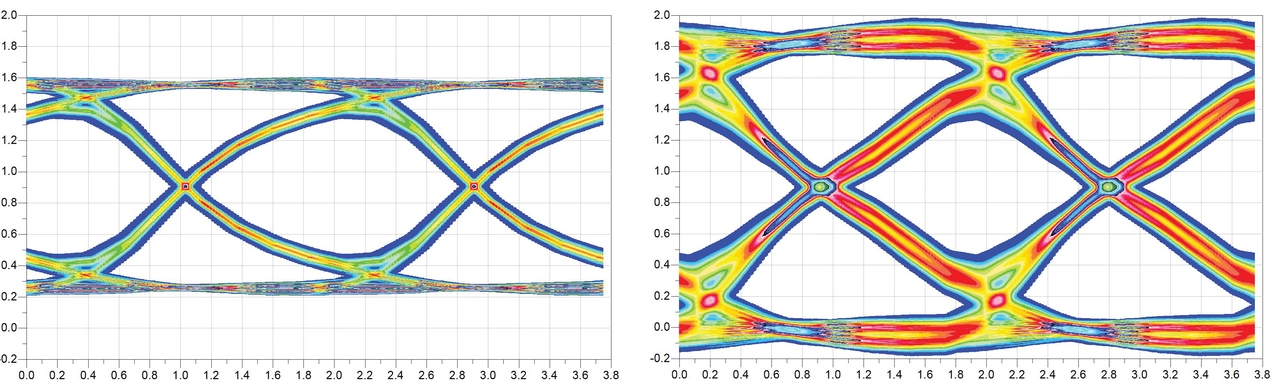

Im Vergleich zwischen einem terminierten und nicht terminierten DDR2-CA-Bus sehen die Datenaugen in Bild 5 sehr unterschiedlich aus. Das Datenauge des terminierten Systems sieht optisch deutlich besser aus. Bei einer genaueren Auswertung erkennt man allerdings, dass sich die Höhen der Augen praktisch nicht unterscheiden. Auch die Augenweite beim Kreuzungspunkt (Uref-Pegel) wird nur wenig verkleinert. Der Unterschied liegt in der Flankensteilheit und damit bei der Augenweite bei AC/DC-Pegeln. Eine Auswertung hier erfordert das Bestimmen der Flankensteilheit und das Derating der Setup/Hold-Zeiten, also die Setup/Hold-Zeiten in Abhängigkeit von der Flankensteilheit. Trotz dieser Verschlechterung kann auch die nicht terminierte Variante funktionieren.

Autor

Hermann Ruckenbauer ist Geschäftsführer von EKH - EyeKnowHow

Kontakt

EKH - EyeKnowHow

Telefon: 0 99 38/90 20 83

www.EyeKnowHow.de

»Warum simulieren? Das Design funktioniert doch!«

Bei dieser Argumentation werden einige Tatsachen übersehen: Fast jedes Design wird mit genügend Overhead funktionieren. Aber Produkte mit soviel Reserve (Margin, Marge), die auch ohne genauere Analyse sicher funktionieren, könnten auf Dauer nicht konkurrenzfähig sein. Ein Produkt nach einem Design-Guide zu entwickeln erfolgt in so genannten Low-Cost-Standorten meist schneller und billiger als bei uns in Europa. Mit diesem Geschäftsmodell könnte über kurz oder lang auch das Design nach Asien gehen. Hier gilt es, europäische Stärken im Engineering zum Vorteil einzusetzen und Produkte zu entwickeln, die günstiger zu fertigen sind und eine höhere Performance erreichen, weil die Margen eines Designs bekannt sind und das Produkt entsprechend optimiert ist. Noch ein anderer Punkt darf nicht übersehen werden: Auch wenn das Design nach Design-Guide heute noch funktioniert, könnte mit steigenden Frequenzen und immer kleiner werdenden Margins für ein solches Produkt schon bald ein Ende in Sicht kommen. Wer nicht heute den Grundstein legt und in den nächsten Jahren das Know-how aufbaut, um seine Designs auch simulieren zu können, könnte eventuell die nächste Krise nicht überstehen. Dabei darf man die Kosten für die Simulation aber nicht einem einzelnen Design anheften. Das gewonnene Wissen wird auch in weitere Designs einfließen, sodass die Produkte über die Zeit stetig besser werden. Aus diesem Grund ist eine designbegleitende Simulation nicht als kurzfristige Investition zu sehen. Die Aufwendungen könnten sich auszahlen, wenn das Know-how dauerhaft aufgebaut und umgesetzt wird.

- Simulieren lohnt sich

- Vergleichssimulation und absolute Bewertung