Leiterplatten

Von außen nach innen

Fortsetzung des Artikels von Teil 1

Einfach und trotzdem vielversprechend

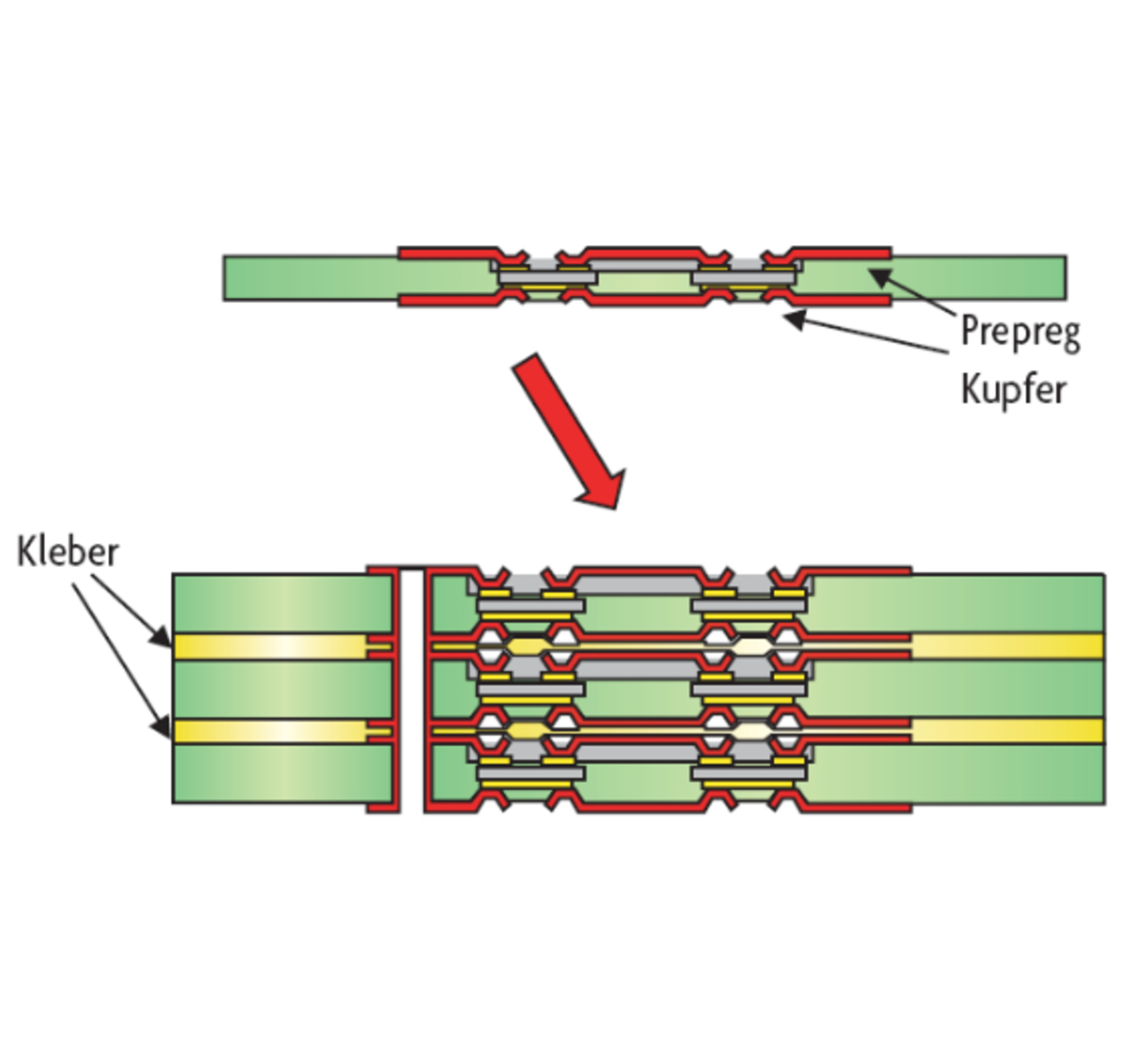

Auf der Suche nach einer preisgünstigen Variante für das Einbetten von Chips in Leiterplatten hat Würth Elektronik die „CHIP+“ genannte Technik entwickelt (Bild 1). Hier startet der Leiterplattenaufbau mit einer Kupferfolie. Im zweiten Schritt wird der Chip mit einem nicht leitfähigen Kleber, der zugleich als Dielektrikum dient, auf die Kupferfolie geklebt. Die Dicke des Dielektrikums lässt sich an die Anwendung anpassen – Schichtdicken kleiner 15 μm konnten bereits realisiert werden.

Danach wird die Kupferfolie mit den aufgeklebten Chips zu einem Multilayer verpresst. Neben den Standardmaterialien wie FR4 und Prepreg können hierbei auch Kombinationen mit Polyimid verwendet werden.

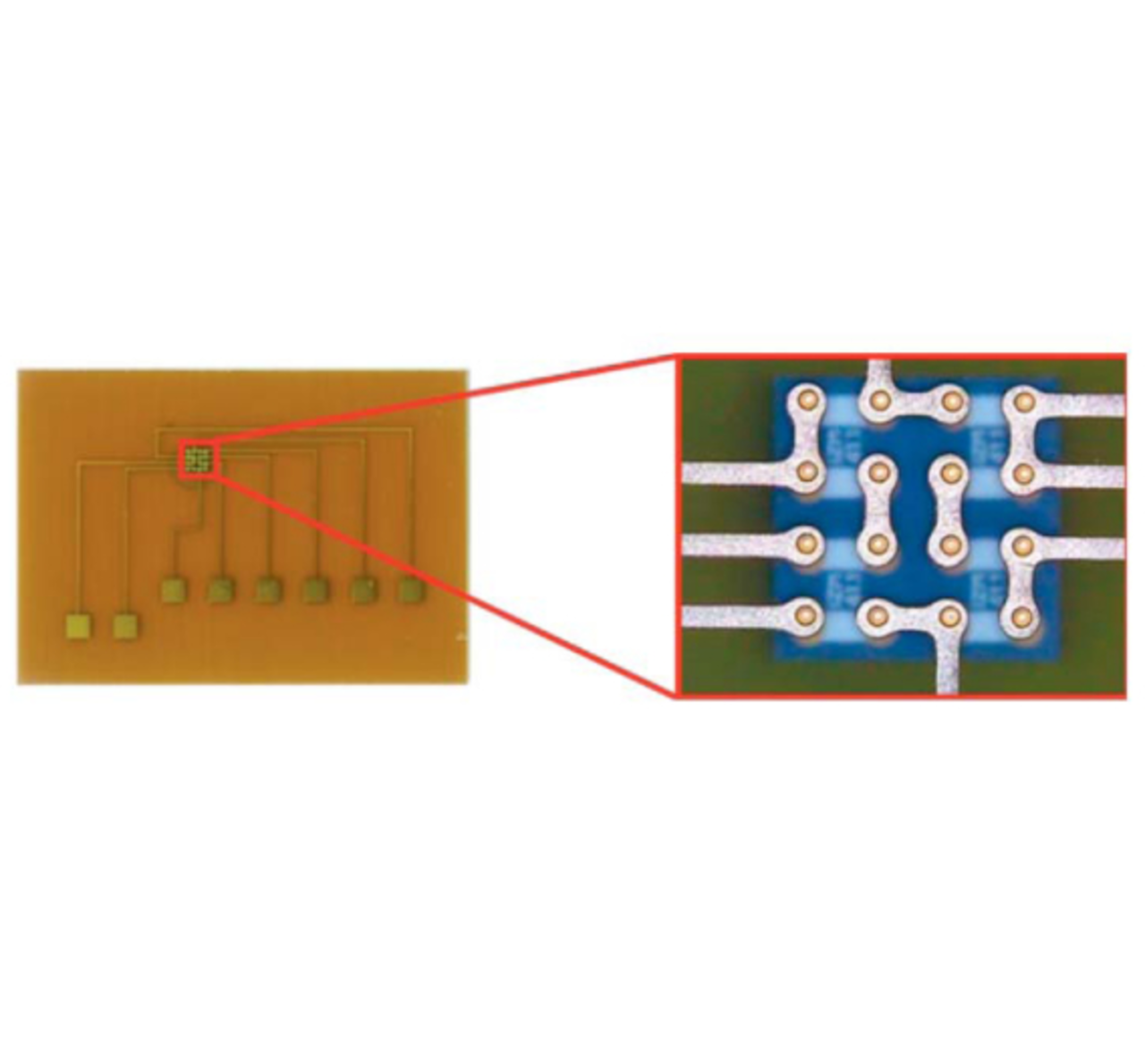

Danach folgen das Bohren der Microvias auf die Chip-Kontakte und die Ankontaktierung der Chips (Bild 2). Hierfür werden spezielle Pad-Oberflächen auf dem Chip benötigt. In umfangreichen Untersuchungen haben sich Nickel-Paladium und Kupfer als beste Oberflächenbeschichtung für die Chip-Kontakte in der Kupfergalvanik bewährt. Die Folgeprozesse entsprechen einer Standard-Leiterplattenfertigung mit Photolithographie und Ätzschritten.

Jobangebote+ passend zum Thema

Die „CHIP+“-Einbetttechnik ermöglicht einerseits einen unkomplizierten und kostengünstigen Fertigungsablauf und bietet andererseits die Möglichkeit, mit gedünnten Chips (≤50 μm) Leiterplattendicken unter 100 μm zu erreichen. Damit können Chips z.B. in fexible Substrate integriert, aber auch mehrere Chips übereinander gestapelt werden. Anwendungsfelder für diese Technik sind alle Bereiche, die nach Miniaturisierung streben. In aktuellen Forschungsprojekten wird insbesondere der Einsatz in der Medizintechnik verfolgt.

Im laufenden EU-Projekt TIPS [2] wird die Möglichkeit des Einsatzes der „CHIP+“-Technik in einem implantierbaren Defibrillator getestet. Für diesen Defibrillator sollen die FETs, die für den Hochstromimpuls verantwortlich sind, in die Leiterplatte eingebettet werden. Dafür sind sowohl eine beidseitige Kontaktierung der FETs als auch das Stapeln der FETs zu realisieren. Anforderungen, die zu einem echten 3D-Leiterplattenaufbau führen (Bild 3).

Sowohl für die „Lasercavity“- als auch für die „CHIP+“-Einbetttechnik wurden Lötschocktests, Temperaturwechseltests und Klimatests – Lagerung bei feuchter Wärme – durchgeführt. Dabei zeigten sich hinsichtlich der Zuverlässigkeit keine signifikanten Unterschiede zu konventionellen Baugruppen. Alle Tests wurden gut bestanden.

Die Temperaturwechseltests wurden unter den Bedingungen –40 °C bis +125 °C mit über 3500 Zyklen durchgeführt. Dabei traten bei den ersten 100 Zyklen einige Frühausfälle auf. Danach gab es bis zum Abbruch der Tests keine weiteren Ausfälle. Die Feuchte-Wärme-Auslagerung wurde bei 85 °C / 85 % über eine Zeitspanne bis zu 3500 h durchgeführt, wobei keine Ausfälle auftraten.

Bei den Lötschocktests wurden die Proben dreimal je 20 s in 260 °C heißes Lot getaucht. Auch hierbei waren keine Ausfälle festzustellen.

Der Autor:

| Dipl.-Ing. Frank Ebling |

|---|

| studierte nach seiner Ausbildung zum Augenoptiker und Augenoptikermeister Mikrosystemtechnik an der FHTW Berlin. Nach erfolgreichem Abschluss im Jahr 2000 war er an der TU Berlin und am Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration im Bereich optische Aufbau- und Verbindungstechnik mit Schwerpunkt Leiterplattentechnologie tätig. 2007 wechselte er zu Würth Elektronik in die zentrale Entwicklungsabteilung. Seine derzeitigen Arbeitsschwerpunkte sind Systemintegration und optische Techniken in der Leiterplatte. |

frank.ebling@we-online.de

Literatur:

[1] Schönholz, R.: Integriert statt aufgesetzt – aktive Bauteile in Innenlagen von Leiterplatten integrieren. Elektronik 2009, H. 22, S. 32ff

[2] Thin Interconnect Package Stacks (TIPS), www.tips-project.eu

- Von außen nach innen

- Einfach und trotzdem vielversprechend