HotChips 2019

ETH Zürich hebt Gleitkomma-Arithmetik auf neue Stufe

NTX heisst ein Hardware-Beschleuniger, den die ETH Zürich für Gleitkomma-Arithmetik entwickelt hat. Mit 260 Gflops/W bietet der in 22nm FD-SOI implementierte Chip eine unerreichte Energieeffizienz und schlägt jeden Konkurrenten um Längen.

Bei dem präsentierten Chip handelt es sich um das erste komplette Design, die Silizium-Implementierung und Messungen in 22-nm-FD-SOI des Network Training Accelerator (NTX) Architekturkonzepts. NTX basiert auf einer neu entwickelten partiellen Carry-Save "wide-inside" (300 bit) Multiplikator-Akkumulatoreinheit (FMAC), die die IEEE754-Konformität und einen um Faktor 1,7× niedrigeren Fehler bei Quadratwurzeloperationen als eine herkömmliche 32-bit-FPU bei Operatioen wie z.B. Faltungen gewährleistet.

Die vollständig pipelined FMAC-Einheit ist für einen konstanten Durchsatz bei allen gängigen Vektor- und Matrixoperationen ausgelegt. Zusätzliche Nicht-MAC-Operationen unterstützen das DNN-Training.

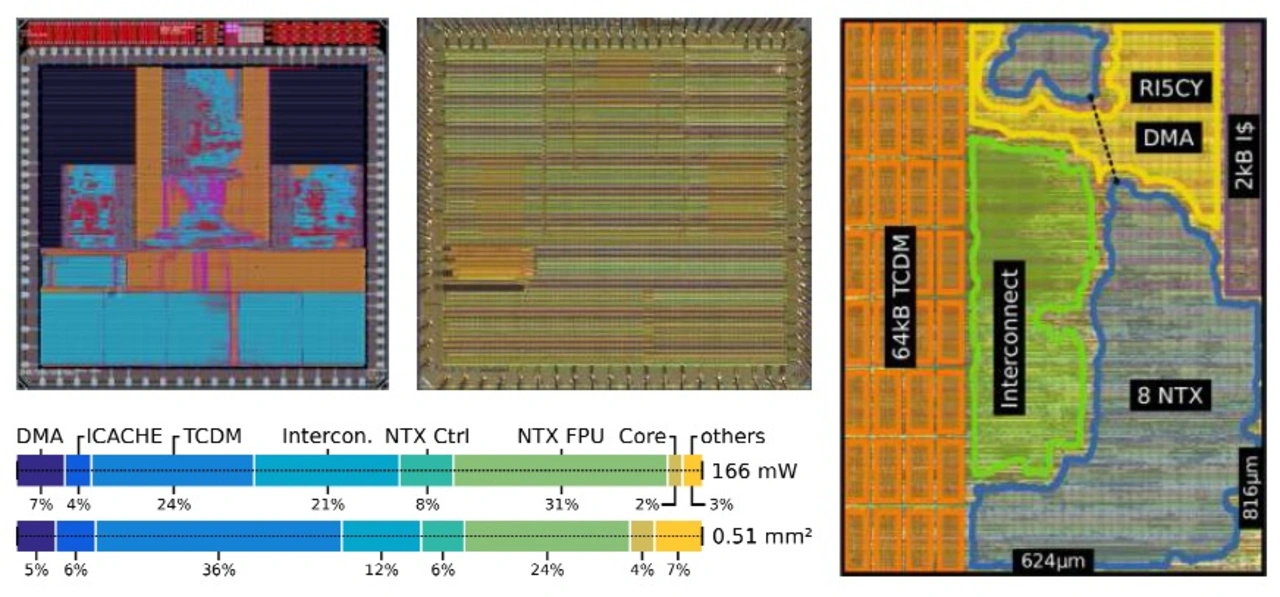

Bild 1 zeigt die Anordnung der Hauptblöcke des Designs. Es erreicht 1,25 GHz (SSG, 0,72 V, -40/125° C) und nimmt 0,51 mm2 Fläche ein. Drei Adressgeneratoreinheiten (AGUs) und fünf verschachtelte Hardware-Schleifen verarbeiten die gängigsten Adressmuster, die in derartigen Algorithmen vorkommen. Acht NTX-Einheiten werden von einem RV32IMC RISC-V-Core gesteuert, der eine volle Softwareflexibilität ermöglicht. Ein wesentliches Merkmal ist der Fokus auf die Beseitigung des bei von Neumann-Architekturen üblichen Engpasses durch die Amortisation von RISC-V-Instruktionen über acht NTX-Einheiten und die Entfernung aller FP-Lade-/Speicher-Vorgänge aus dem Befehlsstrom über die AGUs.

Die NTX-Einheiten und der RISC-V-Core sind mit einem 64 kB großen breitbandigen Tightly Coupled Data Memory TCDM verbunden, vergleichbar mit privatem Speicher und Registerdateien auf aktuellen GPUs (z.B. 48 kB im V100). Eine DMA-Engine wickelt den Datentransfer mit 5 GB/s im Hintergrund ab. Die doppelte Pufferung ermöglicht das Verstecken von Latenzzeiten und die vollständige Ausnutzung der Einheit für eine Vielzahl von Algorithmen, was energieeffizienter ist als herkömmliches Multi-Threading. Der RISC-V-Prozessor konfiguriert und orchestriert lediglich NTX- und DMA-Operationen und verarbeitet keine Datenübertragungen direkt, wodurch die Berechnung und der Datentransport aus der Pipeline herausgehalten wird. Es können somit 32 Flops, 16 lokale und 4 globale 32-Bit-Speicherzugriffe pro Taktzyklus erfolgen und das ohne die Flächen- und Energiekosten einer fortschrittlichen superskalaren oder Vektorarchitektur.

NTX erreicht sogar eine deutlich geringere Befehlsspeicherbandbreite als ein SIMT GPU-Streaming-Prozessor (bis zu 4×) dank der Entfernung expliziter Lade- und Speicheroperationen.

Jobangebote+ passend zum Thema

Der Cluster arbeitet zwischen 260 Gflops/W im Hocheffizienzbereich und 24 Gflop/s im Hochleistungsbereich. Die über Leckströme verlorene Leistung liegt zwischen 5,5 % und 24 % über 0,45 V bis 1,0 V. PVT-Schwankungen können durch bis zu 0,8 V Vorspannung kompensiert werden, was die Leistung um bis zu 1,6× erhöht.

Tabelle 1 zeigt einen Vergleich mit anderen Systemen. NTX übertrifft einen Tesla V100 um 2,1× in der Energieeffizienz und 2,3× in der Flächeneffizienz. Im Vergleich zu einem ARM Cortex- A53, einem 64-bit Rocket-RISC-V-Core und einem PULP-Cluster erreicht NTX eine 6,7×, 15,6× und 14,4× bessere Energieeffizienz und eine 5,4×, 3,2× und 6,4× bessere Flächeneffizienz. Im Vergleich zu einer 28-Core Dual-AVX-512 Intel Xeon 8180 CPU erreicht NTX eine 11,9× und 13,2× höhere Energie- und Flächeneffizienz.

NTX in der 22FDX-Technologie ist eine äußerst wettbewerbsfähige Architektur für FP-intensive Computeraufgaben mit bis zu 24 Gflop/s und 260 Gflop/sW. In gängigen Kerneln reduziert NTX die Befehlsbandbreite um 512× über Single-FMA und 64× über SIMD-Datenpfade. Seine Energie- und Flächeneffizienz übertrifft die heutigen RISC- und CISC-Prozessoren um bis zu Faktor 15,6 und 6,4 und sogar GPUs der Rechenzentrumsklasse um Faktor 2,1 bzw. 2,3.

Abbildung 1. Oben links und in der Mitte: Vollchip-Layout und Die-Shot aus hergestelltem Silizium in Globalfoundries 22FDX-Technologie. Richtig: Grundriss des NTX Accelerator Clusters, bestehend aus 1 RISC-V Prozessor und 8 NTX Gleitkommabeschleunigern. Unten links: Flächen- und Stromverbrauchsausfall des NTX-Clusters. Ein erheblicher Teil der Energie wird von den FPU- und Speicher-Subsystemen verbraucht, was zu einer hohen Energieeffizienz des Systems beiträgt.

Abbildung 3. Gemessene Rechenleistung und Energieeffizienz im Verhältnis zur Versorgungsspannung (links). Kompromiss aus gemessener Leistung und Effizienz (rechts).

Tabelle 1. Vergleich der wichtigsten Kennzahlen zwischen NTX und anderen Prozessoren. Leistung für 32-Bit Gleitkommaoperationen. Tesla V100 und Xeon 8180 basierend auf unseren eigenen Schätzungen, die wir auf verfügbaren Informationen und Würfelschüssen basieren. Energieeffizienz im Ist-Zustand, Flächeneffizienz normalisiert über Knoten.

| NTX | PULP | Arm Cortex-A53 | Rocket 64 bit | Tesla V100* | Intel XEON 8180* | |

|---|---|---|---|---|---|---|

| Node (nm)/Udd (V) | 22/0,45 | 40/0,8 | 16/0,8 | 40/0,65 | 12/1,0 | 14/0,9 |

| Energieeffizienz (Gflops/W) | 260 | 18 | 38,7 | 16,7 | 122 | 21,9 |

| Flächeneffizienz (Gflops/mm2) | 47,1 | 7,35 | 8,7 | 14,5 | 20,5 | 3,57 |

Tabelle 1. Vergleich zwischen NTX und anderen Prozessoren. Rechenleitung (Gflops) bei 32-bit-Gleitkommaoperationen gemessen. Die Flächeneffizienz wurde über die unterschiedlichen Fertigungs-Nodes normalisiert. *: Angaben basieren auf eigenen Schätzungen basierend auf öffentlich verfügbaren Angaben und Die-Shots.