Fantasiewerte für Powerpoint-Folien

Die Wahrheit über die abstrusen Nanometer-Zahlen

In der Chipfertigung sind wir mittlerweile bei 7 nm angelangt, zumindest wenn es nach den Marketing-Folien von Samsung, TSMC und Intel geht. Wie sich die Transistordichte jenseits von Powerpoint tatsächlich entwickelt hat, haben wir für Sie hier zusammengestellt.

32 nm, 28 nm, 20 nm, 16 nm, 14 nm, 12 nm, 10 nm und last but not least 7 nm mal mit und mal ohne FinFets oder FD-SOI: Mit vermeintlichen Strukturgrößen von Mikrochips bzw. deren Fertigung wird herumjongliert, wie es kein Akrobat im Zirkus besser könnte.

Die Annahme der Makrketingstrategen: Je kleiner die Zahl, desto höher werden die Kunden die Transistordichte und die Geometrien der Chipstrukturen annehmen.

Tatsächlich werden die Zahlen ja auch gerne ungeprüft in der Öffentlichkeit zitiert: 7 nm muss da schon mal “kleiner” sein als 10 nm, klingt doch logisch und 16 nm erst Recht kleiner als 20 nm.

Wir haben an dieser Stelle alle öffentlichen Quellen genutzt, um die tatsächlichen Geometrien der relevanten Parameter – Gate-Abstand (CPP, Contacted Poly Pitch), minimaler Interconnect-Abstand (MMP, Minimal Metal Pitch) und Fin-Abstand (FP, Fin Pitch) bei FinFET-Transistoren – zusammengestellt und damit die Dichte gemäß der üblichen Berechnungsmethode CPP x MMP (+ FP) berechnet. In der Tabelle haben wir diese nach steigender Dichte sortiert.

Jobangebote+ passend zum Thema

| Relative Fläche | Fertiger | Prozess | FinFET | CPP (nm) | MMP (nm) | FP (nm) |

|---|---|---|---|---|---|---|

| 1 | Intel | 32 | nein | 112,5 | 112,5 | - |

| 1 | Samsung | 32 LP | nein | 120 | 100 | - |

| 0,84 | TSMC | 28 | nein | 118 | 90 | - |

| 0,81 | Globalfoundries | 28 | nein | 114 | 90 | - |

| 0,806 | Samsung | 28 | nein | 113,4 | 90 | - |

| 0,77 | Intel | 22 FFL | ja | 108 | 90 | 45 |

| 0,57 | Intel | 22 | ja | 90 | 80 | 60 |

| 0,569 | Samsung | 20LPE | nein | 90 | 80 | - |

| 0,45 | TSMC | 20 | nein | 90 | 64 | - |

| 0,45 | TSMC | 16FF | ja | 90 | 64 | 48 |

| 0,43 | Common Platform* | 20 | nein | 86 | 64 | - |

| 0,4 | Samsung/Globalfoudries | 14LPP | ja | 78 | 64 | 48 |

| 0,29 | Intel | 14 | ja | 70 | 52 | 42 |

| 0,25 | Samsung | 10LPE | ja | 64 | 48 | 42 |

| 0,23 | TSMC | 10FF | ja | 66 | 44 | 36 |

| 0,225 | Samsung | 10LPP | ja | 64 | 44 | 36 |

| 0,18 | Globalfoundries | 7LP** | ja | 56 | 40 | 30 |

| 0,173 | TSMC | 7FF | ja | 54 | 40 | 30*** |

| 0,16 | Intel | 10 | ja | 54 | 36 | 34 |

| 0,156 | Samsung | 7EUV | ja | 54 | 36 | 27 |

Vergleich der Fertigungsgeometrien und Transistordichten unterschiedlicher Prozesse von Intel, TSMC, Samsung und Globalfoundries. Quelle: Hersteller, eigene Recherchen. *: Common Platform war eine Initiative von IBM, Gloablfoundries und Samsung zur Entwicklung gemeinsamer Chipfertigungs-Prozesse (bis 2014). **: Prozess wird nicht in Produktion gehen, da Globalfoundries im August 2018 entschied, die Entwicklung an allen Prozessen von 7 nm und darunter zu stoppen. ***: Schätzung der Elektronik auf Basis inoffizieller Informationen.

Das mystische Multi-Patterning

Einher mit den Nanometer-Zahlen wird meistens in mehr oder weniger Rätseln über die Wafer-Belichtung und hier über Immersions-Lithografie und EUV berichtet.

Konkret fehlen Angaben, wie komplex die Mehrfachbelichtung mit Immersions-Lithografie bei den kleinen Prozessgeometrien ist und wie die extrem-ultraviolette Strahlung (EUV) diese Komplexität aus der Chipfertigung rausnimmt.

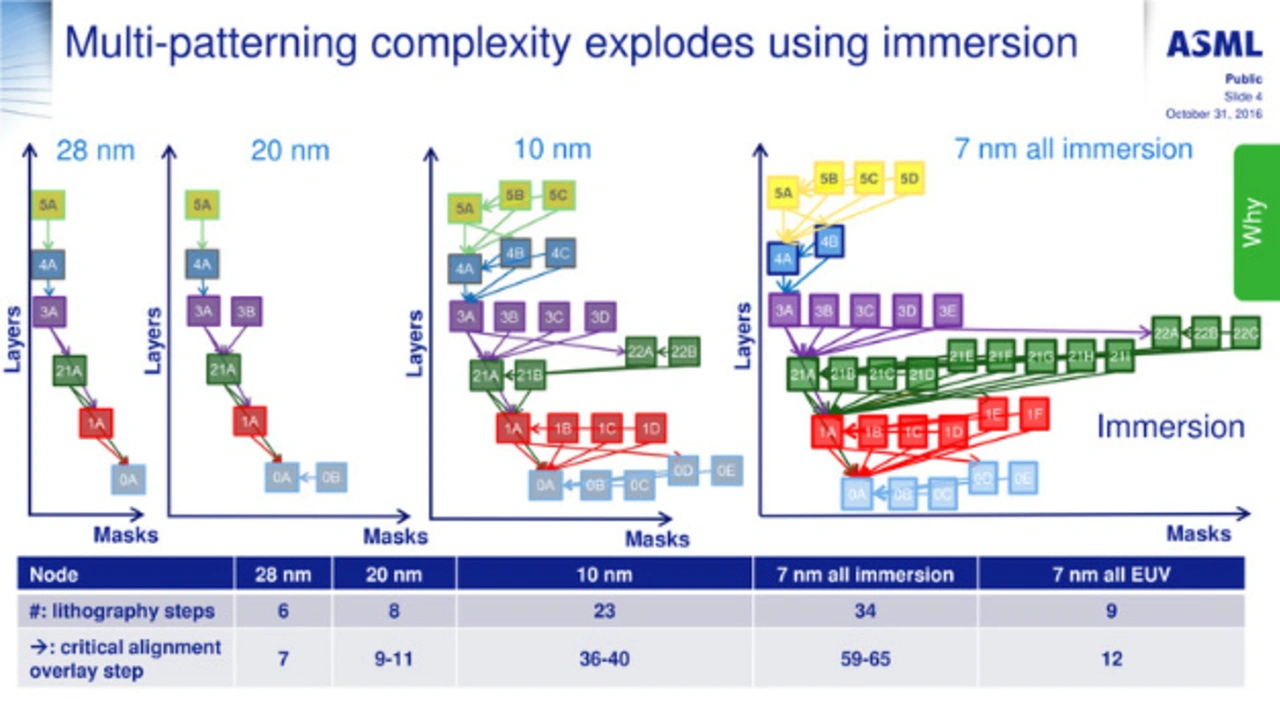

Auf Bild 1 zeigt die Entwicklung der Anzahl der notwendigen Masken, die Anzahl der Belichtungsschritte und der kritischen Ausrichtungen durch Überlagerungen ausgehend von einer 28- bis hin zur 7-nm-Fertigung ohne den Einsatz von EUV.

Die Anzahl der Belichtungsschritte stieg von 6 auf 34 Schritte an, einhergehend damit explodierte die Anzahl der Masken regelrecht zusammen mit einem Anstieg von Mehrfachbelichtungen und kritischen Ausrichtungen.

Für die Mehrfachbelichtungen werden unterschiedliche Verfahren (Double Patterning LELE – Litho-Etch-Litho-Etch, Triple Patterning LELELE – Litho-Etch-Litho-Etch, SADP – Self Aligned Double Patterning und SAQP – Self Aligned Quadruple Patterning) eingesetzt, die jeweils spezifische Vor- und Nachteile aufweisen.

Problematisch bei den ersten beiden Verfahren ist z.B. der auftretende Überlagerungsversatz zwischen den Strukturen bzw. Strukturteilen der unterschiedlichen Belichtungsschritte. Der Overlay-Versatz entsteht, da die zwischen den beiden Belichtungsschritten geänderten Komponenten des optischen Systems nie perfekt aufeinander ausgerichtet werden können (Beispielursachen: Maskenjustierung, Wafertopografie, Fokus, Belichtungsdosis, thermische Ausdehnung usw.).

Durch den Einsatz von EUV wird die Komplexität auf das Niveau einer 20-nm-Fertigung zurückgeführt.