Neue Funktionen und Profile erweitern den Anwendungsbereich von SERCOS interface

Echtzeit-Ethernet SERCOS III

Fortsetzung des Artikels von Teil 4

Master und Slave-Implementierungen

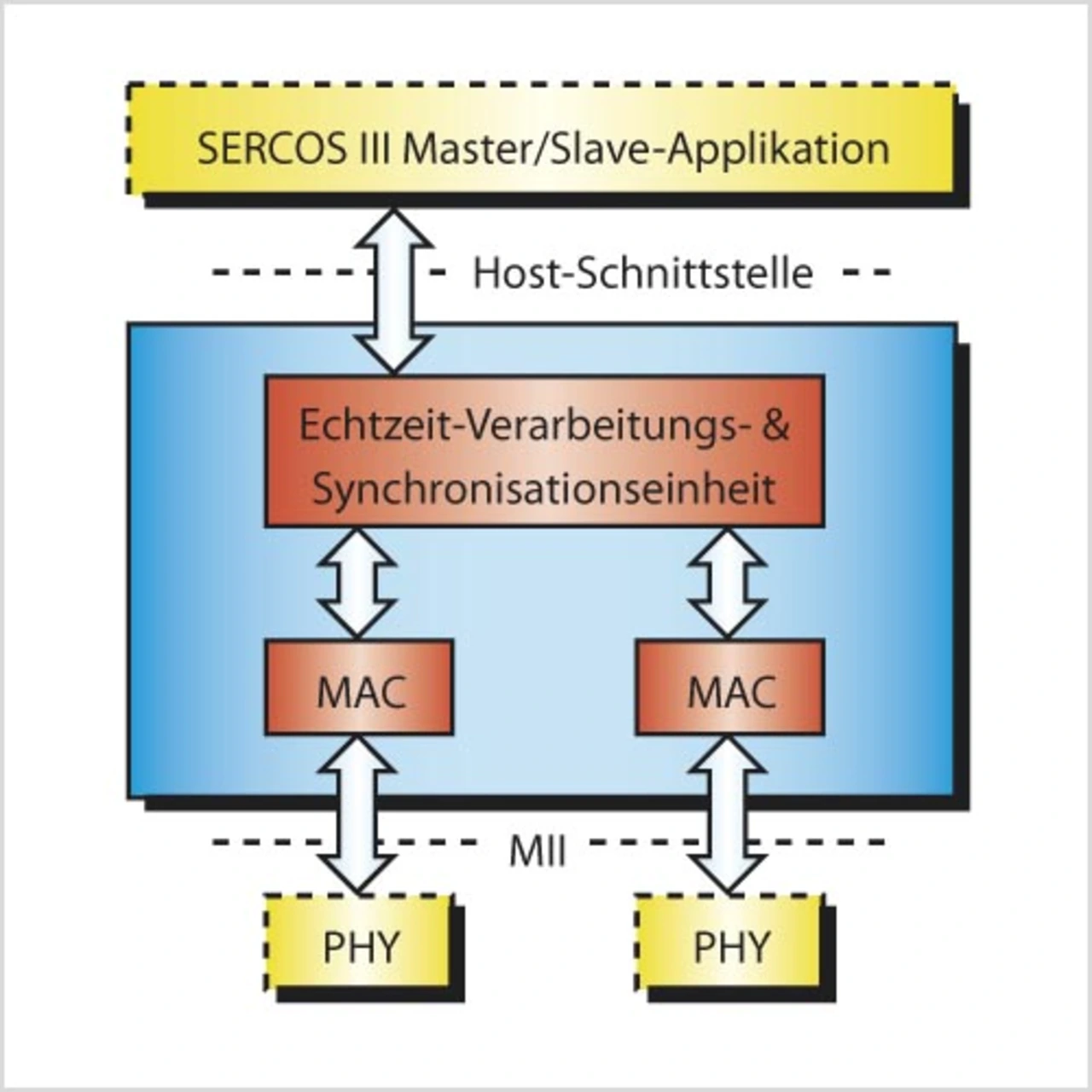

Die heute verfügbaren SERCOS-III-Produkte verwenden auf der Master- und der Slave-Seite eine spezifische SERCOS-III-Hardware (Bild 3). Diese übernimmt wichtige Funktionen, um die schnelle Verarbeitung der Echtzeit-Daten und die hardware-basierte Synchronisierung sicherzustellen. Damit wird die Host-CPU nicht mit Kommunikationsaufgaben belastet und es lässt sich auf diese Weise eine sehr robuste Implementierung realisieren, die zudem einfach getestet werden kann. Die Grundlage dafür ist die Entwicklung und Bereitstellung eines SERCOS-III-IP-Core, mit dem sich die SERCOS-III-Hardware in einen FPGA-Baustein integrieren lässt. Derzeit werden Bausteine der Firmen Xilinx (Spartan-3/3E) und Altera (Cyclone II/III) unterstützt. Daneben kooperiert die SERCOS-Nutzerorganisation mit Chip-Herstellern bzw. Systemhäusern, um die SERCOS-III-Hardware-Funktionen in universelle, multi-protokollfähige Kommunikations-Controller zu integrieren. Damit lassen sich Automatisierungsgeräte realisieren, die nur durch Umschaltung entsprechender Treiber-Software auf die verschiedenen Ethernet-Protokolle einstellbar sind. Der erste Multi-Protokoll-Chip für SERCOS III wird in verschiedenen Varianten von der Firma Hilscher angeboten (netX).

Für die Integration einer SERCOS-III-Schnittstelle in einfache SERCOS-III-Slave-Geräte mit einem geringstmöglichen Entwicklungs- und Integrationsaufwand steht für Low-cost-FPGAs ein lizenzfreier IP Core („Easy I/O“) zur Verfügung. Der Funktionsumfang des SERCOS-III-Slaves wurde dazu auf das Notwendigste reduziert, so dass nicht nur die Kommunikationsfunktionen, sondern auch der komplette SERCOS-III-Protokollstapel im Chip ablaufen kann. Der „Easy-I/O IP Core“ unterstützt ausschließlich den Echtzeit- und Servicekanal von SERCOS III. Pro Anschaltung können dabei bis zu 64 byte Master-Echtzeitund 64 byte Slave-Echtzeit-Daten verarbeitet werden. Zielanwendungen des Easy I/O sind unter anderem Drehgeber, Messtaster, Ventilinseln, 24-V-Digital-E/A, Analog-E/A sowie Sensorik zur Messdatenerfassung.

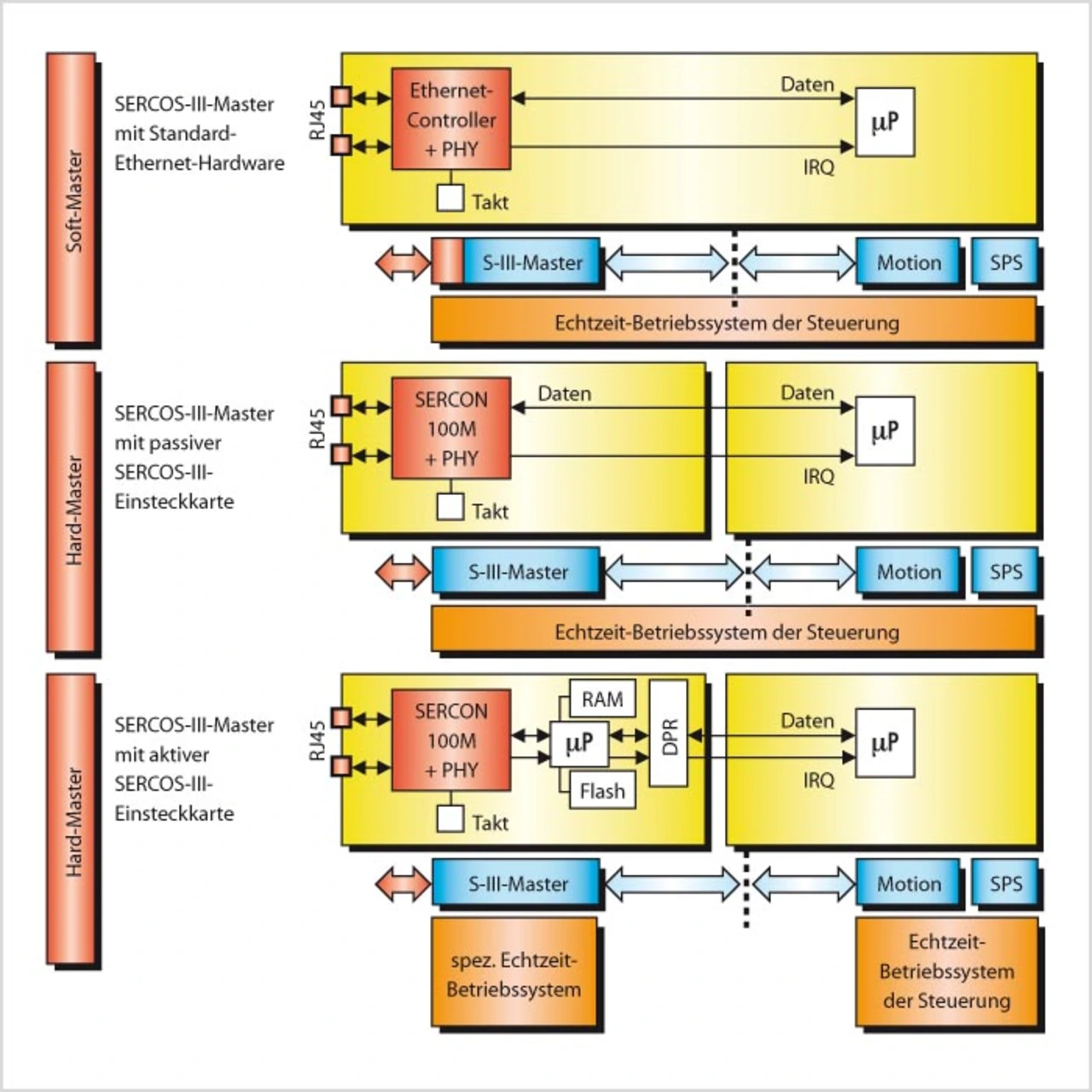

Beim Master kann auf eine spezifische Hardware verzichtet werden. An Stelle der SERCOS-III-Hardware werden dann Standard-Ethernet-Controller verwendet. SERCOS-spezifische Hardware-Funktionen werden dabei in den hardware-nahen und echtzeit-fähigen Teil des Master-Treibers verlagert, so dass die master-seitige Anschaltung komplett in Software realisiert werden kann (Bild 4). Diese Realisierung des Masters („SoftMaster“) ist etwa für PC-basierte Steuerungen interessant, die eine Ethernet-Schnittstelle „on board“ haben, so dass zusätzliche Hardware entfallen kann. Die erreichbare Synchronisierungsgenauigkeit des SERCOS-III-Echtzeit-Netzwerk-Verbundes hängt von der Leistungsfähigkeit der Hardware und der Charakteristik des Betriebssystems ab. Messungen mit handelsüblicher PC-Hardware und typischen Echtzeit-Betriebssystemen ergaben eine Synchronisationsgenauigkeit von 1 bis 3 μs und darunter. Damit können selbst anspruchsvolle „Motion Control“-Anwendungen realisiert werden.

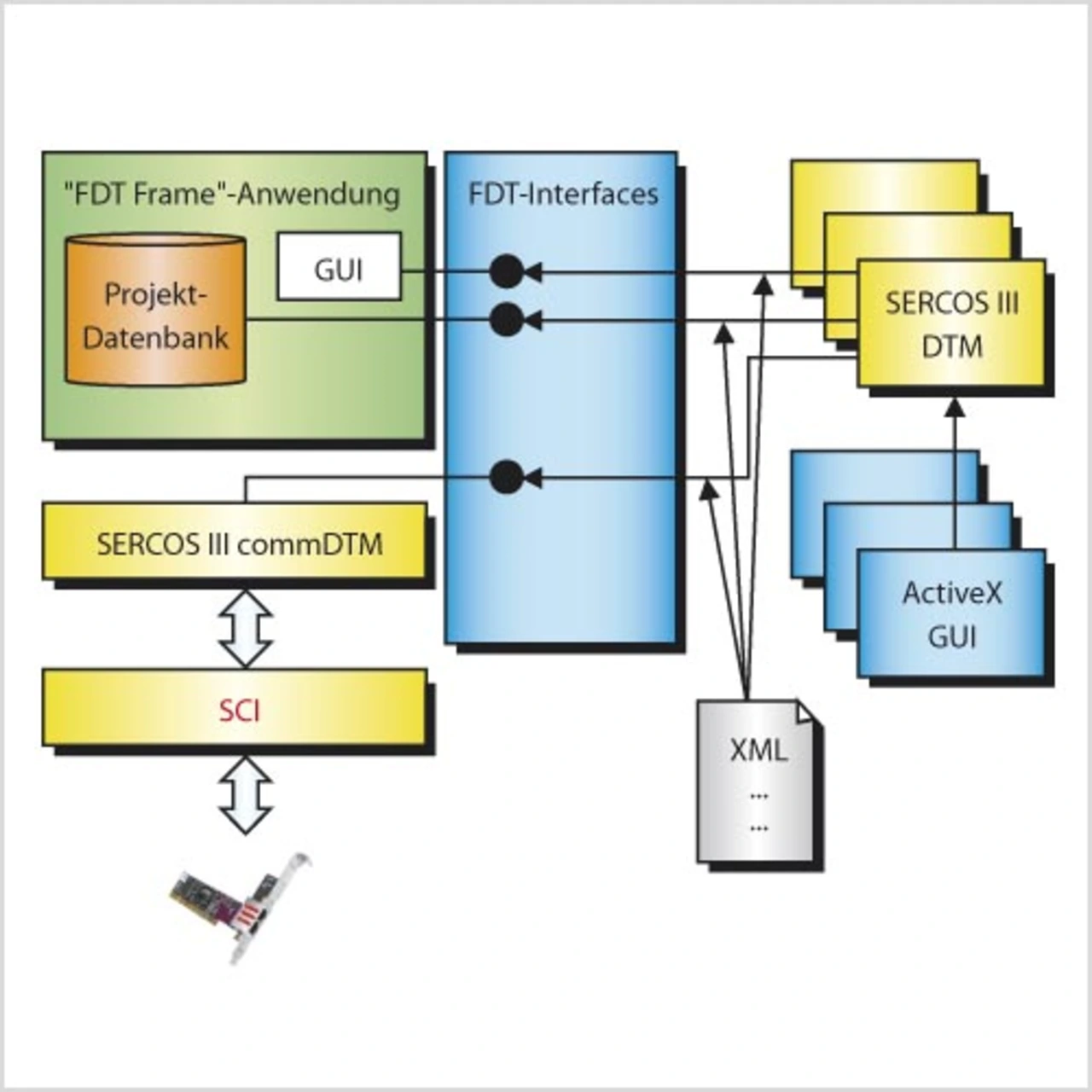

Auf der SPS/IPC/Drives 2008 haben die Nutzerorganisationen SERCOS International und die FDT-Organisation eine Kooperation zur Erweiterung der FDT-Spezifikation mit dem SERCOSIII-Protokoll bekanntgegeben. Mit der Erweiterung der FDT-Spezifikation um SERCOS III können SERCOS-III-Geräte mit Hilfe der DTM-Gerätetreiber konfiguriert werden.

Die DTM-Gerätetreiber ermöglichen die vollständige Gerätekonfiguration und -diagnose über grafische Bedienerdialoge. Die DTM-Anwendung bietet ein einheitliches Bedienfenster für Inbetriebnahme, Parametrierung und Diagnose der Feldgeräte.

Das Bild 5 veranschaulicht die Schnittstellen des FDT-Standards in Verbindung mit SERCOS-III-DTMs und dem SERCOS Configuration Interface (SCI), einer Standard-Schnittstelle für die Beschreibung von SERCOS-III-Netzwerk-Konfigurationen. Die FDT-Komponenten tauschen Informationen untereinander über XML-Dokumente aus, welche auf protokoll-spezifischen (in diesem Falle SERCOS III) FDT-XML-Schemata

- Echtzeit-Ethernet SERCOS III

- Echtzeit-Kommunikation bei kleinsten Zykluszeiten

- Einfache Installation

- Sicherheit inklusive – CIP Safety on SERCOS

- Master und Slave-Implementierungen

- Autor: Peter Lutz