Systemdesign / Echtzeitbenchmarks

Zeitanalyse komplexer eingebetteter Systeme

Fortsetzung des Artikels von Teil 3

Vorteile der Mikroarchitekturanalyse

Betrachten wir zwei Komponenten der Ausführungsplattform, die Caches und die Pipeline. Eine Komponente der Mikroarchitekturanalyse analysiert ein Programm daraufhin, welche Speicherblöcke an einem Programmpunkt auf jeden Fall im Cache sind, wann immer die Programmausführung diesen Punkt erreicht. Sie berechnet eine Unterapproximation der Menge der sicher im Cache befindlichen Speicherblöcke - wenn an einem Programmpunkt auf einen Speicherblock a zugegriffen wird und die Cacheanalyse berechnet hat, dass a garantiert im Cache ist.

Dann kann die Zeitanalyse sicher annehmen, dass dieser Zugriff nur einen Cachezugriff kostet. Wenn die Cacheanalyse nicht herauskriegt, dass a garantiert im Cache ist, dann muss im Prinzip mit beiden Fällen, einem Cache-Hit und einem Cache-Miss gerechnet werden.

In diesem Fall reicht es nicht nur den teureren Fall, den Cache-Miss, zu betrachten. Moderne Prozessoren haben sogenannte Zeitanomalien. Dies bedeutet, dass eine Ausführung, welche mit einem langsamen Schritt, etwa einem Cache-Miss, anfängt, insgesamt teurer werden kann. Dies ist z.B. dann der Fall, wenn der Cache-Miss eine Fehlspekulation bei einem bedingten Sprung verhindert. Die Existenz von Zeitanomalien erzwingt eine vollständige Durchmusterung des Raums der Pfade durch die Architektur. Dies verursacht den größten Aufwand bei der Zeitanalyse.

Die Befehlspipeline eines Prozessors ist in der Lage, mehrere aufeinander folgende Befehle in einer überlappenden Weise parallel zueinander auszuführen und damit die Programmausführung zu beschleunigen. Die größte Beschleunigung ergibt sich bei einer perfekt gefüllten Pipeline. Allerdings gibt es eine Reihe von Gründen, weshalb die Pipeline eventuell nicht perfekt gefüllt ist: Ein Befehl verursacht beim Laden aus dem Speicher einen Cache-Miss, oder ein Befehl kann nicht die arithmetische Einheit zur Ausführung seiner Operation erhalten, weil alle von vorangehenden Befehle belegt sind; oder ein Befehl kann seine Operation nicht ausführen, weil ein Operand noch nicht von einem vorangehenden Befehl berechnet worden ist. In all diesen Fällen muss die Pipeline für einige Zyklen anhalten.

Jobangebote+ passend zum Thema

Die Mikroarchitekturanalyse versucht, möglichst viele von diesen Gründen auszuschließen und damit die Zahl der Wartezyklen zu begrenzen, die auf die Ausführungszeit der Befehle addiert werden müssen.

Werkzeuge

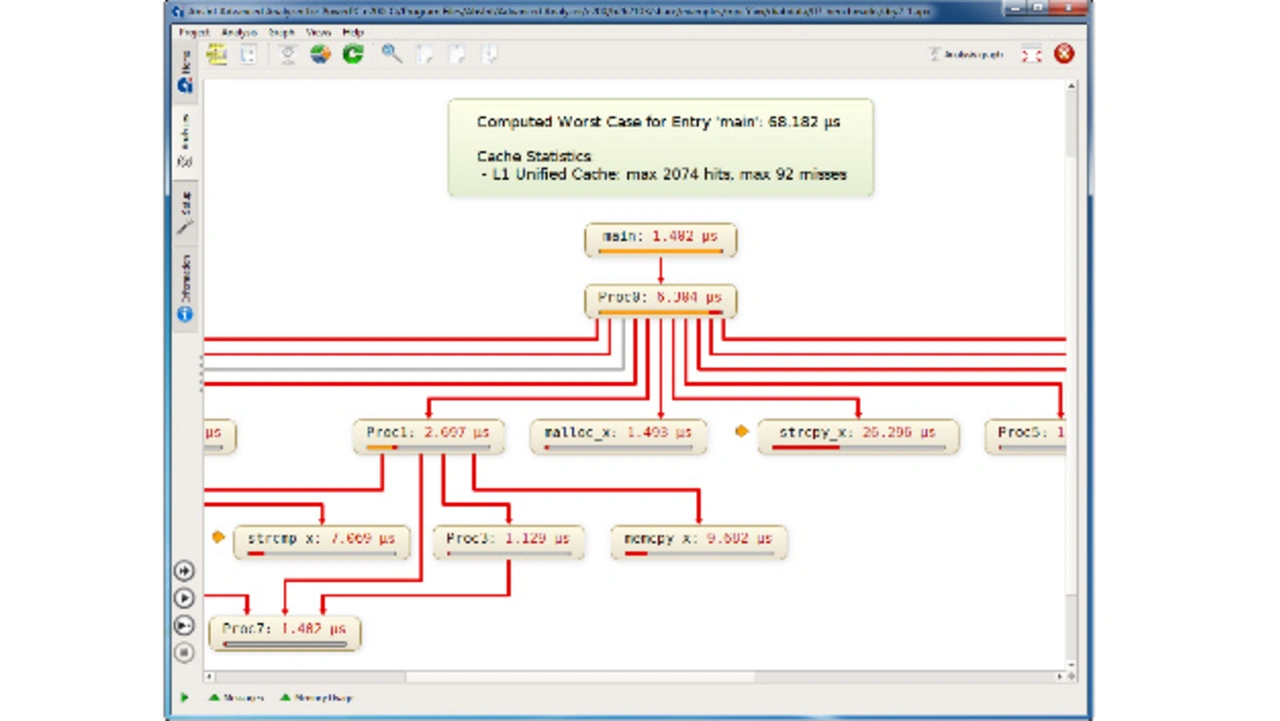

Die beschriebene Methode ist in der Werkzeugfamilie aiT der Firma AbsInt realisiert. Die Zeitanalyse ist stark von der jeweiligen Ausführungsplattform abhängig. Jede Ausführung eines aiT-Werkzeugs für eine spezielle Architektur enthält ein abstraktes Modell der Plattform. Die Modellierung einer neuen Plattform ist sehr aufwendig und benötigt eine präzise Beschreibung dieser Plattform. Der größte Teil dieser Beschreibung, z.B. die des Prozessors, wird vom Werkzeugentwickler in das Werkzeug integriert. Eventuell bleibt ein Rest übrig, welcher vom Systementwickler per Annotation dem Werkzeug bekannt gemacht werden muss. Dieser Rest betrifft die spezielle benutzte Hardwarekonfiguration, z.B. die Speicher- und Cachekonfiguration mit ihren Parametern. aiT wurde inzwischen für viele Plattformen realisiert. Die Wichtigsten sind viele Mitglieder der Freescale PowerPC-Familie, Renesas V850, verschiedene Infineon TriCore/AURIX-Prozessoren, LEON 2 und LEON 3.

- Zeitanalyse komplexer eingebetteter Systeme

- Die Ursache des Problems

- Laufzeitanalyse

- Vorteile der Mikroarchitekturanalyse

- Normen und industrieller Einsatz

- Literatur