IC-Fertigung: Schneller, zuverlässiger und kosteneffizienter soll sie sein

Optimierter IC-Test

Fortsetzung des Artikels von Teil 1

Zu testende Parameter

Drei der wichtigsten Parameter, die man an elektrischen Schaltungen kontrollieren muss, sind Spannung (logisches und funktionales Verhalten), Strom (Kriechströme, Leistungsaufnahme) und das Zeitverhalten (Verzögerungen – Frequenz). Versorgungsstromtests im Allgemeinen und Ruhestromtests (IDDQ) im Besonderen sind die Ecksteine des Testablaufs bei den heutigen ICs. IDDQ hat eine doppelte Bedeutung: Es bezeichnet einmal den Stromverbrauch im Ruhezustand, bezieht sich aber auch auf eine Ruhestrommessung beim Test von CMOS-Bauteilen. Der Ruhestrom fließt, wenn die Schaltung im Ruhezustand ist, was gleichzusetzen ist mit dem Leckstrom für logische Schaltungen, oder die Kombination von Leckstrom und Bias-Strom im Allgemeinen. Der IDDQ-Test erlaubt eine schnelle Identifikation fehlerhafter Teile, sowohl auf Wafer Level als auch beim Final Test.

Nach Überzeugung der Experten von Q-Star ist es nachgewiesen, dass IDDQ-Tests im Vergleich zu anderen Testmethoden die Fehlererkennung verbessern – und das bei geringeren Kosten. Kombiniert mit einem Spannungsstresstest kann IDDQ laut Q-Star den »Burn-in«-Test ersetzen: Zu einem Bruchteil der Burn-in-Kosten biete er mindestens die gleiche, wenn nicht sogar bessere Produktzuverlässigkeit. Sicher ist: Eine gut gewählte Kombination aus Spannungs- und Stromtests führt zu sehr effizienten Testabläufen, die die Testkosten signifikant reduzieren können.

Jobangebote+ passend zum Thema

- Optimierter IC-Test

- Zu testende Parameter

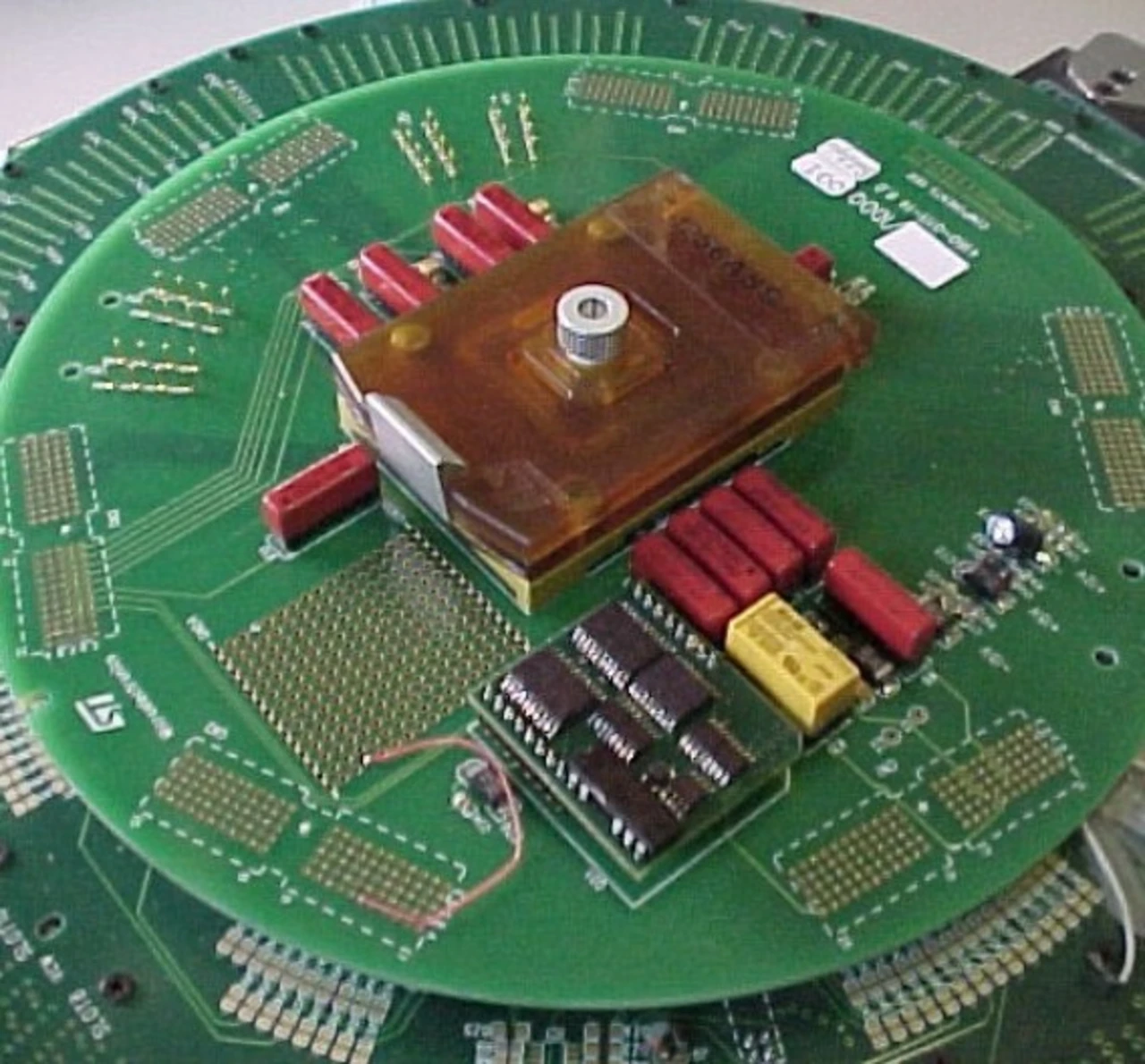

- Die Q-Star-Lösung