Mehrere FPGAs in einem Gehäuse

Xilinx überschreitet Grenzen des Mooreschen Gesetzes

Um immer größere FPGAs mit mehr Logikelementen herzustellen, gibt es zwei Möglichkeiten: Größere Siliziumplättchen oder das Schrumpfen der Prozessgeometrie. FPGA-Marktführer Xilinx hat nun eine dritte intelligente Alternative vorgestellt: Mehere Dies in einem Gehäuse, die über einen sogenannten "Stacked Silicon Interconnect" verbunden werden.

Um neue Märkte in den Bereichen Wireless, Wireline, Medizin-Bildgebung und Militär erschliessen zu können, die bislang von ASICs dominiert werden, reicht das Mooresche Gesetz nicht aus. In den heutigen FPGAs der 40-nm-Generation mit Transceivern befinden sich rund eine halbe Million Logikelemente, durch das Schrumpfen der Prozessgeometrie auf 28 nm dürfen wir ca. 750.000 Logikelemente erwarten - zu wenig, um viele der ASICs in den genannten Zielmärkten ersetzen zu können.

Ein größerer Die wirft Fertigungsprobleme auf: Wir alle erinnern uns noch an die Ausbeute-Probleme bei TSMC bei Einführung des 40-nm-Prozesses, die erst nach einiger Zeit schrittweise gelöst werden konnten. Fakt bleibt aber, dass kleinere Dies zu höheren Ausbeuten führen - und nicht größere. Auch die Zusammenschaltung von mehreren FPGAs auf einem Board ist oft nicht die Lösung, da die I/O-Verschaltungen trotz der zu erwartenen 28-Gbit/s-Transceiver nicht die notwendige Bandbreite bereitstellen können. Zudem wird bei heutigen Designs oft fast ein Drittel des Power-Budgets durch I/Os aufgefressen.

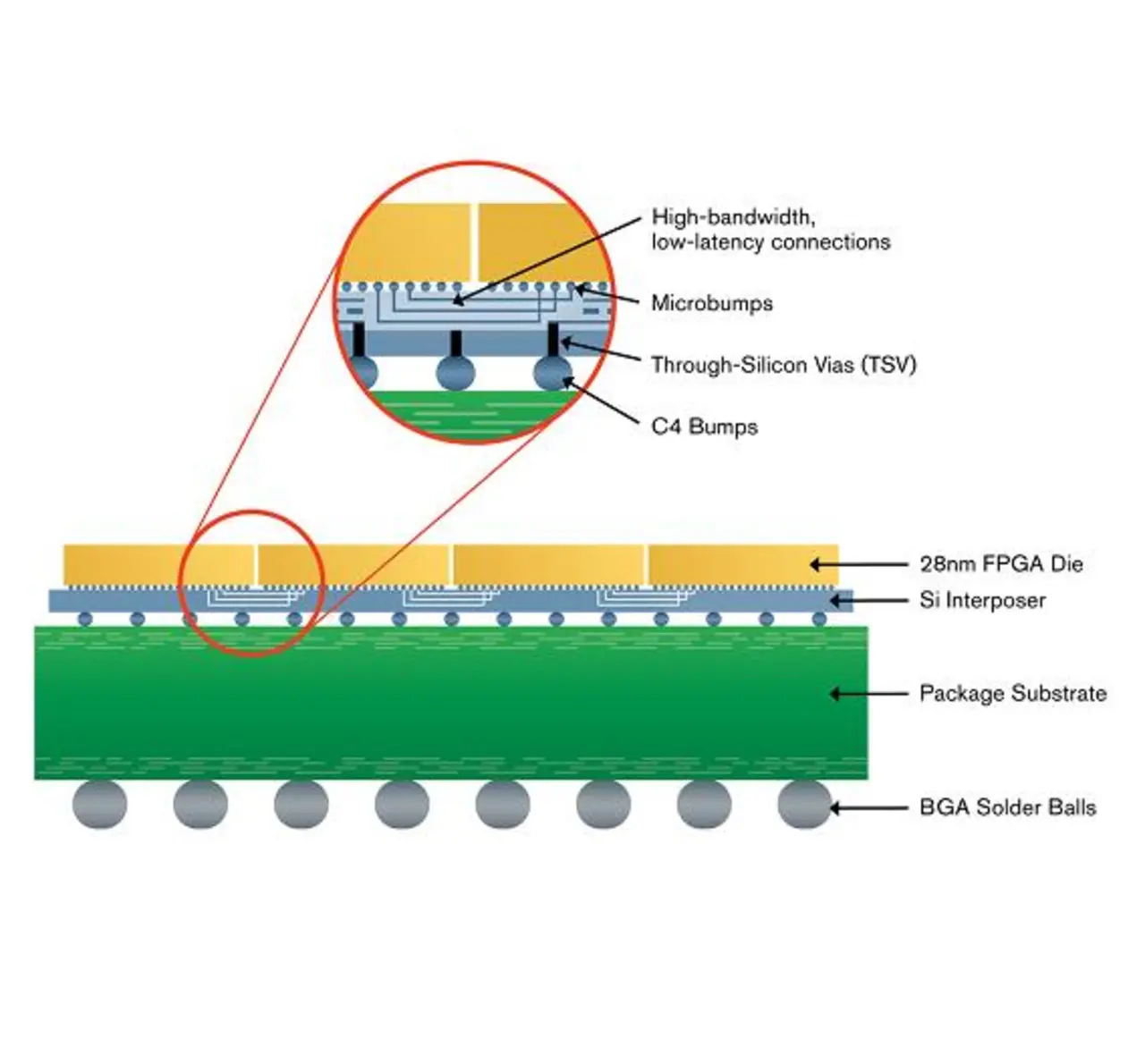

Was also tun? Xilinx hat zusammen mit der Foundry TSMC und einigen anderen führenden Fabless-Herstellern wie Qualcomm eine "Stacked Silicon Interconnect" genannte Technologie entwickelt (Bild), bei welcher mehrere kleinere Dies auf ein Stück Silizium, das ausschließlich als Schaltmatrix dient und keine eigenen Transistoren beinhaltet, aufgepflanzt werden. Als Verbinder dienen sogenannte Microbumps mit einem Durchmesser von nur 45 µm, von denen pro Die mehr als 10.000 Stück zum Einsatz kommen können. Die Außenwelt (Package-Substrat) wird mittels TSVs (Through-Silicon-Vias) und C4-Bumps hergestellt. Der wie gesagt völlig passive Silicon-Interposer wird in einem 65-nm-Prozess gefertigt.

Was ist der große Vorteil dieser Technologie? Zum einen können zwischen den einzelnen "FPGA-Scheiben" (den Dies) mehr als 10.000 Routing-Verbindungen hergestellt werden, zum anderen beträgt die Latenzzeit nur ca. 1 ns. Aus Benutzersicht verhält sich das Multi-Die-FPGA daher wie ein einziges riesiges Siliziumplättchen, durch die Place-and-Route-Tools von Xilinx bleibt die interne Aufteilung in vier Dies unsichtbar. Anders als bei 3D-Stapeln von Dies gibt es hier keine Probleme mit der Wärmeabführung, da die Siliziumplättchen ja nebeneinander und nicht aufeinander liegen. Der passive Silizium-Interposer generiert zudem keine eigene Wärme. Im Vergleich zu einer herkömmlichen Lösung mit mehreren FPGAs auf einem PCB erzielt man auf diese Weise einen Vorteil von Faktor 100 in Bezug auf das Verhältnis Bandbreite/Watt.

Der größte Vorteil besteht natürlich in der Anzahl der Logikelemente, die man in so einem Baustein unterbringt: Das erste Virtex-7-2000T-FPGA dieser Bauart (insgesamt soll es 5 Bausteine, die auf dieser Technologie basieren geben) soll im ersten Quartal 2011 auf den Markt kommen (Muster) und neben 36 10,3-Gbit/s-Transceivern zwei Millionen Logikelemente enthalten, womit man auch komplexere ASICs ersetzen könnte.

Trotz des überzeugenden Konzeptes bleiben zunächst zwei Fragen offen: Ein Zeitpunkt, wann Xilinx die ersten FPGAs mit den im Frühjahr 2010 angekündigten 28-Gbit/s-Transceivern liefern wird, wurde nicht genannt. Laut Patrick Dorsey, Senior Director im Product Marketing bei Xilinx, soll es von Kundenseite noch keine derartige Nachfrage geben - was in krassem Gegensatz zu Aussagen des Konkurrenten Altera steht, wo man "reges Kundeninteresse" an einem Testchip mit 25-Gbit/s-Transceiver festgestellt hatte. Die zweite Frage betrifft den Zugriff des langjährigen TSMC-Kunden Altera auf diese Technologie. In der Regel entwickeln Foundries ja Prozesse, die mehreren Kunden angeboten werden. Eine Aussage, ob und wann Altera diese innovative Technologie nutzen darf bzw. wird, wurde weder von TSMC noch von Xilinx getätigt.

Dagegen wurde bestätigt, dass diese Technologie auch ohne weiteres für Analog/Mixed-Signal-Schaltungen genutzt werden kann: So kann man sich zukünftig FPGAs vorstellen, in denen drei Dies mit "herkömmlicher Logik", DSP-Blöcken und Transceivern ausgestattet sind und zusätzlich auf einem Die Analog/Mixed-Signal-Funktionalität untergebracht wird - was einer weiteren Integration und Reduktion der Board-Größe dienen wird.