Arbeitsspeicher der Zukunft

Speed-Limit (fast) unendlich - Teil 2

Fortsetzung des Artikels von Teil 1

Speed-Limit (fast) unendlich

Die Threading-Architektur

Die Speicher-Subsysteme heutiger Rechnerplattformen werden üblicherweise mit DIMMs implementiert, die einen 64 bit breiten Datenbus und einen 28 bit breiten Command-/Address-/ Clock-Bus haben. In einer typischen Konfiguration sind auf einer Leiterplatte acht (×8) DDR3-Bausteine parallelgeschaltet. Auf einem standardmäßigen DDR3-DIMM wird auf alle Bausteine innerhalb eines Moduls gleichzeitig und mit ein und demselben C/A-Bus zugegriffen. Die daraus resultierende minimale Transfergröße ergibt sich, indem man die 8 bit betragende Burst-Länge mit 64 bit multipliziert, was 64 byte pro Transfer ergibt.

Die minimale effiziente Transferlänge bei einem DIMM der Zukunft mit 64-bit-Bus und einer Burst-Länge von 16 bit wäre dagegen 128 byte pro Zugriff, also die doppelte Transfergröße eines DDR3-Moduls. Diese erhöhte Transfergröße kann zu Effizienzeinbußen bei der Berechnung führen, und zwar speziell bei Multi-Threaded- und Grafik-Applikationen, die vermehrt auf kleinere Datenelemente zugreifen müssen.

Bei Multi-Threaded-Applikationen und kleineren Transfers lässt sich die Effizienz verbessern, indem man das Modul in zwei separate Speicherkanäle aufteilt. Erstmals verwirklicht wurde das Konzept des Mehrkanal-DIMM in dem zweikanaligen Modul RIMM 4200, das von Rambus im Jahr 2002 erstmals demonstriert wurde. In einem zweikanaligen Modul implementiert jede Seite des Moduls einen eigenen Befehls- und Adress-Port, wodurch sich die minimale Transfergröße auf die Hälfte eines konventionellen Einkanal-Moduls reduziert.

Ein zweikanaliges Modul lässt sich mit herkömmlichen Leiterplatten implementieren und erfordert keine zusätzlichen DRAM-Bausteine. Bei diesem Konzept wird lediglich ein zusätzlicher C/A-Port eingerichtet, um die C/A-Bandbreite des Moduls zu verdoppeln. Zusätzlich senkt die Zweikanal-Lösung die Dämpfung des C/A-Signals, da der Controller das C/A-Signal gegenüber einem standardmäßigen DIMM nur an halb so viele Bausteine senden muss.

Das Threaded-Modul bietet als Alternative zu den Zweikanal-Modulen ähnliche Vorteile, allerdings ohne die Notwendigkeit eines zusätzlichen C/APorts. Wie bereits angesprochen, ist in vielen der heutigen DRAM-Bausteine ein hohes Core-Prefetch-Verhältnis implementiert. Die DDR3-Architektur nutzt eine Burst-Länge von 8 bit bei doppelter Datenrate (bei steigenden und fallenden Taktflanken). Während der Übertragungszeit eines einzigen DRAM-Zugriffs besteht die Gelegenheit zur Erzeugung von bis zu vier Zeilen-Aktivierungs-, Lese- oder Schreibanforderungen (mit 1T-Timing und der Auto-Precharge-Funktion). Da für den Zugriff auf ein Daten-Burst lediglich zwei Befehle (Aktivierung plus Lesen oder Schreiben) erforderlich sind, bleibt ausreichend Befehls-Bandbreite übrig, um einen Zugriff auf einen anderen „Speicher-Thread“ auszulösen. Bei einem künftigen DRAM mit einem Core-Prefetch-Verhältnis von 16:1 würde die überschüssige Bandbreite sogar reichen, um zwei Befehle zu implementieren – selbst mit 2T-C/A-Timing. Ein Thread-Modul kann somit in einem Speichermodul und unter Verwendung ein und desselben C/A-Busses zwei Speicherkanäle einrichten. Die Befehle für die beiden Speicherkanäle werden auf dieselben Signal-Leiterbahnen gemultiplext, die auch bei einem traditionellen Einkanal-Modul verwendet werden. Die Zuordnung zum jeweiligen Speicherkanal erfolgt mit Chip-Select-Signalen. Ein Threaded-Modul nutzt folglich nur die ohnehin überschüssige Befehls-Bandbreite und benötigt für die Implementierung eines zweikanaligen Moduls lediglich zusätzliche Chip-Select-Pins.

Jobangebote+ passend zum Thema

Vorteile des Threadings

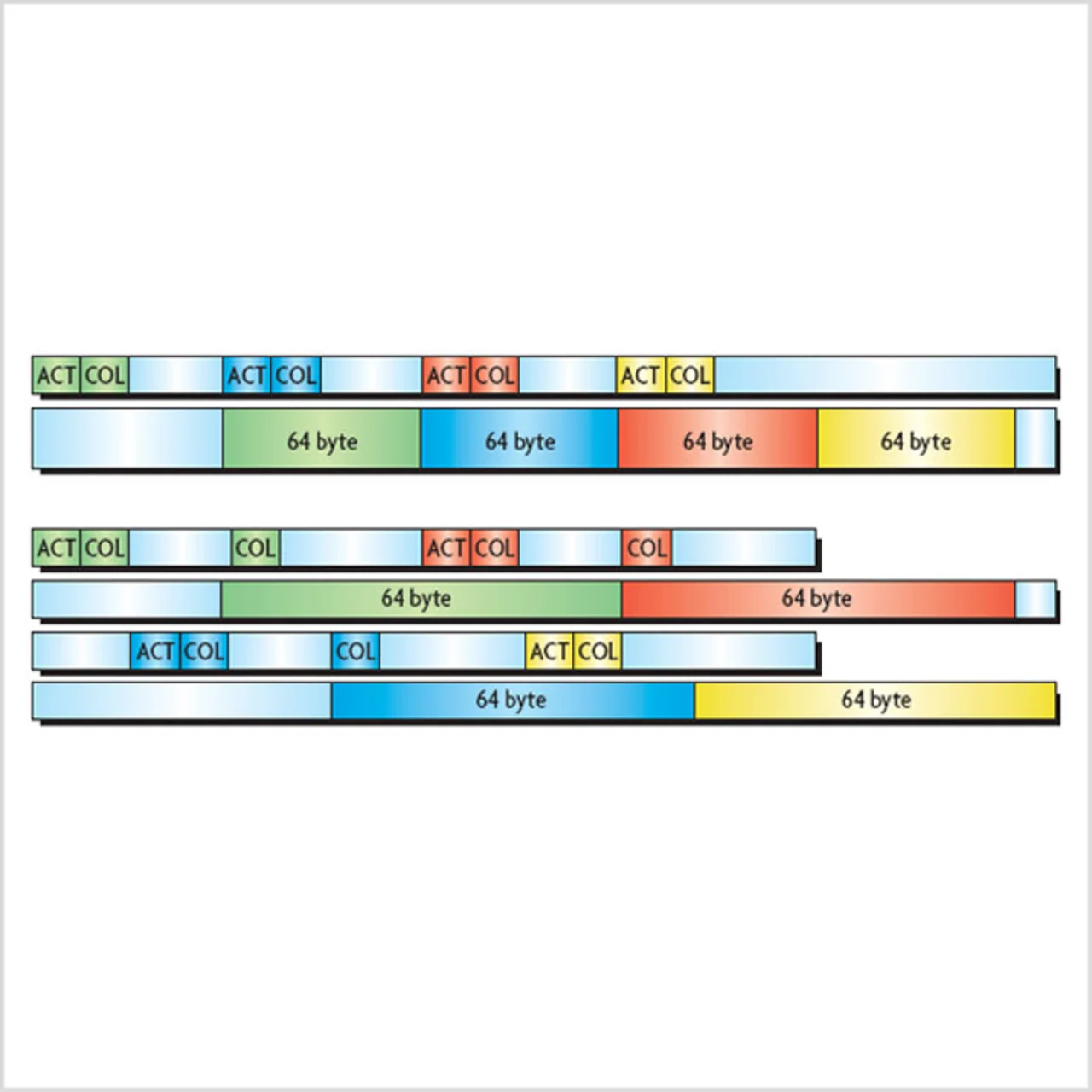

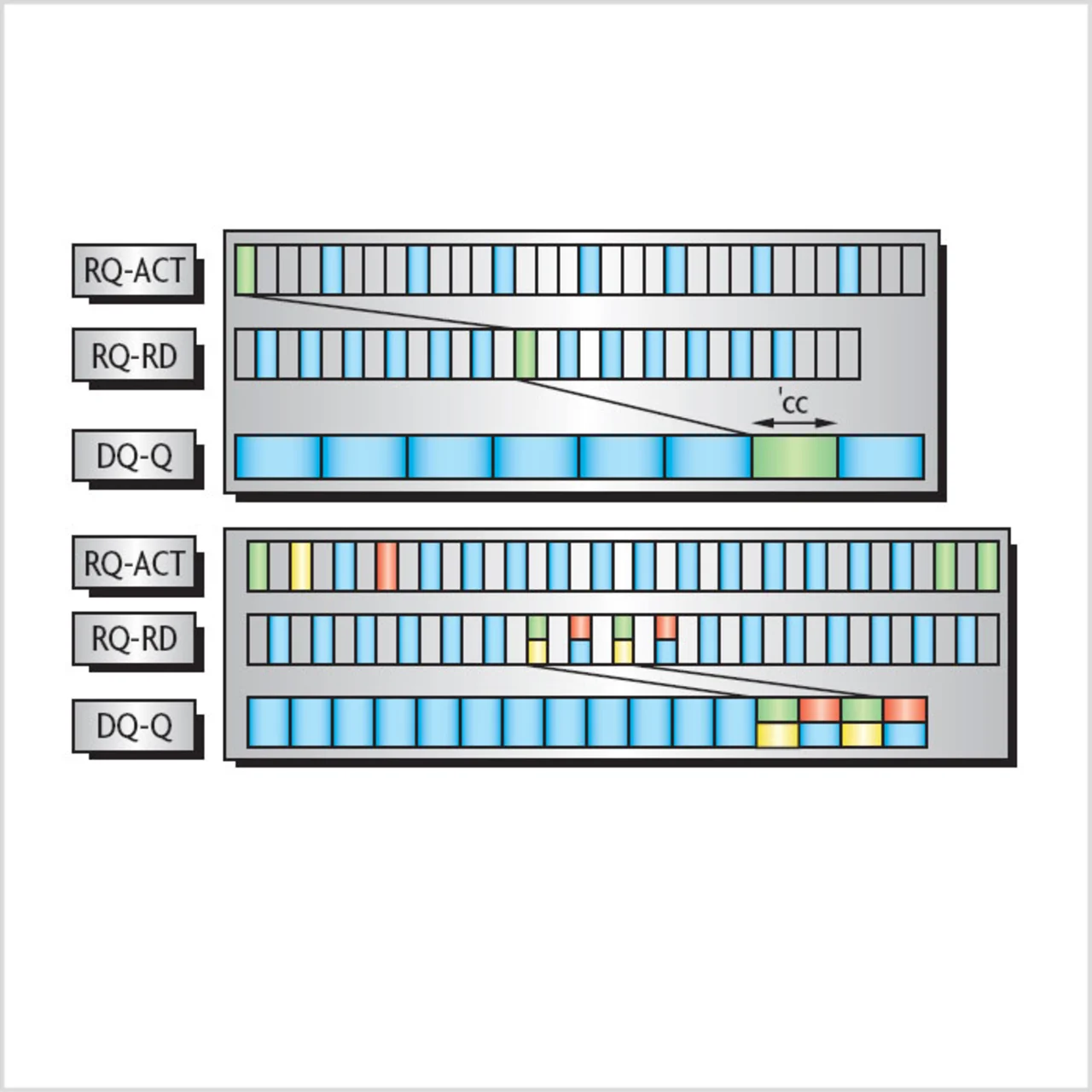

Thread- und Zweikanal-Module können den Energiebedarf für Zugriffe auf den Arbeitsspeicher senken. Wie das Timing-Diagramm in Bild 1 verdeutlicht, lassen sich bei einem Threadund Zweikanal-Modul die Zugriffe auf die verschiedenen Kanäle verzahnen (Interleaving). Abgesehen von den geringeren Mindest-Transfergrößen ist beim Threading auch der Energiebedarf für die Zeilenaktivierung geringer als bei einem konventionellen DIMM.

Bei einem konventionellen Modul mit acht Bausteinen werden stets alle acht DRAMs aktiviert (ACT), bevor sich der Lese- oder Schreibzugriff (COL) auf alle acht Chips anschließt. Ein Threaded- oder Zweikanal-Modul kann denselben Datentransfer abwickeln, indem nur vier Speicherchips aktiviert und anschließend zwei aufeinanderfolgende Lese- oder Schreib-Operationen auf diese vier Bausteine ausgeführt werden. Da im Gegensatz zu acht Bausteinen bei einem konventionellen DDR3-Modul nur mehr vier aktiviert werden müssen, kommt ein Threaded- oder Zweikanal-Modul mit dem halben Energiebedarf für die Zeilenaktivierung auf eine vergleichbare Bandbreite. In einem Speichersystem resultiert hieraus eine ungefähr 20-prozentige Senkung des Gesamt-Energiebedarfs für ein Modul. Mit DDR3-DRAMs wurde ein Thread-Modul implementiert. Messungen bestätigten hier in der Tat einen um 20 % geringeren Energiebedarf gegenüber einem konventionellen einkanaligen Modul.

Als weiterer Pluspunkt kommt bei Threaded- oder Zweikanal-Modulen die größere Dauer-Bandbreite bei hohen Datenraten hinzu. Bei vielen modernen Industriestandard-DRAMs ist die Bandbreite infolge von Verlustleistungs-Restriktionen der DRAM-Bausteine begrenzt. Beginnend mit der DDR3-Generation, darf bei DRAMs nur auf eine begrenzte Anzahl von Bänken zugegriffen werden, um das DRAM-interne Stromversorgungs-Netzwerk zu schützen und eine stabile Versorgungsspannung aufrechtzuerhalten. Dieser, als tFAW bekannte Parameter erlaubt nur die Aktivierung von vier Bänken innerhalb des gleitenden tFAW-Fensters. Die Bandbreiten-Restriktionen durch tFAW betreffen DDR3-DRAMs bei Datenraten über800 Mbit/s. Der tFAW-Parameter hat mit dem Parameter tRC (Core-Zugriffszeit) und der Tatsache zu tun, dass die DRAM-Datenraten schneller zunehmen als die Core-Zugriffszeiten.

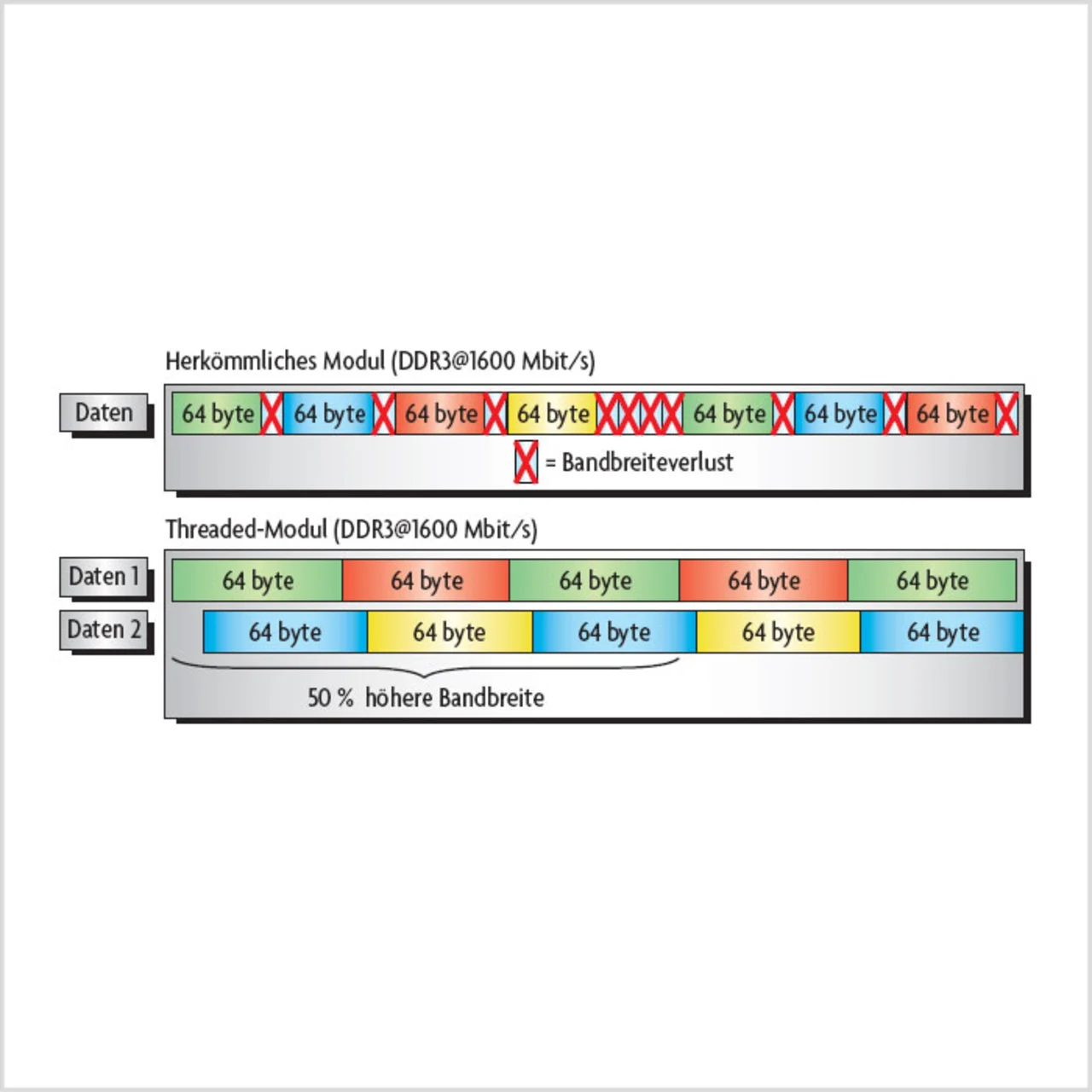

In einem Computersystem hindert tFAW den Speicher-Controller an der Ausgabe weiterer Zeilenaktivierungsbefehle, wenn in einem bestimmten tFAW-Fenster bereits vier Aktivierungsbefehle erfolgt sind. Der Speicher-Controller wird hierdurch blockiert, und die Bandbreite leidet entsprechend. Ein mit 1066 Mbit/s laufendes DDR3-DRAM büßt ungefähr 25 % seiner Dauer-Datenbandbreite ein, da die Speicher-Transaktionen durch die tFAW-Restriktion ausgebremst werden. Bei einer Datenrate von 1600 Mbit/s gehen bei einem DDR3-DRAM bis zu 50 % der Dauer-Datenbandbreite verloren, da die Speicher-Transaktionen hier nicht nur durch tFAW, sondern auch durch tRRD behindert werden (Bild 2).

In einem Threaded-Modul werden die DRAM-Bausteine nur noch halb so oft aktiviert wie in einem konventionellen Modul, und so kommt es hier zu keiner Einschränkung der Dauer-Bandbreite durch tFAW oder tRRD.

Threaded- oder Zweikanal-Module können den Datendurchsatz auch bei nicht-sequenziellen Zugriffen verbessern, da sie im Vergleich zu konventionellen einkanaligen Modulen mehr logische Bänke enthalten. Zum Beispiel lassen sich Speicherzugriffe aus mehreren Threads auf unabhängige Bänke richten, was die Wahrscheinlichkeit von Bank-Konflikten verringert.

Micro-Threading: Threading auf Baustein-Ebene

Elemente des von Rambus auf Modul-Ebene angewandten Threading-Konzepts lassen sich mit einer als „Micro-Threading“ bezeichneten Technologie auch auf einzelne DRAM-Bausteine anwenden. Dieses Micro-Threading nutzt die DRAM-Ressourcen effizienter, indem die Granularität der Zeilen- und Spaltenzugriffe herabgesetzt wird. Die Mindest-Transfergröße lässt sich gegenüber herkömmlichen DRAMBausteinen um den Faktor 4 reduzieren, indem für jeden Quadranten des physischen Speicherbereichs unabhängige Zeilenund Spalten-Schaltungen vorgesehen werden. Die unabhängige Adressierbarkeit jedes Quadranten passt außerdem zu der in verschiedene Threads gegliederten Speichernutzung moderner Grafik- und Multicore-Prozessoren. Diese spezielle Architektur erlaubt ein Micro-Threading, um einerseits die Gesamt-Datenbandbreite zu wahren und andererseits den Energiebedarf pro Transaktion zu senken.

Wie weiter oben bereits ausgeführt, hat das höhere Core-Prefetch-Verhältnis moderner DRAMs die Zugriffs-Granularität erhöht (d.h., es wird stets auf einen größeren Umfang an Daten zugegriffen). Tatsächlich stellen viele DRAM-Subsysteme mehr Daten bereit, als von Applikationen wie zum Beispiel Grafik oder Multicore-Computing benötigt werden. Dieses Abrufen eigentlich unnötiger Daten ist aber ineffizient, denn es führt zu unnötigem Energieverbrauch im DRAM und für die Signalübertragung. Die Zugriffs-Granularität ist eine Funktion der Zugänglichkeit der Daten in einer Speicherarchitektur.

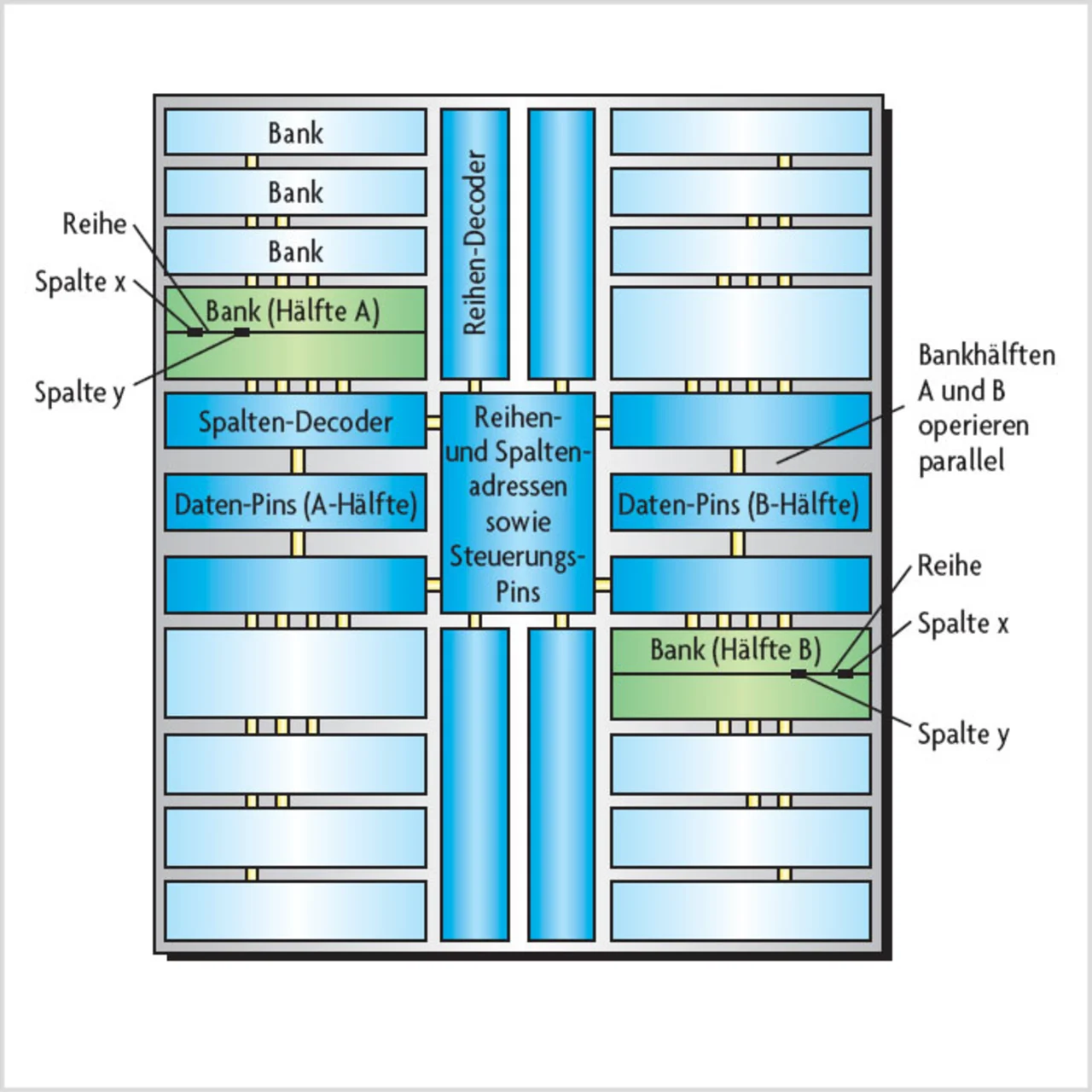

Ein typisches DRAM setzt sich aus acht Speicher-Bänken zusammen, die wiederum in zwei Halbbänke (A und B) unterteilt sind (Bild 3). Bei einem solchen DRAM mit 32 Daten-Pins sind die Bänke A und B an jeweils 16 Daten-Pins angeschlossen. Die Bänke befinden sich in gegenüberliegenden Quadranten des physischen Die, und jeder Quadrant ist mit seinen eigenen Zeilen- und Spalten-Schaltungen ausgestattet. Die einzelnen Bank-Hälften treten auf Zeilen- und Spaltenbefehle hin jeweils parallel in Funktion.

Ein Zeilenbefehl selektiert in jeder Hälfte der adressierten Bank eine Zeile, was zum Auslesen und Zwischenspeichern der betreffenden Zeile führt. Physikalisch bedingte Timing-Restriktionen bewirken eine Verzögerung (tRRD), bevor auf eine Zeile in einer anderen Bank zugegriffen werden kann. Bei Spaltenbefehlen existiert eine ähnliche Beschränkung (tCC). Allerdings macht das Zeilen-Timing-Intervall üblicherweise das Doppelte des Spalten-Timing-Intervalls aus, und so können während der zwangsweisen Wartezeit für die Aktivierung einer einzelnen Zeile zwei Spaltenbefehle ausgegeben werden.

Die Spalten-Prefetch-Länge, also der Umfang der pro Transaktion bereitgestellten Daten, berechnet sich nach der folgenden Formel aus den Spalten- bzw. Zeilen-Verzögerungszeiten:

Prefetch = Verzögerungszeit/Transferrate

Ein DRAM arbeitet typisch mit 200 MHz, während ein Hochleistungs-Industriestandard-DRAM mit typisch bis zu 400 MHz arbeiten kann. Frequenzen über 400 MHz sind dagegen mit modernen Industriestandard-DRAMTechnologien schwierig zu realisieren, ohne dass die Produktionsausbeute leidet oder die Kosten steigen. Aus diesem Grund wird für ein solches Hochleistungs-DRAM ein Spalten-Prefetch von 16 bit benötigt, um externe Datenraten von mehr als 3200 MHz zu unterstützen, denn das DRAM ist so organisiert, dass beide Halbbänke mit derselben Zeile bzw. Spalte arbeiten. Hinzu kommt folgende Beziehung:

Spalten-Granularität = Spalten-Prefetch × Zahl der Daten-Pins pro Halbbank × Zahl der Halbbänke je Zugriff

Für ein 32 bit breites DRAM mit 16 Daten-Pins je Halbbank gilt deshalb:

Spalten-Granularität = 16 × 16 × 2 = 512 bit bzw. 64 byte

Um die Maximal-Bandbreite zu halten, müssen außerdem während des Zeilen-Intervalls mindestens zwei Spalten-Operationen ausgeführt werden. Es kommen also zwei Column-Address-Strobes (CAS) auf einen Row-Address-Strobe (RAS), und folglich resultiert hieraus eine minimale Zeilen-Granularität von 128 byte. Diese grobe Zugriffs-Granularität resultiert in einer ineffizienten Daten- und Energienutzung beispielsweise in 3DApplikationen.

Micro-Threading in DRAMs

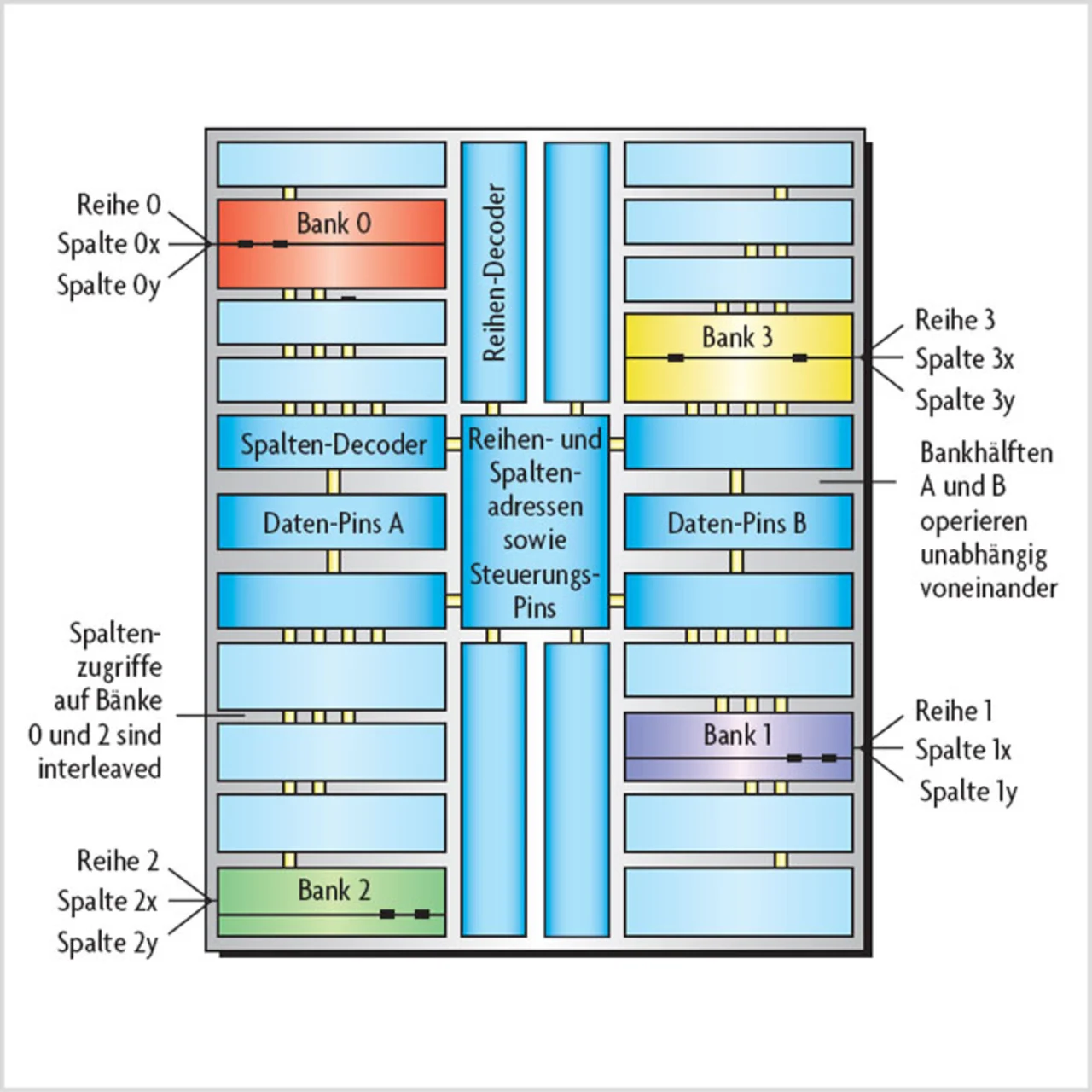

Ausgehend vom vorigen Beispiel sei ein exemplarisches DRAM mit Micro-Threading und 16 Bänken angenommen (Bild 4), wobei jede Bank dieses Micro-Threaded-DRAMs einer Halbbank des typischen DRAMs entspricht. Während die geradzahligen Bänke mit den Daten-Pins der Gruppe A verbunden sind, sind die ungeradzahligen an die Daten-Pins der Gruppe B herausgeführt (wiederum mit je 16 Pins). Im Unterschied zu einem typischen DRAM kann hier jedoch jeder Vier-Bank-Quadrant dank der für jeden Quadranten unabhängig ausgeführten Zeilen- und Spaltenschaltungen eigenständig operieren. Das Interleaving, also der gleichzeitige Zugriff auf mehr als eine Speicher-Bank, lässt hier außerdem gleichzeitige Zugriffe auf den unteren Quadranten derselben physischen Seite des DRAMs zu, an die auch der vorhergehende Zugriff gerichtet war.

Mit Micro-Threading lassen sich gleichzeitig vier unabhängige Zugriffe auf das DRAM ausführen. Zwar muss nach wie vor dieselbe Zeit verstreichen wie bei einem typischen DRAM, bevor auf eine zweite Zeile einer Bank oder eines Bank-Quadranten zugegriffen werden kann, doch kann in diesem Zeitraum separat auf die drei Bänke in den übrigen Quadranten zugegriffen werden. Auf Spalten in den Zeilen anderer Quadranten kann somit parallel zugegriffen werden, auch wenn das Column-Timing-Intervall abgewartet werden muss, bis in der zuvor aktivierten Zeile eine neue Spalte für einen Zugriff verfügbar ist. Diese Unabhängigkeit der Quadranten und das Interleaving haben letztendlich den Effekt, dass während eines Row-Timing-Intervalls auf vier Zeilen (je eine pro Quadrant) und acht Spalten (zwei pro Zeile) zugegriffen werden kann, während ein DRAM in konventioneller Technik nur eine Zeile und zwei Spalten unterstützt.

Die Timing-Werte ähneln denen eines typischen DRAMs, doch sendet jede Spalte nur für die Hälfte des Column-Timing-Intervalls tatsächlich Daten. In der anderen Hälfte sendet die andere am Interleaving beteiligte Spalte ihre Daten. Das Micro-Threading reduziert somit die minimaleTransfer-Granularität, während die Taktfrequenz beibehalten wird. Durch das Verzahnen der Spaltenzugriffe aus vier verschiedenen Bänken kommt ein micro-threaded DRAM (bei gleicher Spalten-Prefetch-Länge und Taktfrequenz) auf die doppelte Datenrate eines konventionellen DRAMs. Umgekehrt lässt sich durch das Micro-Threading der Spaltenansteuerung erreichen, dass ein DRAM auf kosteneffektive Weise eine bestimmte Datentransfer-Granularität unterstützt, während die Spaltenzykluszeit (tCC) gegenüber einem herkömmlichen DRAM bis um den Faktor 2 gelockert wird. Mit Micro-Threading berechnet sich die Spalten-Granularität jetzt wie folgt:

Spalten-Granularität = Spalten-Prefetch/ 2 × 16 Pins = 16/2 × 16 = 128 bit bzw. 16 byte

Es handelt sich also um ein Viertel des vorigen Werts (Bild 5). Die Zeilen-Granularität macht jetzt 32 byte aus (wiederum ein Viertel des vorigen Werts). In vielen Anwendungen bewirkt die per Micro-Threading erreichte feinere Granularität einen Leistungs-Schub.

Ein weiterer Vorteil liegt darin, dass die Zahl der logischen Bänke gegenüber DRAMs ohne Threading gesteigert wird. Unter anderem lassen sich Speicherzugriffe von verschiedenen Threads auf unabhängige Bänke richten, so dass doppelt so viele Bänke genutzt werden und das Risiko von Bank-Konflikten entsprechend sinkt.

Literatur

[1] Best, S.; Ching, M.: Speed-Limit (fast) unendlich, Teil 1. Elektronik 2009, H. 19, S. 26ff.

[2] Website des Herstellers: www.rambus.com

| B.S.E.E. Scott Best |

|---|

| studierte Elektrotechnik an der Cornell University, Ithaca, N.Y. Er arbeitet als Senior Principal Engineer bei Rambus und hält mehr als 20 Patente in den Bereichen Schaltkreis-Design und Systemtechnik. |

scott_best@rambus.com

| M.Sc. Michael Ching |

|---|

| studierte Elektrotechnik an der University of California in Berkeley. Er begann seine Karriere bei Intel, wo er Hochgeschwindigkeits-I/Os für Mikroprozessoren entwickelte. 1996 kam er zu Rambus, wo er diverse Positionen in Entwicklung und Marketing besetzte. Heute arbeitet er als Direktor für strategische Entwicklungen. |

Michael_Ching@rambus.com

- Speed-Limit (fast) unendlich - Teil 2

- Speed-Limit (fast) unendlich