Nicht der Erste, aber der Pfiffigste?

CES: Atmel stellt Cortex-M7-Controller für Automotive, Industrie und IoT vor

Fortsetzung des Artikels von Teil 1

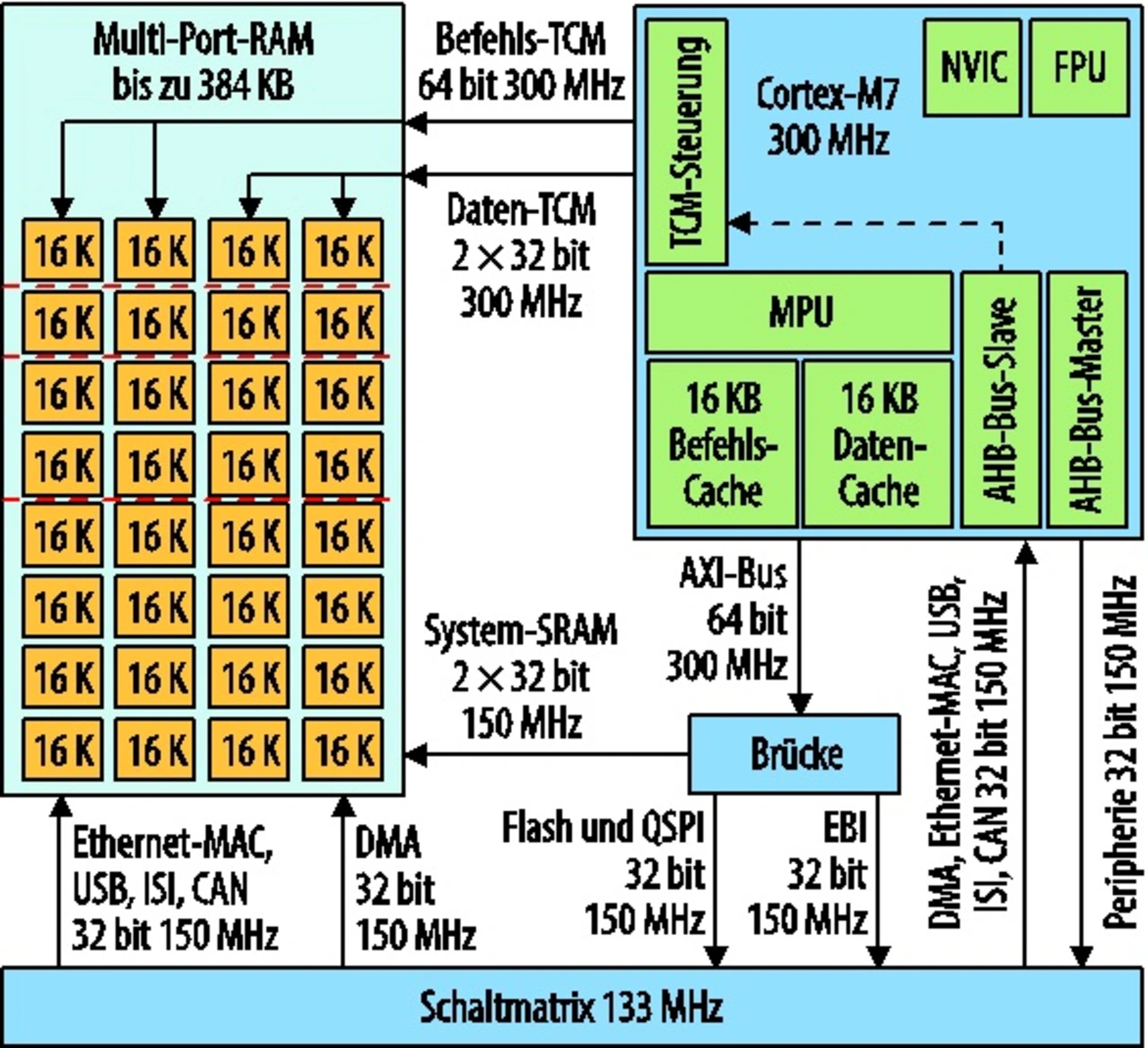

On-Chip-SRAM als TCM oder Systemspeicher konfigurierbar

Auf den „eng angebundenen Speicher (TCM)“ kann die CPU innerhalb eines Taktzyklus zugreifen, womit er sich für die zeitkritischen Abschnitte einer Anwendung eignet, die deterministisches Verhalten benötigt. Das System-RAM kann für Kommunikations-Stacks wie Feldbusse oder USB benutzt werden. Hat man also Echtzeit-Anwendungen wie Audio-Encoding/Decoding oder Motorsteuerung bzw. Anwendungen, die eine schnelle Datenverarbeitung erfordern wie z.B. Fingerabdruck-/Spracherkennung, wird man einen größeren TCM-Bereich konfigurieren, arbeitet man viel mit Kommunikations-Stacks, dagegen das System-SRAM.

Desweiteren bietet die MCU noch 12 KB SRAM als Ethernet-Puffer, 4 KB SRAM als USB-Puffer, 1 KB Backup-SRAM, einen Speichercontroller für externes SDRAM (8 oder 16 bit Daten, 2 oder 4 Speicherbänke) und die schon erwähnte EBI-Schnittstelle für die Anbindung von externem NAND- oder NOR-Flash. Bild 2 zeigt die Speicherarchitektur des SAMX70.

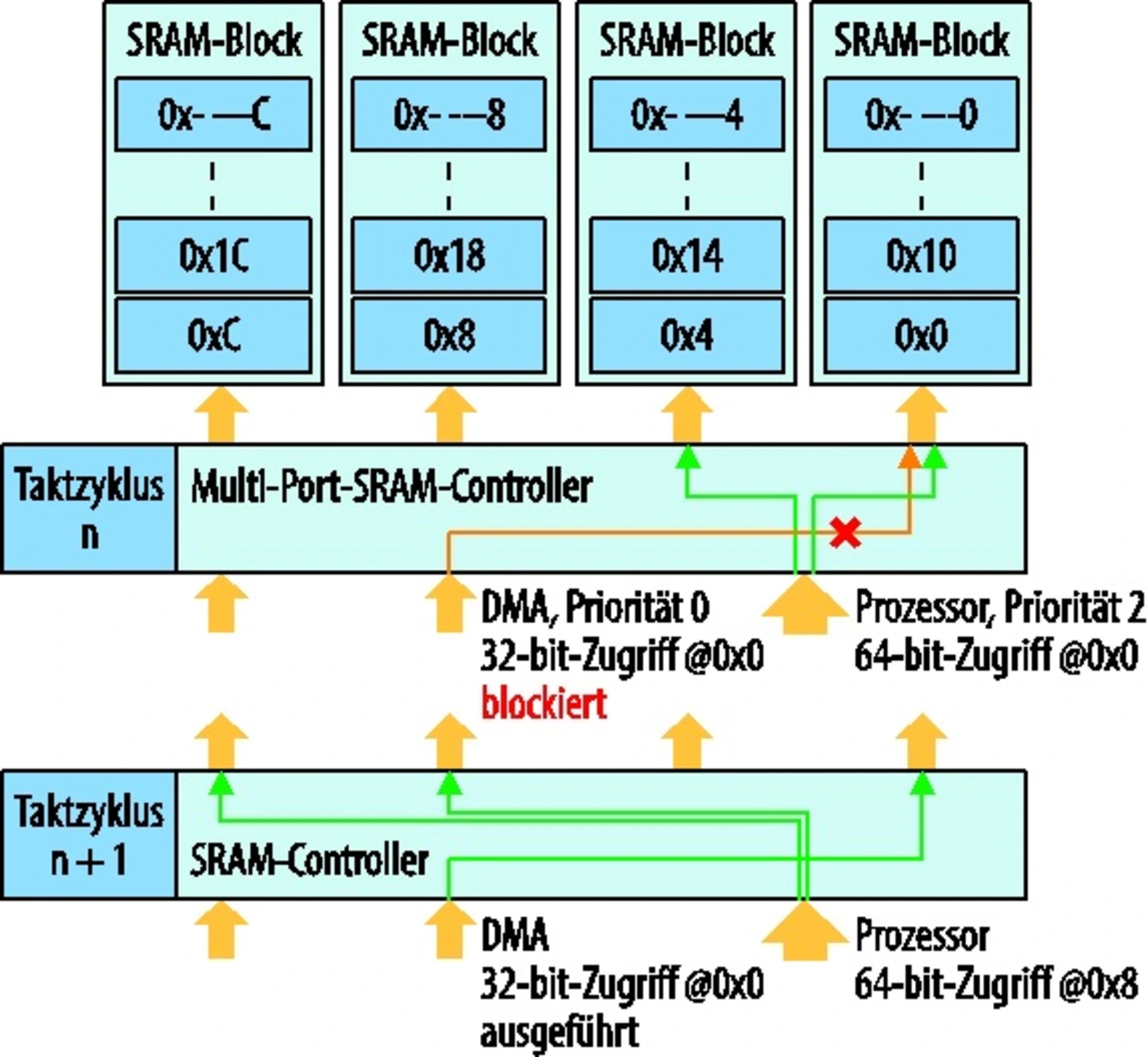

Warum aber hat Atmel seinen Speicher „Multi-Port-RAM“ genannt? Ganz einfach: Weil es über vier Ports auf den Speicher zugreift, um Blockaden zu verhindern und die MCU-Rechenlesitung zu maximieren, ohne dabei Anforderungen von latenzzeit-kritischen Peripherien mit hoher Priorität (z.B. Transfer eines USB-Descriptors) aus den Augen zu verlieren.

Jobangebote+ passend zum Thema

Um die Zugriffe von DMA und Caches möglichst schnell abarbeiten zu können, werden Speicherzugriffe im Burst-Modus betrieben. Im Gegensatz zum sogenannten Wort-Modus werden beim Burst-Modus größere Datenblöcke als ununterbrochenes Bündel kleinerer Dateneinheiten übertragen, ohne dass gewisse Initialisierungen für jede dieser Untereinheiten neu erfolgen müssten. Beispielsweise kann eine Cache-Line zu 16 Byte als Bündel von vier Dateneinheiten zu 4 Byte übertragen werden. Die Folge bei Speichersystemen mit nur einem Port ist jedoch, dass der Zugriff für die Dauer eines Bursts blockiert werden kann.

Atmels Multi-Port-RAM reduziert dank Interleaving diese möglichen Konflite auf einen Taktzyklus (Bild 3). Ein Arbiter priorisiert für jeden Port individuell den Speicherzugriff, wobei die Prioritäten (0-3 mit 3 am höchster) in jedem Master individuell festgelegt werden können. Die CPU hat immer die Priorität 2. Mit der „Überpriorisierung“ der CPU sollte man freilich vorsichtig sein, Priorität 3 kann man wohl guten Gewissens nur für Master empfehlen, die einen limitierten Speicherzugriff ausüben.

- CES: Atmel stellt Cortex-M7-Controller für Automotive, Industrie und IoT vor

- On-Chip-SRAM als TCM oder Systemspeicher konfigurierbar

- Das gibt es an Peripherie

- Vergleich mit der Konkurrenz und Fazit