Konkurrenz für ARM

Andes liefert Ultra-Low-Power-CPU-Cores

Fortsetzung des Artikels von Teil 2

Der neueste Andes-Core

Der N705 nimmt bei Fertigung in einem 90-nm-LP-Prozess von TSMC nur 11 µW/MHz auf. Bei 50 MHz liefert er in seiner Minimalkonfiguration 60 DMIPS, genug Rechenleistung für einen Touchscreen-Controller, Power-Management-IC oder Sensor-Controller – und das bei 0,5 mW dynamischer Leistungsaufnahme. Der Core ist ebenso sparsam was die Chipfläche angeht, hier stehen in 90 nm weniger als 0,04mm2 zu Buche. In fortschrittlicheren Prozessknoten würde die CPU praktisch verschwinden.

Die Pipeline hat nur zwei Stufen: Befehl holen und ausführen. Die Kürze begrenzt die Taktfrequenz, auf der anderen Seite optimiert sie auch das Design: Die gesamte CPU wird inklusive dem kleinen Multiplizierer, der 17 Taktzyklen für eine 32x32-bit-Multiplikation benötigt, in 12.000 Gattern abgebildet. Designer können den N705 auch mit einem schnellen Multiplizierer konfigurieren, der 32x32 bit in 1 Taktzyklus berechnet. Zur weiteren Vereinfachung kann man die v3m-Teilmenge des Befehlssatzes und nur 16 Allzweck-Register implementieren.

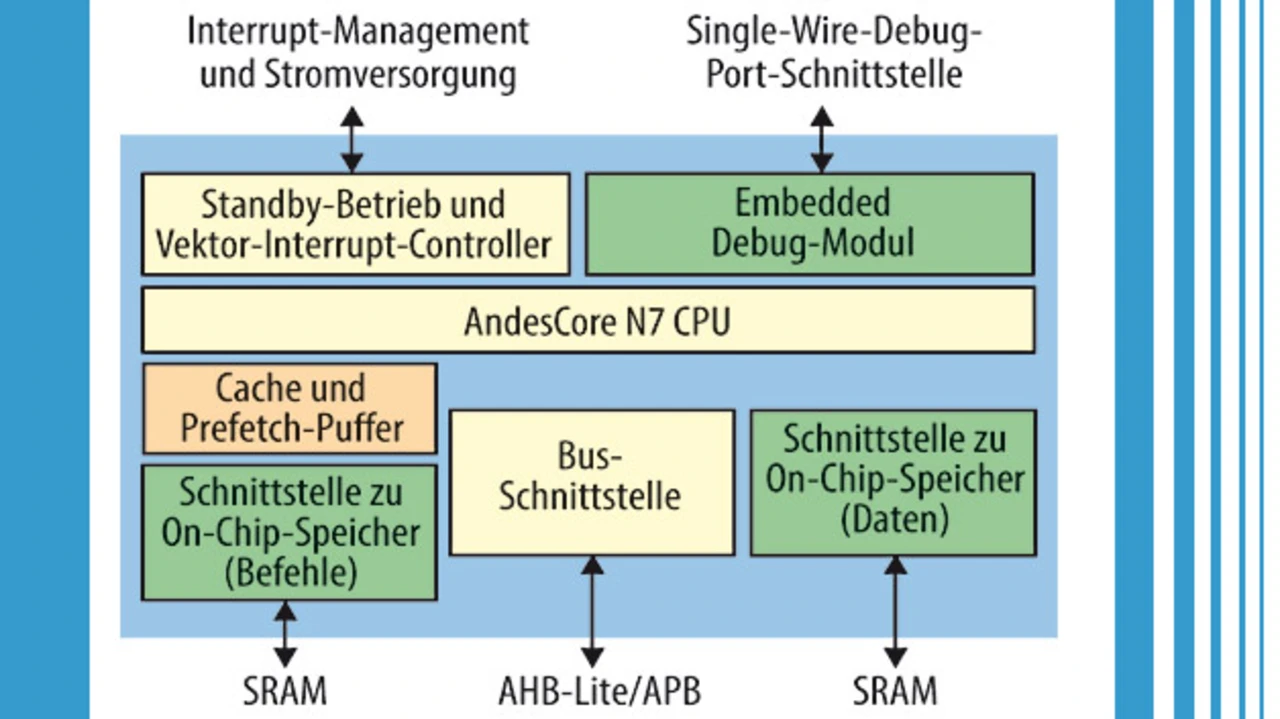

Bild 1 zeigt den N705 in seiner vollständigen Konfiguration. Der Vektor-Interrupt-Controller (VIC) ermöglicht bis zu 32 Interrupt-Quellen. Das optionale Debug-Modul stellt eine Zwei-Draht-Schnittstelle bereit. Während die minimale Konfiguration einen einzelnen AHB-Lite-Bus für die Verbindung zu allen Speichern und Peripherien nutzt, kann die CPU auch mit separaten Befehls-und Daten-Schnittstellen zum SRAM konfiguriert werden. Durch diese Zusatzbusse wird die Rechenleistung um 22 % erhöht, allerdings verdoppelt sich in maximaler Konfiguration auch die Gatter-Zahl und fast auch die dynamische Leistungsaufnahme.

Die optionalen Schnittstellen verbessern nicht nur die Rechenleistung, sondern geben auch den SoC-Designern mehr Flexibilität. Zahlreiche Peripherie-IP-Blöcke nutzen den Amba-Standard und werden an die Bus-Schnittstelle angeschlossen. Die minimale Konfiguration unterstützt nur diese Peripherien. Wenn der Designer wünscht, Peripherien mit einer SRAM-ähnlichen Schnittstelle zu verwenden, können sie entweder an die Befehls- (ILM) oder Datenschnittstelle (DLM) angeschlossen werden. Man kann auch auf die Datenschnittstelle verzichten und alle Peripherien und Speicher mit der ILM verbinden, aber für die höchste Rechenleistung sollten Peripherien und Datenspeicher mit der DLM und nur der Befehlsspeicher mit der ILM verbunden sein.

Die N705 ist entworfen worden, um eine direkte Verbindung mit On-Chip- oder externem Flash-Speicher herzustellen. Die ILM-Schnittstelle kann mit 16, 32 oder 64 Bit Breite konfiguriert werden, die breiteren Schnittstellen liefern logischerweise den höheren Datendurchsatz, insbesondere bei langsameren Speichern. Wenn die Flash-Geschwindigkeit weniger als ein Drittel der CPU-Geschwindigkeit beträgt, empfiehlt Andes die Konfiguration einer 64-Bit-Schnittstelle und den Einsatz der N705-Prefetch-Puffer-Einheit (DEA). Dieser kleine Puffer kann gleichzeitig von der CPU gelesen und aus dem Speicher gefüllt werden. Eine weitere nützliche Option für Flash-basierten Code ist der winzige Cache. Dieser 128-Byte-Puffer benötigt nur 7.000 Gatter, ist jedoch groß genug, um die meisten inneren Schleifen aufzunehmen, wodurch Speicherzugriffe um bis zu 50 % reduziert werden. Dies steigert nicht nur die Rechenleistung, sondern reduziert durch den Wegfall der energiehungrigen Speicherzugriffe auch die Leistungsaufnahme.

Jobangebote+ passend zum Thema

- Andes liefert Ultra-Low-Power-CPU-Cores

- Die AndeStar-Architektur

- Der neueste Andes-Core

- ARM wird bei Kosten und Leistungsaufnahme unterboten

- Marktposition und Fazit