Everspin

1-GBit-MRAMs für den Mainstream

Fortsetzung des Artikels von Teil 2

Durchbruch in Sicht

Dass jetzt der Durchbruch gelingen könnte, davon geht auch Thomas Coughlin aus, President von Coghlin Associates: »Mit den Embedded MRAMs auf Basis des 22FDX-Prozesses bietet GlobalFoundries einen entscheidenden Vorteil für die SoCs, nämlich einen Speicher, der wenig Platz einnimmt und sich mit geringer Leistungsaufnahme zufrieden gibt. Die Designer von batteriebetriebenen IoT-Geräten, von Automotive-MCUs und -SoCs und SDD-Speichercontrollern lieben diese vielseitigen nichtflüchtigen Speicher schon heute.«

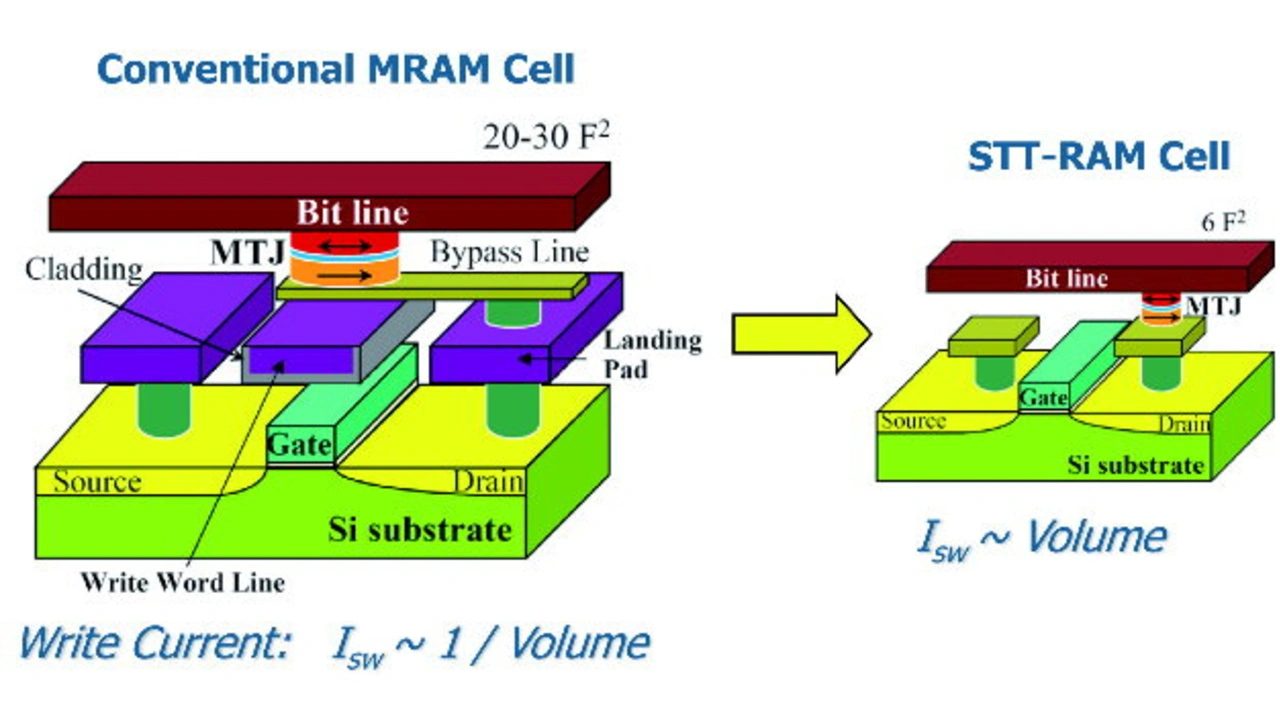

Phill LoPresti jedenfalls sieht Everspin als führend im MRAM-Geschäft. »Von Wettbewerbern wie Avalanche sehe ich nichts auf dem Markt, auch Samsung und TSMC entwickeln, aber bieten derzeit nichts an.« Tatsächlich entwickeln einige große Firmen (zum Beispiel auch Hynix und Toshiba) sowie Startups derzeit offen oder versteckt an MRAM-Techniken. Denn es scheint klar zu sein, dass die NAND-Typen Schwierigkeiten mit der Skalierung haben, sobald die für ihre Fertigung erforderlichen Strukturen unter 28 nm sinken. Zwar gehen die Hersteller jetzt in die dritte Dimension, aber das sorgt für deutlich mehr Maskenschritte, was die 3D-NANDs teuer macht. Dagegen versprechen die MRAMs, mit weniger zusätzlichen Maskenschritten auszukommen. Und noch nehmen die eingebetteten Speicher – meist sind es SRAMs, bestehend aus 4- oder 6-Transistorzellen – in SoCs oder MCUs zwischen 50 und 80 Prozent der Gesamtfläche ein. Mit embedded MRAMs ließe sich also gewaltig Fläche einsparen, weshalb viele Experten hier den ersten großen Hebel für die MRAM-Technik sehen.

Auch Bo Svarrer Hansen, seit 2002 CEO der dänischen Capres, ist überzeugt, dass der MRAM-Markt nun endlich vor dem Durchbruch stehe. Alle großen Firmen würden daran arbeiten. Er muss es wissen, denn Capres liefert die Geräte, die die grundlegenden Messungen für die MTJ-Stack-STT-MRAM-Speicher durchführen. Die Technik hatte Capres zusammen mit IBM entwickelt – eine Firma, die nach den Worten von Hansen auch heute noch zu den führenden Entwicklern der MRAM-Technik zählt. Erst im Sommer dieses Jahres hatte IBM bekannt gegeben, zusammen mit Samsung SST-MRAMs zu entwickeln. Hansen jedenfalls rechnet damit, dass STT-MRAMs zunächst als embedded Speicher auf SoCs in ein bis zwei Jahren auf den Markt kommen, Stand-alone -TT-MRAMs etwas später. Ob sie SRAMs und DRAMs ersetzen können? Das hinge allein von ihrem Preis ab. Dass er sinkt, dafür sieht Hansen aber gute Chancen.

Samsung

Dieser Meinung scheint seit längerem auch Samsung zu sein. Die Koreaner haben sich 2011 den MRAM-Start-up Grandis einverleibt. Dass MRAMs durchaus auch ihre Schwierigkeiten haben, ist der langen Entwicklungszeit zu entnehmen, die es gedauert hat, bis die 256-MBit-Typen zu akzeptablen Preisen zur Verfügung standen – und demnächst die 1-GBit-Typen, wenn man Everspin glauben darf. Samsung jedenfalls hat auf der Design-Automation-Konferenz in Austin im Juni dieses Jahres einen 28-nm-FD-SOI-Prozess vorgestellt, in dem das Unternehmen Stand-alone- und Embedded-MRAMs anbieten will. Der Zeithorizont: ab 2017/18. Wir dürfen gespannt sein, ob das Unternehmen die Zeitvorgabe einhalten kann.

Avalanche

Denn es gibt auch noch andere Mitspieler. Zu den Start-ups gehört die 2006 gegründete Avalanche. Die Firma mit Sitz in Fremont hatte kürzlich angekündigt, STT-basierte MRAMs auf Basis eines 55-nm-Foundry-Prozesses zu liefern. Auch diese Speicher – gefertigt auf 300-mm-Wafern – basieren auf einer pMTJ-Zellen-Architektur. Insgesamt sei die Technik durch über 220 Patente geschützt. Weil Avalanche gleich mit der STT-Technik losgelegt hat, sieht sich das Unternehmen in dieser Technik als führend und ist immerhin überzeugt, als erste STT-MRAM-Samples liefern zu können. Everspin nimmt es gelassen, denn, wie gesagt, das Unternehmen liefert derzeit Samples der 256-MBit-Typen, und die 1-GBit-MRAMs werden schnell folgen.

Die Speichergrößen, die Avalanche jetzt liefert: 32 und 64 MBit. Da versteht man die Gelassenheit von LoPresti. Erst kürzlich hatte Avalanche bekannt gegeben, dass Sony Semiconductor die Rolle der Foundry für die Fertigung der pMTJ-STT-MRAMs auf 300-mm-Wafern »in verschiedenen sehr fortschrittlichen Nodes« übernehmen werde. Auch Gründer und CEO Petro Estakhri ist überzeugt, dass die neuen Speicher das Potenzial haben, sowohl SRAMs, embedded Flash und ROM in Embedded-Anwendungen zu ersetzen als auch die Stand-alone-SRAMs, -NOR-Flash und -DRAMs abzulösen. Die Stückzahlproduktion visiert Avalanche »für das frühe Jahr 2017« an.

Jobangebote+ passend zum Thema

- 1-GBit-MRAMs für den Mainstream

- Die Zukunft gehört pMTJ-STT-MRAMs

- Durchbruch in Sicht

- Crocus