IEDM 2012

Intel zeigt ersten 22-nm-SoC-Prozess mit FinFETs und wiederspricht IMEC

Für Mikroprozessoren gibt es ihn schon länger, jetzt hat Intel seine 22-nm-Fertigung mit FinFET-Transitoren auch auf SoCs ausgedehnt. Nicht nur die unterschiedlichen Anforderungen hinsichtlich Rechenleistung und Leistungsaufnahme wurden berücksichtigt, auch SRAM, Analog-Blöcke und passive Komponenten profitieren von der neuen Technologie.

Intels Fertigungsguru Mark Bohr wiedersprach Meldungen, dass Intels 22-nm-Prozess gegenüber der 28-nm-Fertigung von TSMC mit Planartransistoren 30-40 % teurer sein würde – realistisch seien vielmehr nur 3 % Mehrkosten bedingt durch die FinFETs. Durch eine minimale Feature-Size von 80 nm könne man die Chips in einem Durchgang mit einem 193-nm-Immersions-Lithografie-Tool bearbeiten.

Auch IMEC-Chef Luc van den Hove, der behauptet hatte, 14-nm-Chips würden durch das Fehlen der EUV-Lithografie sogar 90 % teurer als 28-nm-Chips, wiedersprach Bohr. Das sei nicht mal ansatzweise richtig, zwar würden die Kosten steigen, durch die höhere Transistordichte würden die Kosten pro Transistor jedoch auch bei 14-nm-Fertigung weiter sinken.

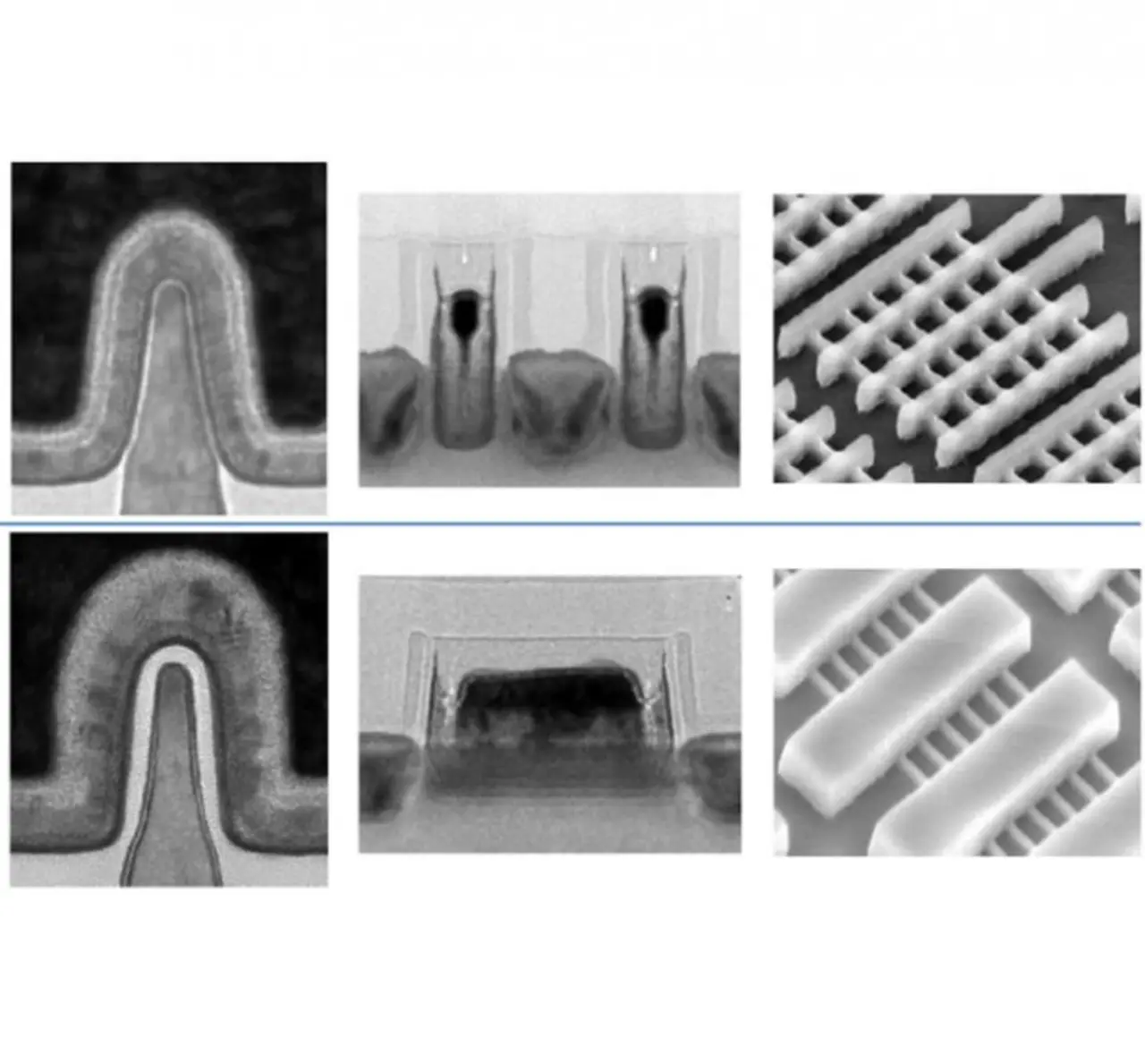

Intels 22-nm-Prozess für System-on-Chips (SoC) wird drei grundsätzlich unterschiedliche Transistor-Typen enthalten (Tabelle), die parallel auf einem Chip zum Einsatz kommen können: High-Speed-Logikl (HP/SP), Low-Power-Logik (LP/ULP) und Hochspannungs-I/O (TG), womit man gleichzeitig die Leckströme auf ca. 10 pA/µm runterbringen und die unterstützten I/O-Spannungen auf über 5 V hochbringen kann. HP/SP und LP/ULP setzen dabei auf die gleiche High-K/Metal-Gate-Dielektrik, während die TG-Transistoren einen spannungstoleranteres Hybrid-SIO2/Higk-K-Gate haben (Bild 1).

Jobangebote+ passend zum Thema

Unterstützt werden dadurch Anwendungen vom Smartphone über Tablets, Netbooks, Embedded-Systeme, Wireless-Anwendungen und ASICs.

Die High-Spped-Transistorfamilie enthält zwei Typen – HP (High-Performance) und SP (Standard-Performance/Power). Die Gate-Länge beträgt 30 bzw. 34 nm und die Leckströme unterhalb der Schwellenspannungen betragen 100 nA/µm bzw. 1 nA/µm. Diese Transistoren sind denen, die schon heute für die Mikroprozessoren in Massenproduktion verwendet werden, sehr ähnlich. Es wird ein DIBL von ca. 50 mV/V für NMOS- und PMOS-Transistoren erreicht.

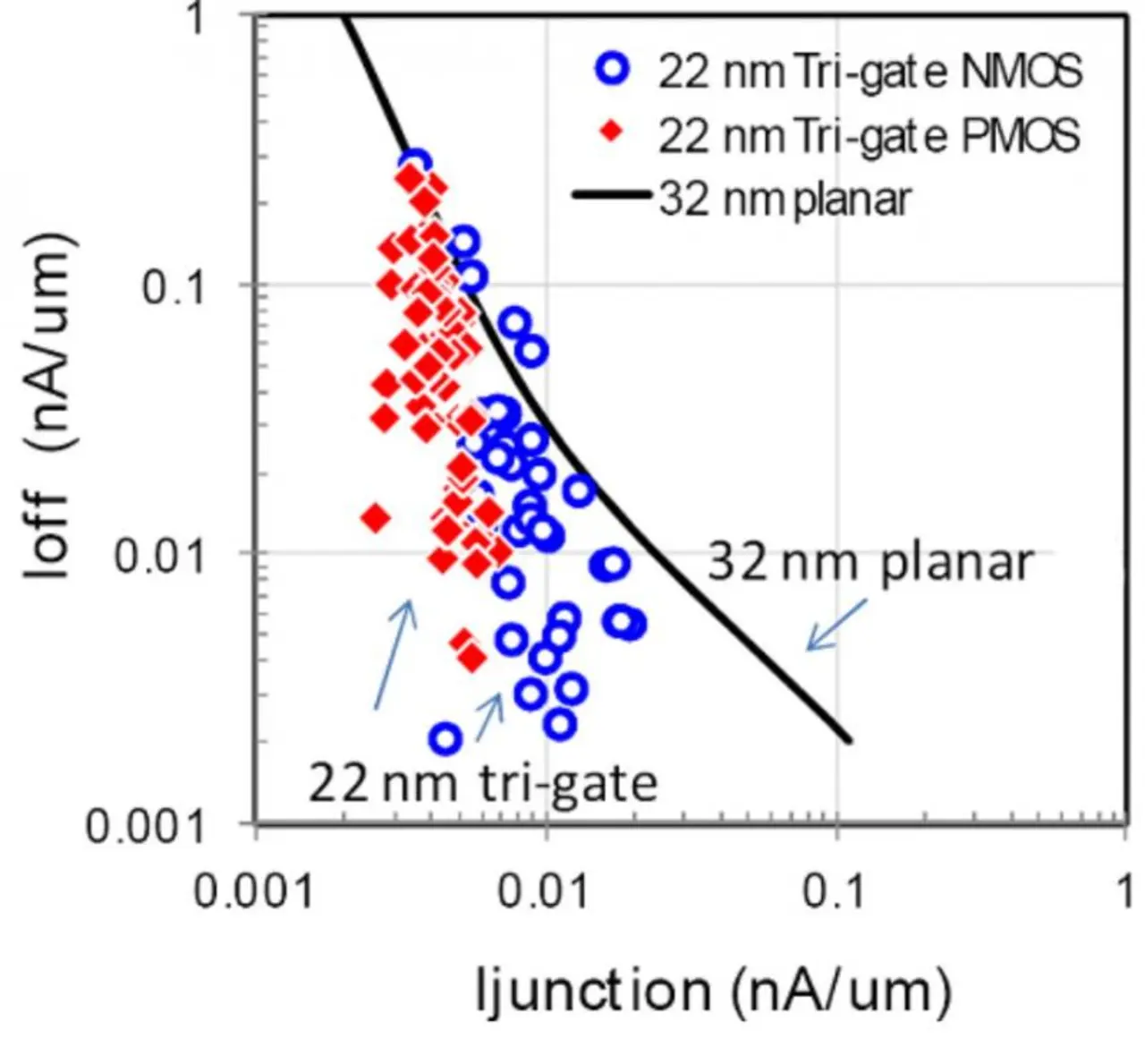

Für Batteriebetriebene Geräte, die immer an sind, sind geringe Leckströme von weniger als 50 pA/µm essentiell. Das Problem bei herkömmlichen planaren Transistoren besteht darin, dass sie hohe Dotierungen im Ladungsträgerkanal und hohe Schwellenspannungen benötigen, um diese Leckströme in den Griff zu bekommen. Derartige Prozesse ergeben eine erhebliche Reduktion in der Ladungsträgermobilität und hohe Sperrschichtleckströme IJunction. Der Gesamtleckstrom eines Transistors ergibt sich ja ungefähr zu

ILeck = 0,5*(IGate,on + IGate,off+Ioff+IJunction)

wobei IGate der Leckstrom zwischen Drain und Gate, Ioff der Leckstrom zwischen Drain und Source und IJunction der zwischen Drain und Sperrschicht darstellt.

Mit den FinFETs kann eine wesentlich geringere Dotierung benutzt werden, durch IJunction fällt durch die vollständige Ladungsträgerverarmung im Fin geringer aus.

| Transistor | HP | SP | LP | ULP | HV 1,8 V | HV 3,3 V |

|---|---|---|---|---|---|---|

| Versorgungsspannung (V) |

0,75/1 | 0,75/1 | 0,75/1 | 0,75/1,2 | 1,5/1,8/3,3 | 3,3/>5 |

| Gate-Abstand (nm) | 90 | 90 | 90 | 108 | >=180 | >=450 |

| Gate-Länge (nm) | 30 | 34 | 34 | 40 | >=80 | >=280 |

| NMOS/PMOS Idsat/Ioff (mA/µm) | 1,08/0,91 @ 0,75 V, 100 nA/µm | 0,71/0,59 @ 0,75 V, 1 nA/µm | 0,41/0,37 @ 0,75 V, 30 pA/µm | 0,35/0,33 @ 0,75 V, 15 pA/µm | 0,92/0,8 @ 1,8 V, 10 pA/µm | 1,0/0,85 @ 3,3 V, 10 pA/µm |

Charakteristika der unterschiedlichen Transistortypen bei Intels 22-nm-FinFET-Prozess.

- Intel zeigt ersten 22-nm-SoC-Prozess mit FinFETs und wiederspricht IMEC

- Verbesserungen um 50 Prozent gegenüber 32-nm-Prozess