IEDM 2012

Intel zeigt ersten 22-nm-SoC-Prozess mit FinFETs und wiederspricht IMEC

Fortsetzung des Artikels von Teil 1

Verbesserungen um 50 Prozent gegenüber 32-nm-Prozess

Mit 0,41/0,37mA/µm bei 30pA und 0,75V (NMOS/PMOS) wurden gegenüber Intels 32-nm-Planar-SoC-Prozess Verbesserungen von 50 % erzielt. Dies ist mehr als doppelt soviel Zuwachs wie es typisch bei einem neuen Prozess-Node ist. Intel erklärt sogar, dass es sich um die besten Werte handelt, die unter diesen Betriebsbedingungen jemals erzielt wurden.

Die ULP-Transistoren unterschieden sich von den LP-Transistoren dahingehend, dass ihr Gate-Abstand von 90nm auf 108nm und die Gate-Länge von 34nm auf 40nm verlängert wurden. Dies führt zu einer DIBL von nur noch 30-40mV/V. Die Schwellenspannung konnte im Vergleich zu den 32-nm-Planartransistoren um immerhin 100 mV abgesenkt werden. Bild 2 zeigt die Verbesserungen hinsichtlich von IJunction.

Um I/Os, analoge Schaltkreise, Spannungsregler und Kommunikationsanwendungen zu unterstützen, braucht man auf einem SoC auch spezielle Hochspannungs-Transistoren. Mit einer High-K/Oxid-Gate-Dielektrik ausgestattet gibt es 1,8- und 3,3-V-Transistoren. Mit 0,92/0,8 mA/µm bei 1,8 V und 10 pA/µm Ioff (NMOS/PMOS) wurden die Werte aus Intels eigenem 32-nm-Prozess um 51 bzw. 56 % (NMOS/PMOS) verbessert. Auch hierzu sagt Intel, die besten Zahlen für ein SoC überhaupt erreicht zu haben.

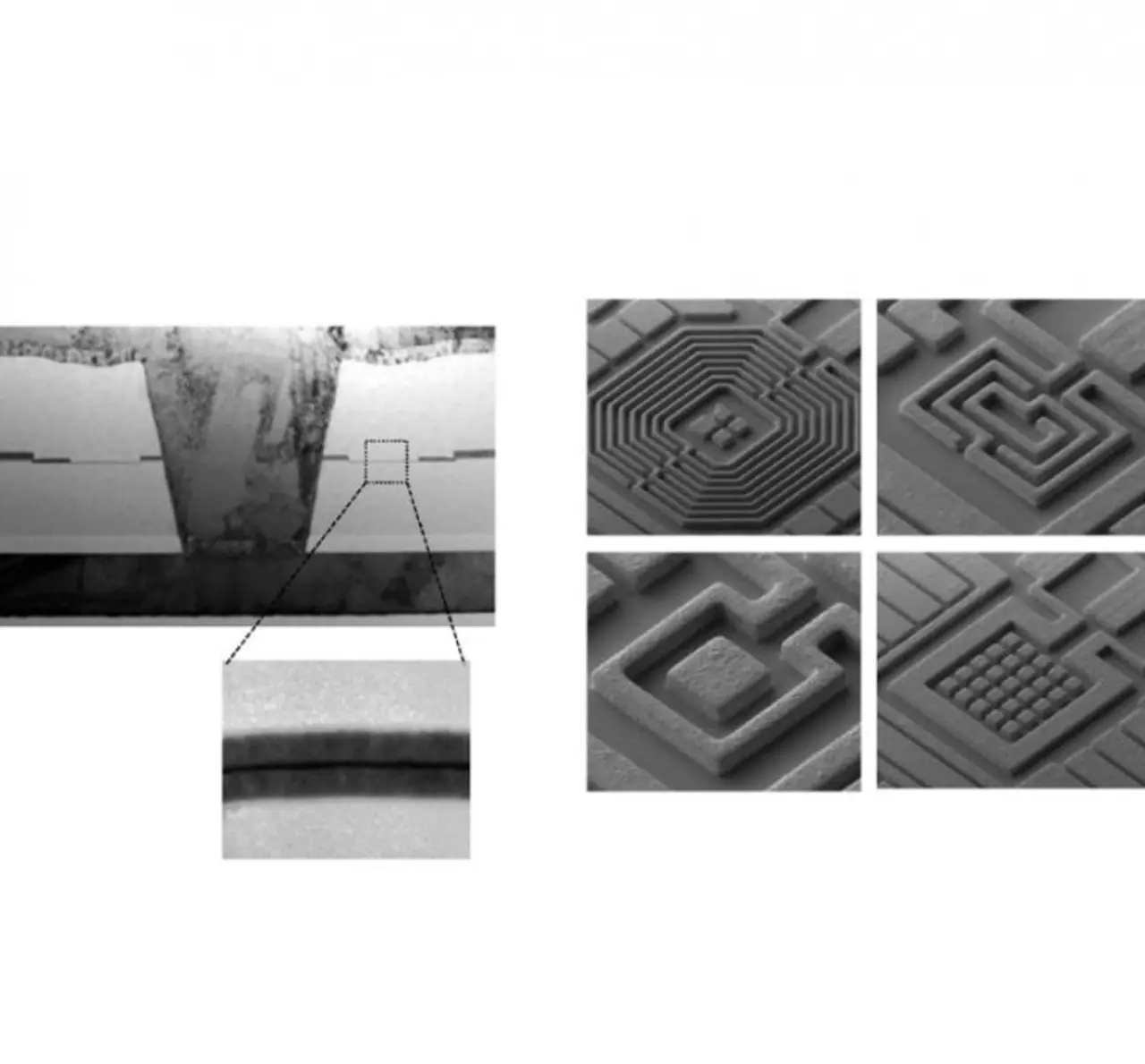

Neben den Transistoren bietet Intel auch eine Bibiothek mit diversen Analog-Komponenten inklusive Präzisions-Widerständen (fertigungsbedingte Abweichungen < 15 %), Kapazitäten in einer neuen MIMCAP genannten Technologie (Bild 3, links) und in Spiralform ausgeführte sogenannte High-Q-Induktivitäten (Bild 3, rechts).

Jobangebote+ passend zum Thema

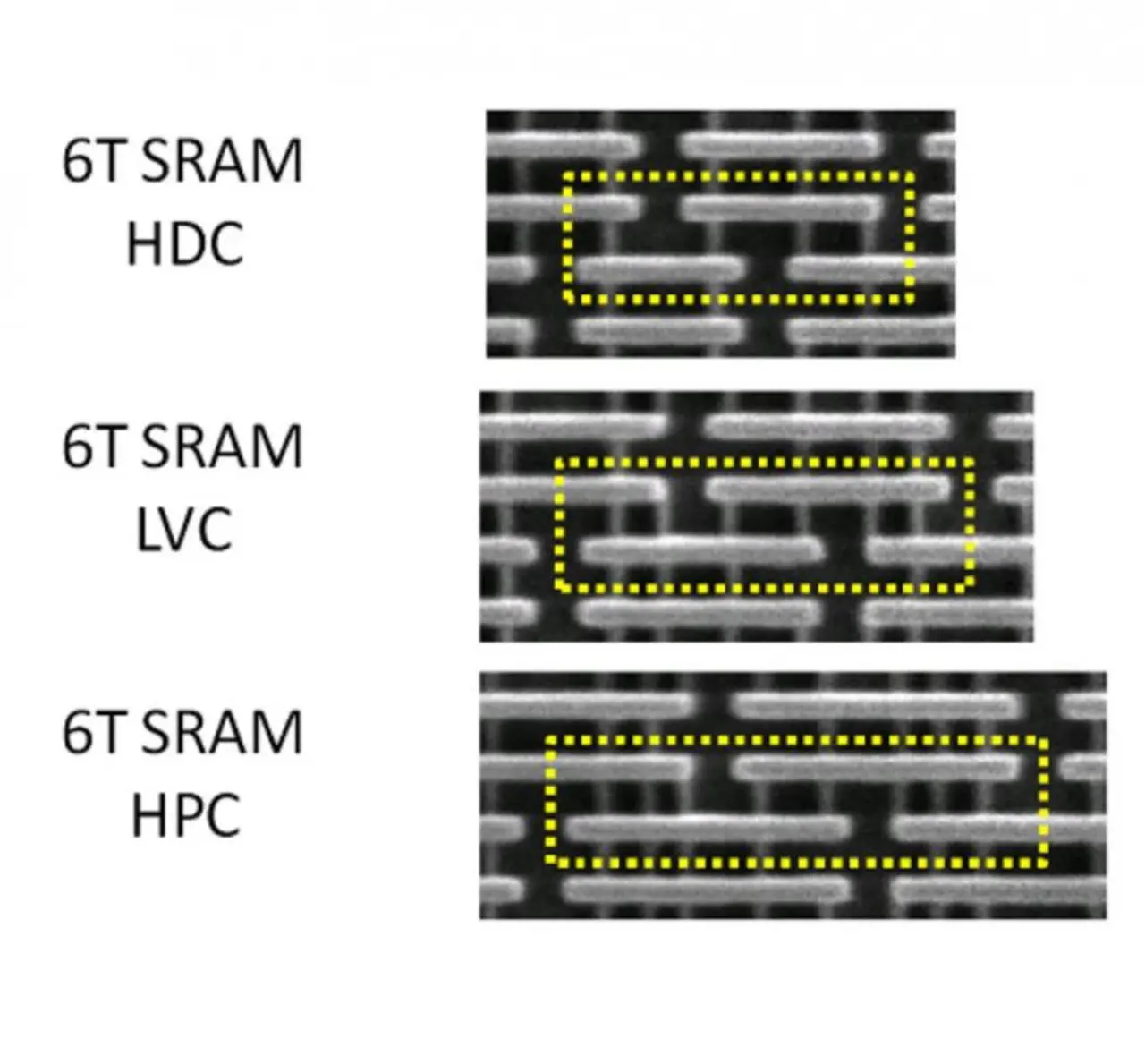

Last but not least warden diverse SRAMs in Single- und Dual-Port-Ausführung angeboten (Bild 4). Die Single-Port-SRAMs beinhalten Zellen mit hoher Integrationsdichte und geringem Leckstrom (0,092µm2 Fläche, HDC), geringe Versorgungsspannung (0,108 µm2 Fläche, LVC) und hohen Datendurchsatz (0,130µm2, HPC).

Die Optionen für Dual-Port-SRAMs beinhalten synchrone und asynchrone Zelltypen. Durch den 22-nm-FinFET-Aufbau wurde bei 1 V Spannung für HDC-LP-SRAM bezüglich des Leckstroms gegenüber der 32-nm-Fertigung eine Verbesserung um Faktor 4 erzielt – von knapp 200 pA/Zelle aus rund 50 pA/Zelle.

Die Taktfrequenzen für SRAM konnten bei 1 V für HP-, SP- und LP-Prozesse um 40 % auf 4,6, 3,5 und 2,6 GHz angehoben werden. Braucht man keine höhere Taktfrequenz, kann alternativ die Versorungsspannung abgesenkt werden, bei 800 MHz und einem PL-Prozess z.B. von 0,75 auf nur noch 0,6 V.

- Intel zeigt ersten 22-nm-SoC-Prozess mit FinFETs und wiederspricht IMEC

- Verbesserungen um 50 Prozent gegenüber 32-nm-Prozess