Safety Industrie

In weniger Schritten zur Zertifizierung

Fortsetzung des Artikels von Teil 2

Von der Wahl der Komponenten bis zur Integration

Architekturentwicklung

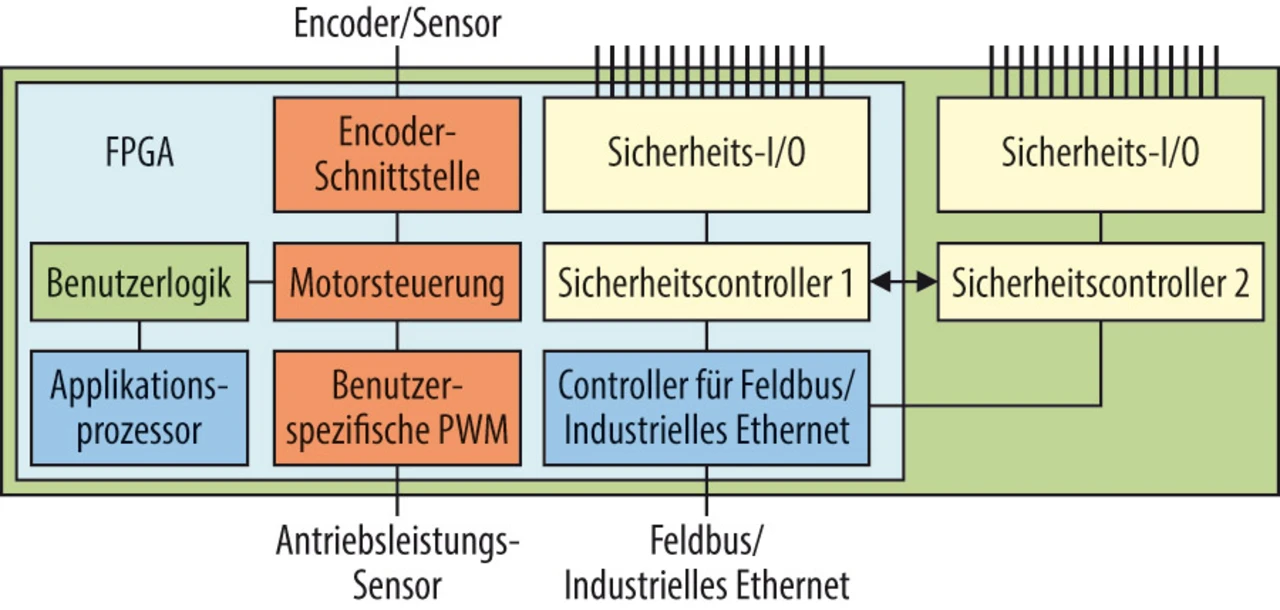

Nach diesem Schritt wird die Architektur der Applikation so entwickelt, dass sie die funktionalen Anforderungen ebenso erfüllt wie die Sicherheitsanforderungen (Bild 4).

Jobangebote+ passend zum Thema

Die Sicherheitsanforderungen werden weiter verfeinert, und die während des Betriebs und der Instandhaltungsarbeiten zu realisierenden spezifischen Funktionen werden dokumentiert. Zusätzlich werden Strategien bestimmt, die befolgt werden müssen, um zu validieren, dass die Sicherheitsmaßnahmen den Anforderungen entsprechen.

Validierungs- und Verifikationsplan

Bei der Entwicklung des Validierungsplans können Methoden zum kontrollierten Einfügen von Fehlern zum Einsatz kommen. Dies dient dem Test des Systems selbst sowie zusätzlicher Überwachungseinheiten, die das System beobachten und überprüfen, ob die Ist-Parameter im zulässigen Wertebereich liegen. In der IEC 61508:2010 ist festgelegt, welche Techniken oder Maßnahmen anzuwenden sind, um einen bestimmten SIL (Safety Integrity Level) zu erreichen. Während der Design-phase wird eine ‚skriptbasierte Prozedur‘ empfohlen, wenn ein SIL von 2 angestrebt wird. Dringend empfohlen wird die gleiche Methode auch für SIL-3-Anwendungen, weil dieser SIL verglichen mit SIL 2 einen größeren Umfang an Techniken und Maßnahmen erfordert. Für diesen Zweck vorgeschlagen wird der sogenannte Ablauf „Tool Command Lan-guage“ (Tcl). Altera hält detaillierte Informationen darüber bereit, wie die Anforderungen der IEC 61508:2010 erfüllt werden können. Dazu gibt es eine Liste mit Techniken und Maßnahmen, die das Einschleichen von Fehlern während des Designs und der Entwicklung verhindern. Beim FSDP von Altera ist die Auswahl der Maßnahmen und Techniken bereits erledigt und dokumentiert, so dass diese unmittelbar für die Verwendung durch das Entwicklungs-Team bereitstehen. Dies hilft beim Verständnis der Anwendung der Methoden, speziell wenn es um die Realisierung des allerersten sicherheitsrelevanten FPGA-Projekts geht. Darüber hinaus sind diese Methoden klar mit Tools verknüpft, die die Methoden implementieren. Damit keine notwendigen Dokumente und Designschritte übersehen werden, enthält das FSDP von Altera genaue Checklisten. Diese helfen den Entwicklungs-Teams, dafür zu sorgen, dass die erforderlichen Input- und Output-Dokumente für alle Phasen des Lebenszyklus vorliegen. Zusätzlich ist eine Reihe von Lebenszyklus-Aktionen definiert, mit denen die vollständige Durchführung aller Phasen verifiziert wird. Da diese Checklisten bereits vom TÜV zertifiziert sind, sind keine weiteren Arbeiten nötig, um nachzuweisen, wie die korrekte Anwendung des V-Modells im FSDP von Altera garantiert wird.

Wahl der Komponenten und Qualifikation von Komponenten, IP und Tools

Die Komponentenauswahl erfolgt wie in einem typischen Projekt. Zusätzlich muss aber sichergestellt sein, dass jede Komponente samt der zugewiesenen und ausgewählten IP-Funktionen für den Einsatz in einer sicheren Anwendung geeignet ist. Für die Auswahl ist es wichtig, die Rest-Ausfallwahrscheinlichkeit in Betracht zu ziehen, denn diese dient als Grundlage zur Berechnung der Gesamt-Fehlerwahrscheinlichkeit (FIT) eines Produkts sowie letztlich auch des erreichbaren SIL. Dies kann zum Teil durch Zusammenstellen der erforderlichen Device- und Design-Tool-Daten und Informationen erreicht werden. So lässt sich sicherstellen, dass die Produkte, wenn sie in großem Umfang von einem breiten Anwenderspektrum eingesetzt werden, hinreichend frei von systematischen Fehlern sind oder sich im praktischen Einsatz bewährt haben (beispielsweise im Fall von IP). Erreicht werden kann dies außerdem durch den Zugang zu Berichten, die Fehlerraten sowie Zuverlässigkeits-informationen zu Halbleiterprodukten wie etwa Prozessoren oder FPGAs enthalten. Allerdings ist es häufig schwierig, Zuverlässigkeitsberichte zu Bauteilen und Halbleiterprodukten zu bekommen, die die nötigen Informationen enthalten. Dies gilt insbesondere für die zugehörigen Design Tools und das in der Applikation eingesetzte IP.

Implementierung des Applikations--Designs

Komplexe Systemfunktionen wie etwa Kommunikationsprotokolle, im FPGA verwendete Speicherschnittstellen-IP oder in das FPGA eingebettete IP (z.B. der Embedded-Prozessor Nios II von Altera zur Verarbeitung des Software Stack für industrielle Ethernet-Protokolle in Antriebs-Applikationen) müssen für Sicherheitsarbeiten ebenfalls analysiert, geprüft und qualifiziert werden.

Zusätzlich zur Implementierung der Applikation muss das Design durch einen bestimmten Umfang an zusätzlichen Funktionen ergänzt werden. Erforderlich sind beispielsweise Funktionen zur Überwachung bestimmter elementarer Parameter (z.B. Takt- und Stromversorgung), aber auch komplexe Funktionen wie etwa Datenmonitor-Funktionen zur Gewährleistung eines korrekten Systembetriebs, indem beispielsweise der Ausgang eines Pulsweitenmodulators (PWM) überwacht wird. Notwendig ist die Implementierung von Funktionen, die Fehler automatisch erkennen und das System in einen sicheren Zustand versetzen. Zu den elementaren Überwachungsfunktionen gehören beispielsweise die Überprüfung, dass sich der Speicherinhalt nicht durch externe Einflüsse geändert hat, und die Überwachung der Systemtakte, um zu gewährleisten, dass sie das Design innerhalb der vorgegebenen Systemparameter ansteuern (bzw. dass kein Fehler infolge des Ausfalls externer Komponenten vorliegt) und dass die Stromversorgungen in Betrieb sind.

Hinzufügung fertig qualifizierter -Sicherheit

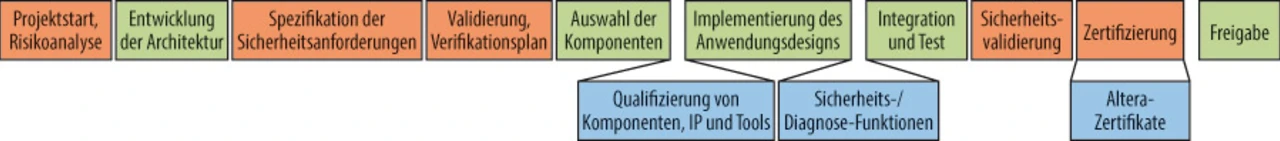

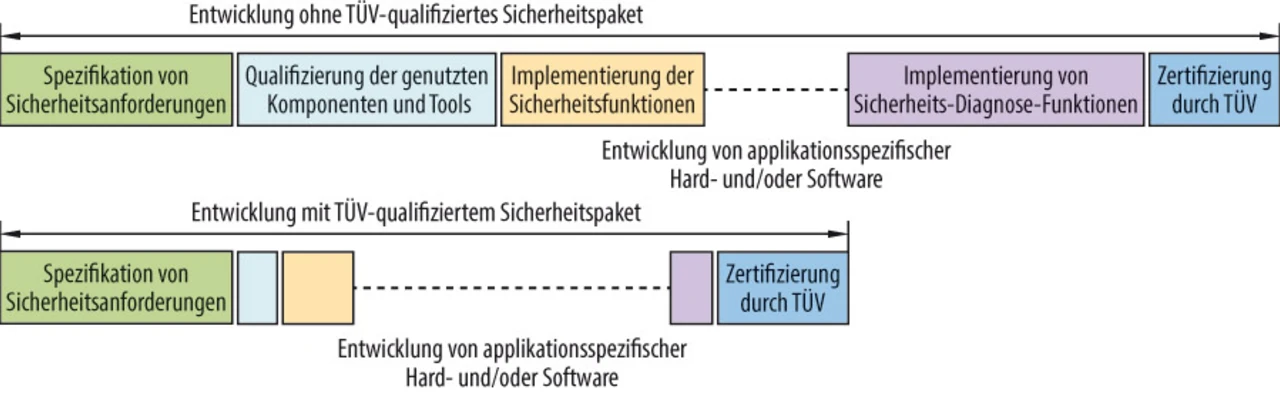

Bei bestimmten Schritten können Halbleiterhersteller wie Altera Hilfestellung leisten und den Aufwand zur Entwicklung sicherer Anwendungen verringern. Zum Beispiel kann der umgehende Zugang zu Halbleiter-Daten, IP, Entwicklungs-Abläufen und Design-Tools, die bereits für Funktionssicherheit qualifiziert sind, den gesamten Entwicklungsprozess deutlich beschleunigen (Bild 5). Altera hat in die Qualifikation seiner Produkte nahezu zwei Jahre investiert. Die erforderlichen Prüf- und Nutzungsdaten für IP und Design-Tools sowie die Zuverlässigkeitsdaten der Bauelemente sind so zusammengefasst und formatiert, dass sie bei der Funktionssicherheits-Zertifizierung vorgelegt werden können. Wichtige Diagnosefunktionen sind als FPGA-IP konzipiert und gehören zum Umfang des Funktionssicherheits-Pakets. Dessen Nutzer profitieren von den Investitionen und können in ihren Projekten ähnlich viel Zeit sparen (Bild 6).

Integration und Test

Sind die einzelnen Komponenten entwickelt, werden sie zu einem sicheren Antrieb integriert und daraufhin geprüft, ob sie die erwarteten Systemfunktionen und die spezifizierte Sicherheits-Funktionalität bieten. Die Sicherheitsvalidierung muss sicherstellen, dass die angestrebten Sicherheitsmerkmale wirksam sind und dies auch während des Betriebs bleiben. Unter anderem muss gewährleistet sein, dass externe Einflüsse auf das Design keine negativen Auswirkungen auf die Sicherheitsfunktionen haben (indem sie diese beispielsweise deaktivieren, ohne dass dies vom System bemerkt wird).

Validierung, Zertifizierung und Freigabe der Sicherheitsfunktion

Während des gesamten Prozesses ist eine enge Zusammenarbeit mit dem Prüfer erforderlich, um sicherzustellen, dass die während des Entwicklungsprozesses durchgeführten Maßnahmen sinnvoll sind und das richtige Maß an sicherer Funktionalität ergeben. Abschließend zertifiziert der Prüfer die Funktionssicherheit des Produkts, das damit auf den Markt gebracht werden kann.

Die Durchführung des ersten Funktionssicherheits-Projekts mag mit mehr Aufwand verbunden sein, als es für die meisten standardmäßigen Projekte üblich ist. Da die Prozesse, Kennzahlen und Techniken von den Funktionssicherheits-Standards jedoch detailliert vorgegeben werden, kann man von einem hohen Wiederverwendungsgrad ausgehen. Eine gründliche Untersuchung der existierenden Tools, Qualitätskennzahlen und Ressourcen wird weitere Vorteile und Vereinfachungen mit sich bringen, wenn in einem Unternehmen ein neuer Applikationsentwicklungs-Prozess für Sicherheitsprojekte etabliert werden soll. FPGAs bieten Designflexibilität und werden hinsichtlich der Funktionssicherheit unterstützt, da Altera bereits vorab in Methoden, qualifizierte Tools und Bauelemente sowie qualifiziertes IP und Diagnose-IP investiert hat.

Da das V-Modell ein entscheidendes Element des gesamten Funktionssicherheits-Projekts ist, kommt es darauf an, diesem Bestandteil viel Zeit zu widmen. Die Möglichkeit, erprobte Methodiken und ein validiertes V-Modell für FPGAs von Altera wiederzuverwenden, kann in dieser Phase des Projekts hilfreich sein. Die klare Definition und das Verstehen des geplanten Systems und die Wiederverwendung fertig qualifizierter Technologie wird sehr schnell zu einem erfolgreichen Abschluss des Projekts führen.

Wolfgang Kattermann arbeitet als Market Development Manager für Industrie-Anwendungen bei Altera.

WKatterm@altera.com

- In weniger Schritten zur Zertifizierung

- Funktionale Sicherheit gemäß IEC 61508 und V-Modell

- Von der Wahl der Komponenten bis zur Integration