Einfach fallen lassen

Fortsetzung des Artikels von Teil 4

Einfach fallen lassen

Um die Anzahl der Pins in Grenzen zu halten, erfüllt fast jeder Pin an einem modernen Controller mehrere Zwecke. Eine Nebenwirkung dieser Funktionsbündelung besteht darin, dass jeder Pin eine andere interne Laufzeitverzögerung haben kann. Wenn nicht jede Verzögerung für sich kontrolliert wird, ist es wahrscheinlich, dass wenigstens ein Adresspin etwas langsamer als Chipselect ist. Erschwerend kommen auch externe Faktoren hinzu: Es ist gängige Systemdesign-Technik, den Adressbus von Speicher und/oder Peripherie gemeinsam nutzen zu lassen, während Peripheriekomponenten die Chipselects normalerweise nicht gemeinsam nutzen. Auch wenn die Adressen dem vom Controller kommenden Chipselect-Signal vorausgehen, kann diese Timing-Beziehung an den Pins der Speicherkomponente verloren gegangen sein. Ein asynchrones SRAM betrachtet einen Address-Skew (Versatz) als Verringerung der erforderlichen Zugriffszeit, was die Funktionsweise jedoch nicht berührt. Für pseudostatische Speicher ist das relative Timing zwischen Chipselect und langsamster Adresse allerdings ein kritischer Parameter, wie gleich gezeigt werden soll.

Jobangebote+ passend zum Thema

Relativ pünktlich

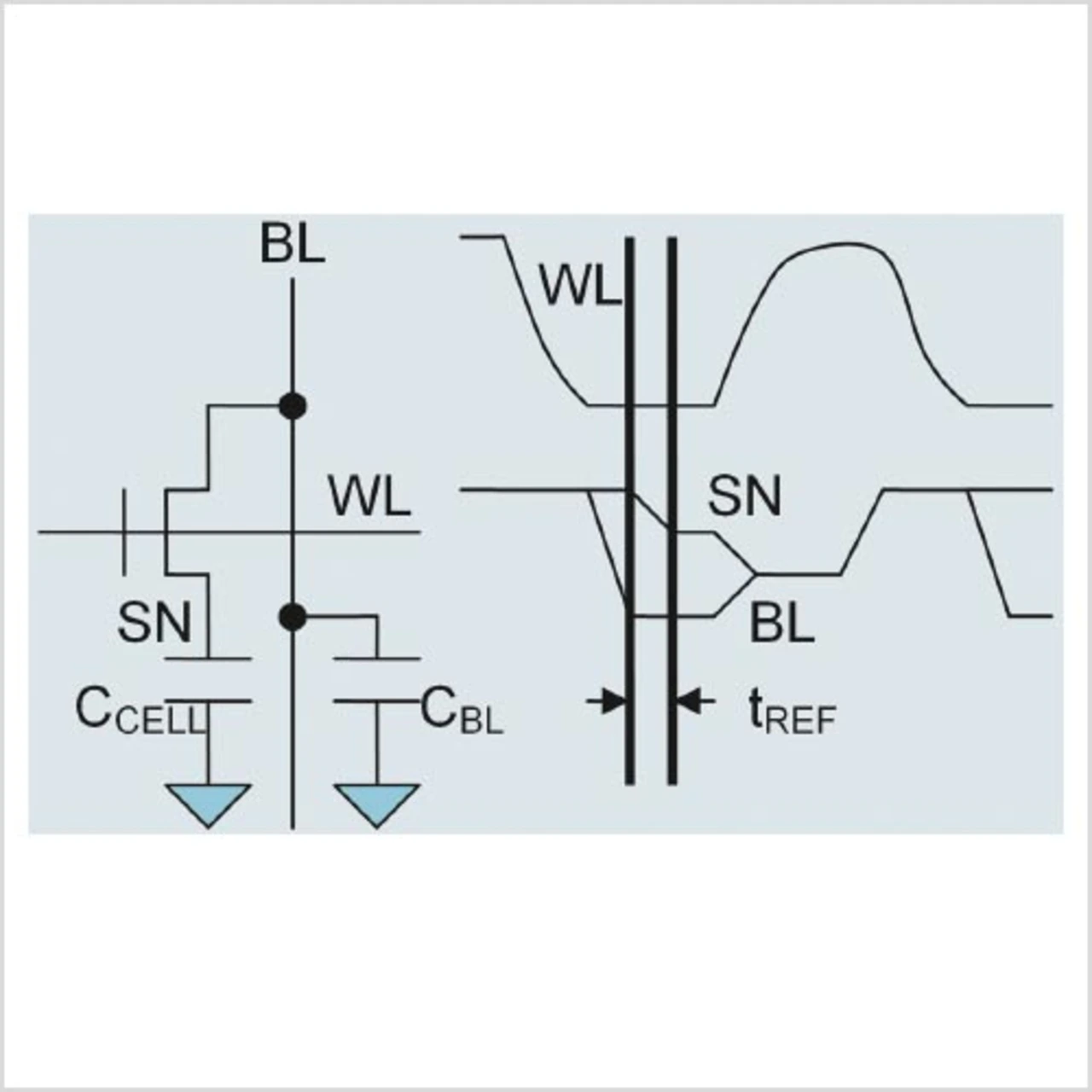

Intern arbeitet PSRAM wie dynamisches RAM (DRAM) in dem Sinne, dass der Speicher laufend im Hintergrund aufgefrischt werden muss, um den Speicherzustand aufrecht zu erhalten. Des Weiteren beeinträchtigt der Vorgang des Lesens einer PSRAM-Zelle das Signal in dieser Zelle, und es dauert seine Zeit, den Datenzustand abzutasten und das Signal wieder auf den vollen Pegel zurückzusetzen. Wie in Bild 3 vereinfacht dargestellt, speichert eine DRAM-Zelle Daten durch Festhalten der Ladung auf dem Speicherknoten (SN) des Zellenkondensators (CCELL).

Ein Transistor dient als Schalter, um den Zugriff auf die Zelle zu kontrollieren. Viele Zellen teilen sich dieselbe Bitleitung, und die parasitische Kapazität jedes Transistor-Drains zusätzlich zur parasitischen Metallkapazität bewirkt eine Nettokapazität, die in Bild 3 als CBL bezeichnet ist. Die in der Zelle gespeicherte Ladung fließt im Laufe der Zeit langsam über den Zugriffstransistor und Zellenkondensator ab. Die Spannung am Speicherknoten muss aufgefrischt werden, bevor das Signal unter den erfassbaren Pegel absinkt. Diese Auffrischzeit ist in der Abbildung als tREF bezeichnet. Beim Auslesen oder Auffrischen der Zelle steigt die Spannung in der Wortleitung (WL). Die im Speicherknoten verbleibende Ladung verteilt sich auf CCELL und CBL. Dann wird die Spannung auf der Bitleitung abgetastet, um zu bestimmen, ob die Zelle einen Datenzustand von 1 oder 0 enthielt. Darauf findet die volle Wiederherstellung der mit diesem Datenzustand assoziierten Spannung auf dem Spannungsknoten statt.

- Einfach fallen lassen

- Einfach fallen lassen

- Maskerade

- Einfach fallen lassen

- Einfach fallen lassen