Einfach fallen lassen

Fortsetzung des Artikels von Teil 2

Maskerade

Zwar spezifizieren die Controller-Datenblätter die Größenordnung der erforderlichen negativen Setup-Zeit nur selten, so dass sie eigentlich für jedes System individuell charakterisiert werden müsste, in den allermeisten Designs liegt sie jedoch unter 5 ns. Geht man von diesem Wert aus, so besteht der Nachteil bei diesem einfachen Ansatz darin, dass er den Beginn des Speicherzugriffs verzögert und daher unmittelbar die Zugriffszeit verlängert. Die Verzögerung, die erforderlich ist, um unter schnellen Bedingungen eine Adressen-Setupzeit von -5 ns zu garantieren, kann die Zugriffszeit unter langsamen Bedingungen um bis zu 12 ns verlängern. Entsprechend können Lieferanten von pseudostatischem Speicher unterschiedliche Geschwindigkeitsgrade anbieten – je nachdem, ob die Verzögerung an der fallenden Flanke des Chip-Enable-Signals freigegeben ist oder nicht. So arbeitet der parallele 4-Megabit-FRAM-Speicherchip »FM22 L16« von Ramtron normalerweise mit einer Zugriffszeit von 55 ns, wenn eine Adressen-Setup-Zeit von 0 ns garantiert werden soll. Auf Anfrage lässt sich eine testprogrammierbare Option aktivieren, welche die Adressen-Setupzeit auf -5 ns setzt, wobei sich als Nebenwirkung die Zugriffszeit allerdings auf 70 ns erhöht.

Jobangebote+ passend zum Thema

Tatsächlich ist die pseudostatische ATD-Implementierung viel einfacher und sicherer als die komplett asynchrone in SRAMs. Jeder Entwickler von Speicherchips kennt wenigstens eine Horrorstory über eine fehlerhafte ATD-Implementierung. Da jeder in einem pseudostatischen Speicher gestartete Zugriff auch beendet werden und die Voraussetzung eines negativen Adressen-Setups erfüllt sein muss, besteht ATD nur noch in einem einfachen Vergleich der Adressen an den Inputs, wenn der interne Lesevorgang abgeschlossen ist, mit den Adressen, die intern zu Beginn des Zugriffs gelatcht wurden.

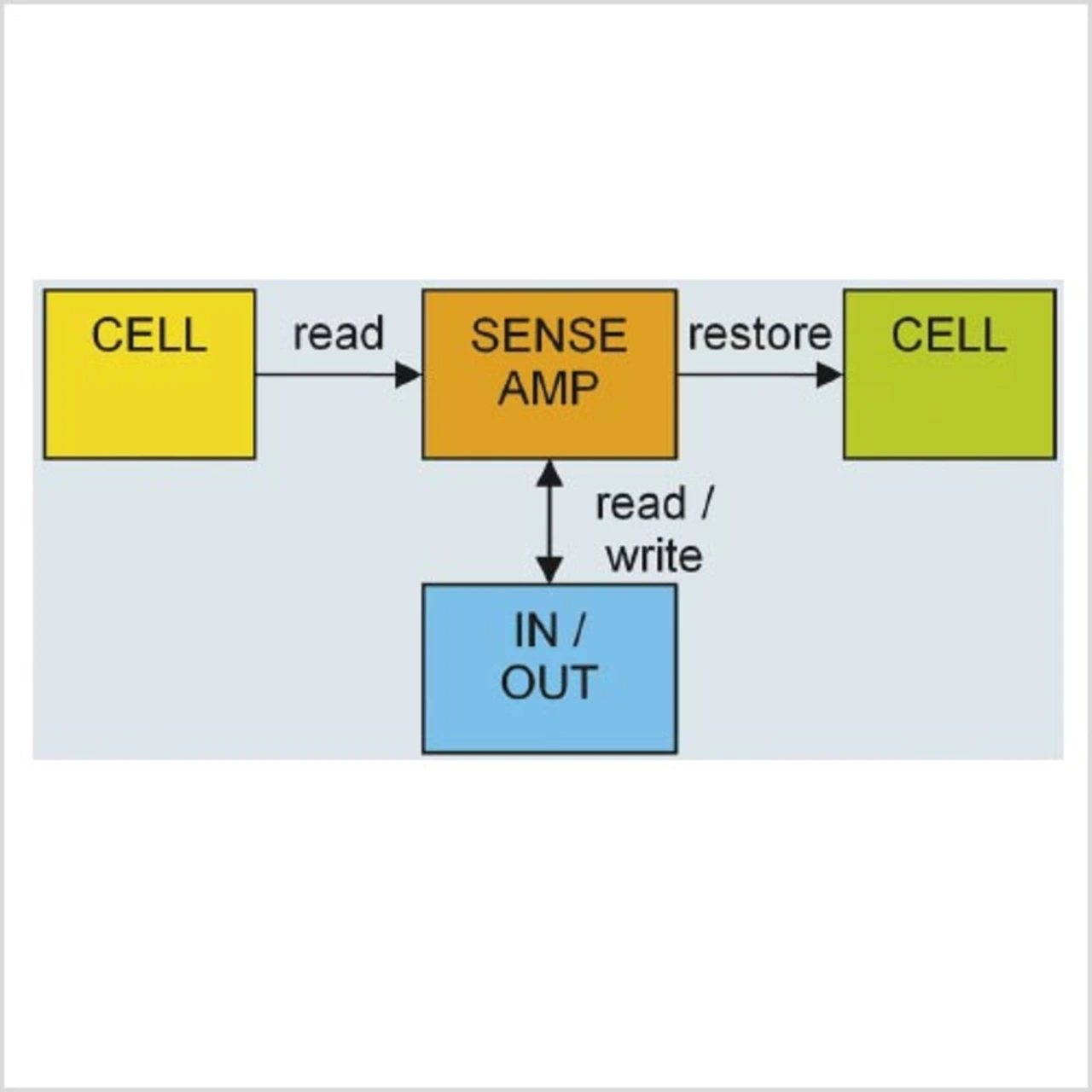

In einem FRAM-Chip ist der interne Zugriff in eine Leseund eine Rückschreibphase aufgeteilt. Dies geschieht aus zwei Gründen. Erstens ist da die SRAM-Forderung auf Kompatibilität mit spätem Schreiben, die mit der Möglichkeit zu tun hat, dass der /WE-Input erst nach /CE fällt oder sich Daten ändern, nachdem /WE gefallen ist. Zweitens ist der interne Datenbus gewöhnlich breiter als der externe Bus. Bei einem internen Bus von 64 Bit und einem externen Bus von 16 Bit gibt es auch bei Schreibzyklen 48 zusätzliche Bits, die zu lesen und wiederherzustellen sind. Dazu beginnen und arbeiten alle FRAM-Zugriffe als Lesevorgang bis zu dem Punkt, an dem die von den internen Sensorverstärkern gelatchten Daten mit dem externen Datenpfad verbunden sind. Bei einem Lesevorgang werden die Sense-Amp-Daten auf die Datenpins des Speicherchips geleitet. Bei einem Schreibvorgang laufen die Daten von den Datenpins des Speicherchips in den Sense-Amp. Die Richtung des Datenflusses ist demnach der einzige Unterschied zwischen Lesen und Schreiben. Der Wiederherstellungs- bzw. Rückschreibvorgang arbeitet in beiden Fällen in gleicher Weise, wobei die im Sense-Amp gelatchten Daten in die Zelle zurückfließen. Bild 6 illustriert den Datenfluss bei einem FRAM-Zugriff.