Einfach fallen lassen

Fortsetzung des Artikels von Teil 1

Einfach fallen lassen

Das interne cebint-Signal ist – wie bereits erklärt – gegenüber dem externen /CESignal geringfügig verzögert. Sobald die Lesephase des Zugriffs beginnt, werden die Adressen intern gelatcht. Das Latch-Kontrollsignal ist als alatch und die gelatchten Adressen als la[n:0] bezeichnet. Vor Abschluss der Lesephase wird jede Änderung in externen Adressen ignoriert. Ist die Lesephase abgeschlossen – wie vom datardy-Signal (Data Ready) angezeigt – geht das atd-Signal auf High, sobald der externe A[n:0]-Bus vom internen la[n:0]-Bus abweicht. In Bild 7 hat sich die externe Adresse vor dem Anstieg von datardy geändert, so dass das atd-Signal unmittelbar nach datardy auf High geht.

Jobangebote+ passend zum Thema

Sobald das atd-Signal einen Adressenübergang anzeigt, wird das interne cebint-Signal auf High gesetzt, um die Rückschreibphase zu starten. Wenn die Rückschreibphase abgeschlossen ist, geht die Kontrolle von cebint an den externen /CEPin zurück. Falls /CE immer noch Low ist, beginnt ein neuer Zugriff auf die bei Abschluss der Rückschreibphase aktuelle Adresse. Bei dieser Implementierung dient die Memory-Rückschreibzeit dazu, auch die Address-Skew-Zeit unterzubringen. Die schnellste Adresse initiiert ATD, und die langsamste Adresse hat die gesamte Speicher-Rückschreibzeit, um anzukommen. Die meisten pseudostatischen Speicherchips tolerieren Skew-Zeiten von Adresse zu Adresse von mehr als 10 ns und sogar bis 20 ns.

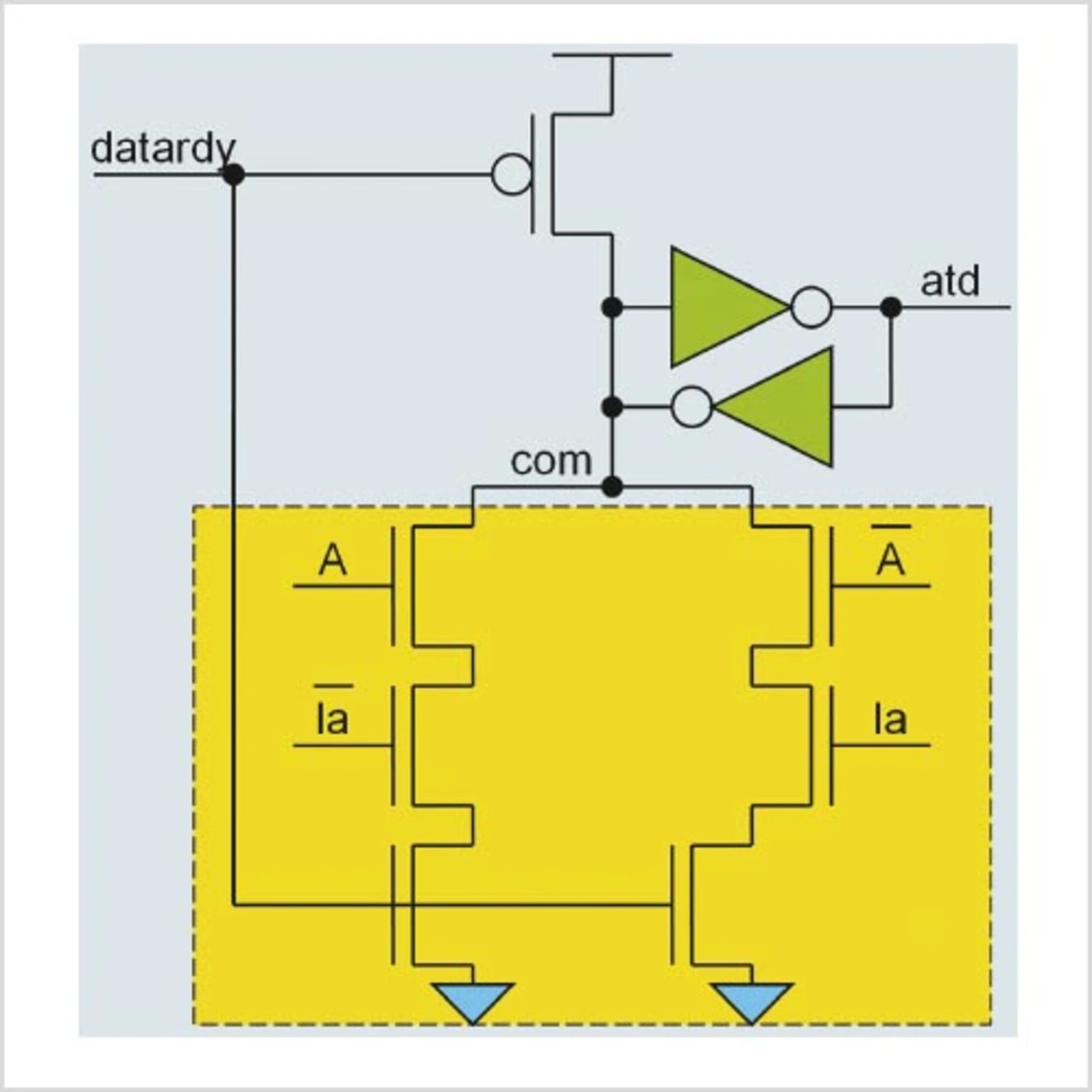

Die Adressenvergleichsschaltung selbst ist sehr einfach, wie Bild 8 zeigt. Der Einfachheit halber ist hier nur ein Bit des Adressenvergleichs dargestellt. Für jedes Adressenbit wiederholt sich die Schaltung innerhalb des gestrichelten Umrisses. Das gemeinsame Vergleichssignal (com) ist auf High vorgeladen, und der Entladungspfad wird unterbrochen, wenn das datardy-Signal auf Low steht. Wenn datardy auf High geht, wird der Entladungspfad freigegeben. Sind A und la jedoch gleich, ist je ein NMOS-Transistor auf jeder Seite ausgeschaltet und das com-Signal bleibt High, während das atd-Signal Low bleibt. Wenn A und la unterschiedlich werden, sind alle drei NMOS-Transistoren auf einer Seite eingeschaltet und entladen den com-Knoten, was wiederum das atd-Signal auf High latcht. (Dr. Marcel Consée)

| Jarrod Eliason ist Senior Design Engineer bei Ramtron International | |

| Telefon 00 44/13 44 39 27 85 | www.ramtron.com |

- Einfach fallen lassen

- Einfach fallen lassen

- Maskerade

- Einfach fallen lassen

- Einfach fallen lassen