Einfach fallen lassen

Fortsetzung des Artikels von Teil 3

Einfach fallen lassen

Nach der Ladungsverteilung und vor der Wiederherstellung kann die auf dem Speicherknoten verbleibende Spannung unter den abtastbaren Pegel fallen. Wird der Zugriff innerhalb dieses kritischen Zeitfensters abgebrochen, könnte der nachfolgende Zugriff auf das gleiche Bit falsch abgetastet werden. Daher gilt der Vorgang des Auslesens eines DRAMs als destruktiv. Hat der Zugriff auf ein DRAM erst einmal begonnen, muss er vollständig zu Ende geführt werden. Ein DRAM ist nicht in der Lage, das in Bild 1 dargestellte Szenario laufender Adressänderungen so zu bewältigen wie ein SRAM. Allerdings kann ein DRAM so konzipiert sein, dass es die endlichen Timing-Unsicherheiten bewältigt, die in den meisten Controllerbasierten Systemen vorkommen. FRAM ist von Natur aus nichtflüchtig und erfordert kein ständiges Auffrischen, jedoch gibt es hier – wie bei DRAM – destruktives Lesen, und es lassen sich gängige Techniken einsetzen, um einfach zu verwendendes pseudostatisches FRAM zu bilden.

Jobangebote+ passend zum Thema

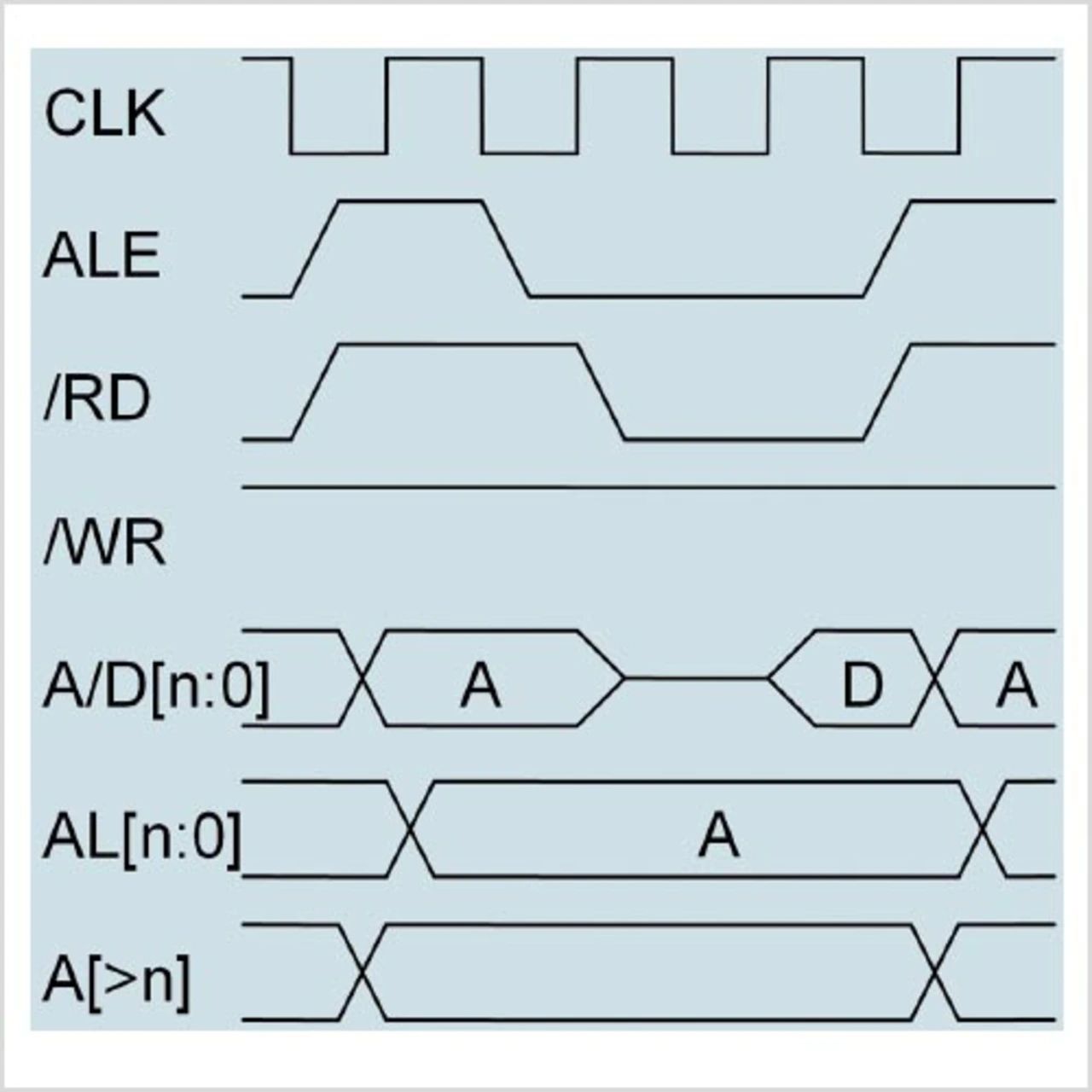

Bild 4 zeigt einen weiteren gern verwendeten Weg, wie Controller die ATD-Eigenschaft von SRAM nutzen. Viele Controller bündeln die Adressund Datenleitungen, um die Anzahl der Pins zu reduzieren, die für die Implementierung der externen Speicherschnittstelle erforderlich sind. Zwischen Controller und Speicher ist ein externes Latch (Auffangregister) einzufügen, und der Controller liefert ein ALE-Signal (Address Latch-Enable) zur Kontrolle dieses externen Auffangregisters. Wenn ALE abfällt, werden die Daten am Input des Latches (A/D[n:0]) zwischengespeichert und während des gesamten Speicherzugriffs an den Speichereingängen (AL[n:0]) erhalten. Sobald die Adresse zwischengespeichert ist, geht der Controller vom A/D-Bus weg und setzt das /RD-Signal bei einem Lesevorgang auf »Low«, wie in Bild 4 gezeigt. Im Fall eines Schreibvorgangs legt der Controller die Daten auf den A/D-Bus und setzt das /WR-Signal auf Low. Nicht alle Adressen in Bild 4 sind gelatcht, und die Laufzeitverzögerung des Latches fügt bei den Adressen einen Skew hinzu.

Viele mit dem Adress-Latch arbeitende Controller liefern kein dediziertes Chip-Enable-Signal. In diesem Szenario können obere Adressen mit Glue-Logic zum Einsatz kommen, um zwischen verschiedenen Speicherchips oder anderen Peripheriegeräten zu wählen. Der /CEPin des Speicherchips kann während der Gesamtdauer des Speicherzugriffs Low bleiben, und die Adressenänderungen sind der einzige Hinweis darauf, dass ein Zugriff beendet ist und ein weiterer beginnt.

Damit ein pseudostatischer Speicherchip in einen SRAM-Sockel seinen Dienst tun kann, muss er die folgenden Address-Skew-Szenarien berücksichtigen:

- Address-Skew von Chipselect (negative Addressen-Setup-Zeit) und

- Address-Skew von anderen Adressen bei ATD-Zugriffen.

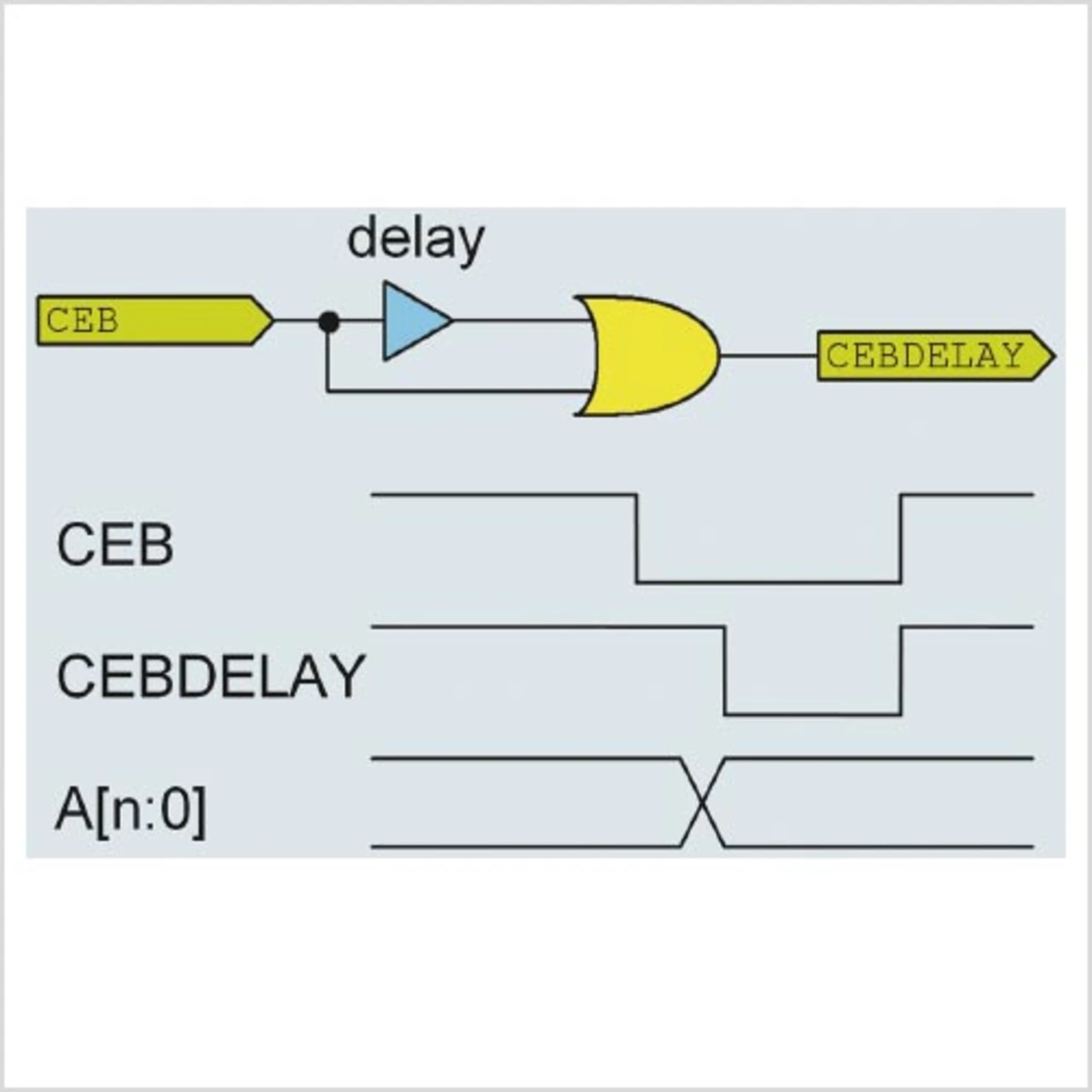

Das erste Szenario lässt sich leicht über längere Zugriffsund Zykluszeiten bewältigen. Die Lösung für das zweite Szenario ergibt sich ganz von selbst als Folge der pseudostatischen ATD-Implementierung. Bild 5 zeigt eine einfache asynchrone Verzögerungsschaltung, die dazu dienen kann, intern die abfallende Flanke des Chip-Enable-Signals zu verzögern, damit nach dem Abfallen des Chip-Enable-Signals für die Adressenänderungen noch Zeit bleibt.

- Einfach fallen lassen

- Einfach fallen lassen

- Maskerade

- Einfach fallen lassen

- Einfach fallen lassen