DSP-Algorithmen effizient implementieren – Teil 1 #####

Fortsetzung des Artikels von Teil 4

Bereitstellung von Programm-Code und Daten

Ein wichtiges Element ist der Datentransfer von der Systemebene zum Prozessor-Core. Wie schon im vorigen Abschnitt angesprochen, ist der Transfer von Daten aus dem externen Speicher zeitaufwendig. Greift der Core direkt auf diese Daten zu, führt dies unweigerlich zu einem Pipeline-Stall, da das Holen der Daten durch die Struktur erheblich verzögert wird. Eine Lösung ist hier das Benutzen von Cache oder eines Overlay-Managements mittels DMA. Bei DSPs kann man zwischen Daten-Cache und Instruktions-Cache unterscheiden. Die Hardware übernimmt dabei die Entscheidung, welche Daten bzw. Instruktionen in den internen Speicher geladen werden sollen. Die Cache-Funktion ist entweder teilweise oder auch ganz abschaltbar. Als Alternative zum hardwaregesteuerten Cache bietet sich das explizite Laden von Daten sowie Instruktionen mittels der DMA-Funktionalität an. Dabei muss der Programmierer selbst die DMA aufsetzen, um Daten vom externen in den internen Speicher zu laden. Beim so genannten Overlay-Management teilt man den Code in kleine, unabhängige Code-Passagen ein, welche separat bei Bedarf in den internen Speicher geladen werden können. Der große Vorteil des Cache besteht darin, dass dem Programmierer die Entscheidung abgenommen wird, welche Daten bzw. Code-Teile in den internen Speicher geladen werden müssen.

Jobangebote+ passend zum Thema

Dafür hat das Overlay-Management Vorteile bezüglich der Rechenleistung in Applikationen, bei denen die Daten im externen Speicher nicht statisch sind, d.h. durch Peripherie-DMAs beeinflusst werden. In diesem Fall sind drei verschiedene Ansätze zu unterscheiden:

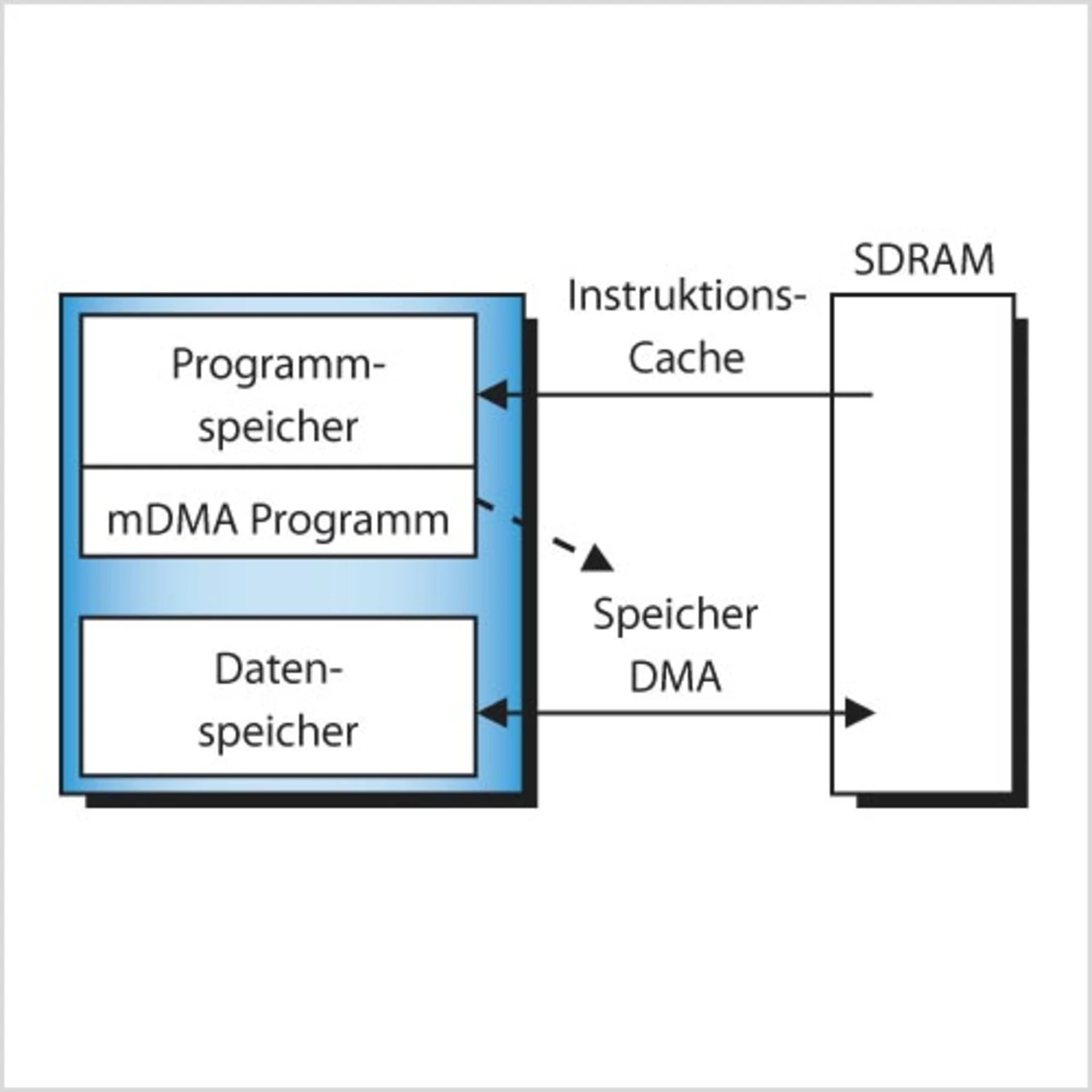

- Der Instruktions-Cache ist eingeschaltet, die Daten werden via DMA in den internen Speicher geladen: Hierbei werden die Instruktionen hardwareorganisiert, d.h. automatisch in den internen Speicher geladen, während die Daten explizit vom Programmierer via DMA in den internen Speicher geladen werden müssen (Bild 6).

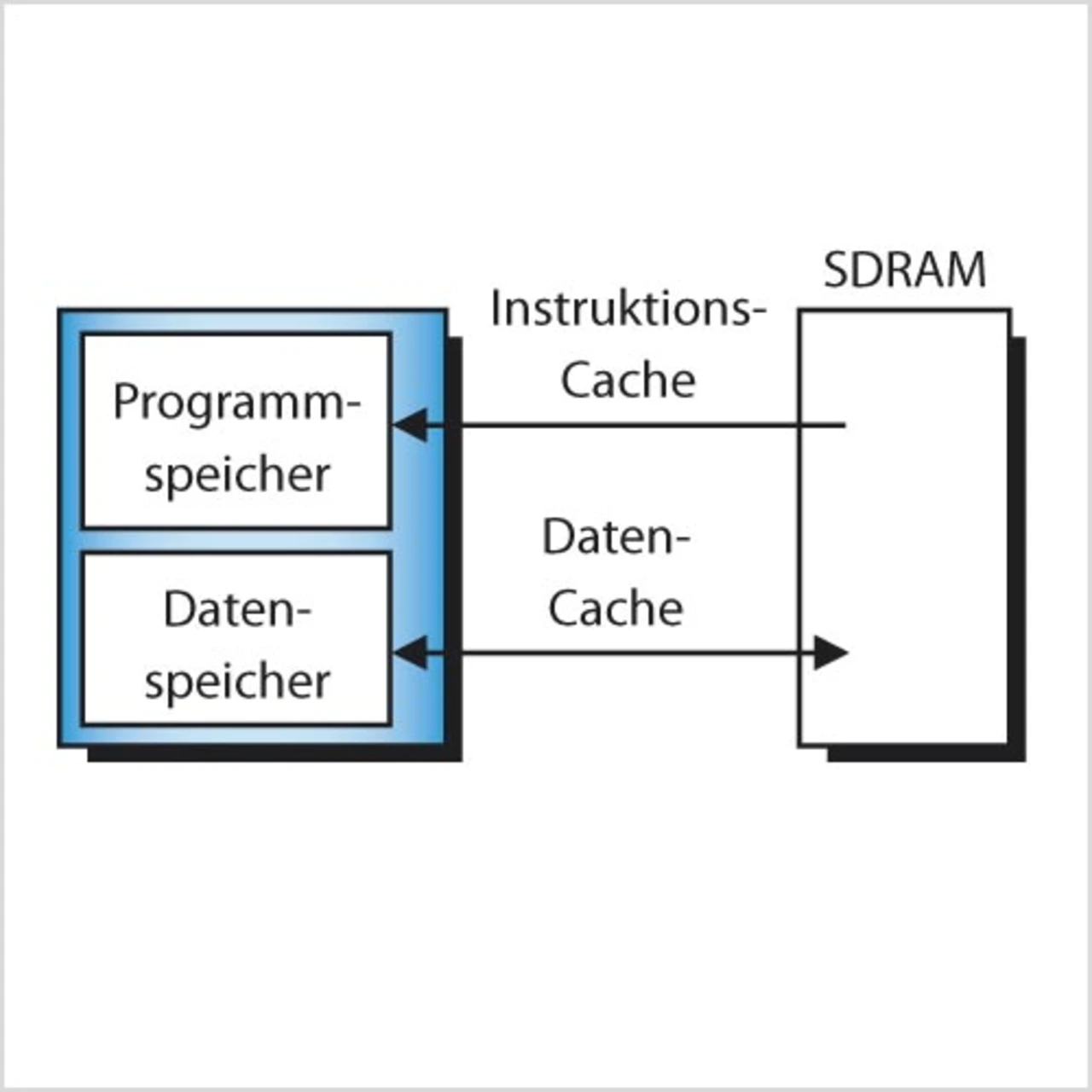

- Der Instruktions-Cache und der Daten-Cache sind eingeschaltet: Die Hardware sorgt dafür, dass sowohl Daten als auch Instruktionen automatisch in den internen Speicher geladen werden (Bild 7).

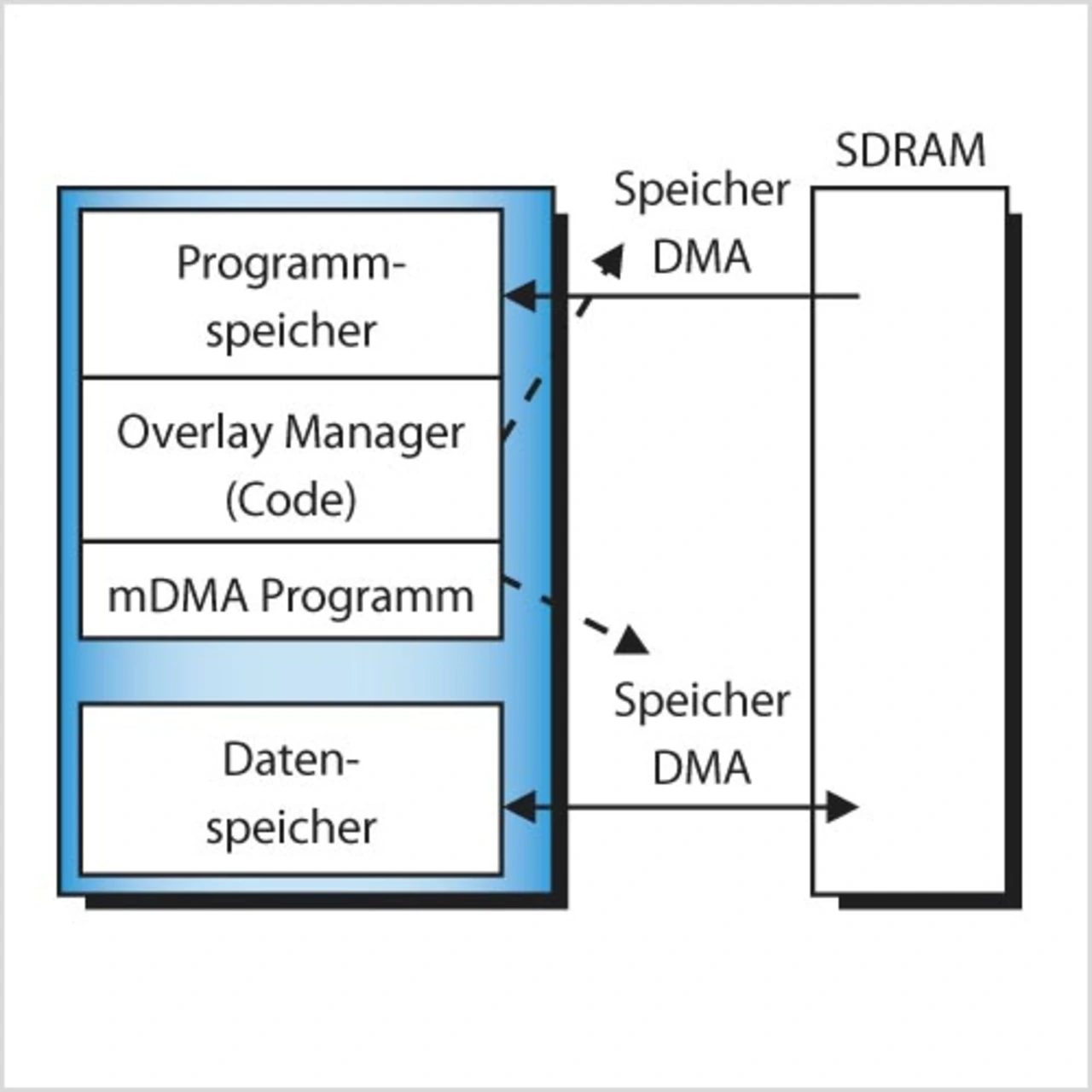

- Instruktionen via DMA, Daten via DMA: Hierbei organisiert der Programmierer alles: Die Software muss selbstständig kontrollieren, welcher Teil des Programm-Codes in den internen Programmspeicher und welche Daten in den internen Datenspeicher geladen werden. Der Programm-Code wird dabei in so genannten Code-Overlays (kleine Programm-Code-Segmente, die in den internen Speicher passen) organisiert, welche mittels eines DMA-Transfers in den internen Speicher geladen werden (Bild 8).

- DSP-Algorithmen effizient implementieren – Teil 1 #####

- DSP-Algorithmen effizient implementieren – Teil 1

- Phase 1: Die mathematische Modellierung des Problems

- Phase 3: Anpassung des Algorithmus an den Prozessor

- Bereitstellung von Programm-Code und Daten

- DSP-Algorithmen effizient implementieren – Teil 1