DSP-Algorithmen effizient implementieren – Teil 1 #####

Fortsetzung des Artikels von Teil 1

DSP-Algorithmen effizient implementieren – Teil 1

Die älteren SHARC-Modelle haben so genannten Dual-Port-Speicher, welcher zwei Zugriffe in einem Zyklus erlaubt. Andere Modelle, wie der Blackfin, haben ihn aufgrund der hohen Taktfrequenzen nicht, da Dual-Port-RAM intern mit dem doppelten Takt wie der Prozessorkern selbst betrieben werden muss und dies bei höheren Frequenzen technisch sehr aufwendig wird. Dies stellt einen Nachteil dar, da nicht zwei Daten in einem Taktzyklus aus einer SRAM-Bank geladen oder gespeichert werden können. Der Nachteil kann jedoch dadurch ausgeglichen werden, indem bei der Implementierung darauf geachtet wird, dass jene Daten, welche simultan aus dem Speicher geholt werden müssen, in unterschiedlichen Speicherbänken untergebracht sind. Aus diesem Grunde sollte man die einzelnen Bänke in den Linker-Dateien (bei der Entwicklungs-Software „Visual DSP++“ beschreibt das Linker-Description-File (LDF) das Speicher-Mapping des Prozessors) einzeln definieren, um auf diese Weise sicherzustellen, dass man Puffer oder Variablen explizit in bestimmte Speicherbereiche legen und auf diese Weise dem Algorithmus effizient bereitstellen kann.

Jobangebote+ passend zum Thema

Der TigerSHARC bietet aufgrund der Größe des internen Speichers nicht nur ein SRAM, sondern auch ein internes DRAM, welches mit dem halben Prozessor-Core-Takt betrieben wird. Um dennoch mit dem Prozessor-Core-Takt auf den Speicher zugreifen zu können, ist der Bus doppelt so breit wie die Daten. Dabei wurde die Annahme gemacht, dass die Zugriffe auf den Speicher sequenziell ablaufen. Aus diesem Grunde sollte man dies bei der Implementierung eines Algorithmus berücksichtigen, da ansonsten wertvolle Taktzyklen verschenkt werden.

Da Programme sowie Daten zumeist einen größeren Raum einnehmen, kommt man heute nur selten um die Tatsache herum, externen Speicher zu benutzen. Aufgrund des Preises und der Geschwindigkeit wird hier meistens SDRAM (SDR (Single Data Rate), DDR (Double Data Rate), DDR2, DDR3 bzw. ihre mobilen Varianten) verwendet. Da die Taktgeschwindigkeit des SDRAM erheblich unter der des Core-Taktes liegt und zumeist durch Handshake-Mechanismen die System-bzw. Core-Grenze weitere Einbußen mit sich bringt, sollte man auf direkte Zugriffe verzichten und entweder mit Cache oder mit Overlay-Management arbeiten. Eine weitere Einschränkung des SDRAM ist architekturbedingt: Das SDRAM teilt sich in mehrere interne Bänke auf, welche sich wiederum in mehrere Zeilen (Rows) und Reihen (Columns) aufteilen. Jedes Mal, wenn eine neue Zeile in einer Bank adressiert wird (sog. Öffnen einer Page), muss intern im Speicherbaustein die vorige Reihe vom Puffer zurückgeschrieben und die neu-adressierte Reihe in dem Puffer platziert werden. Dieser Vorgang benötigt einige Zyklen.

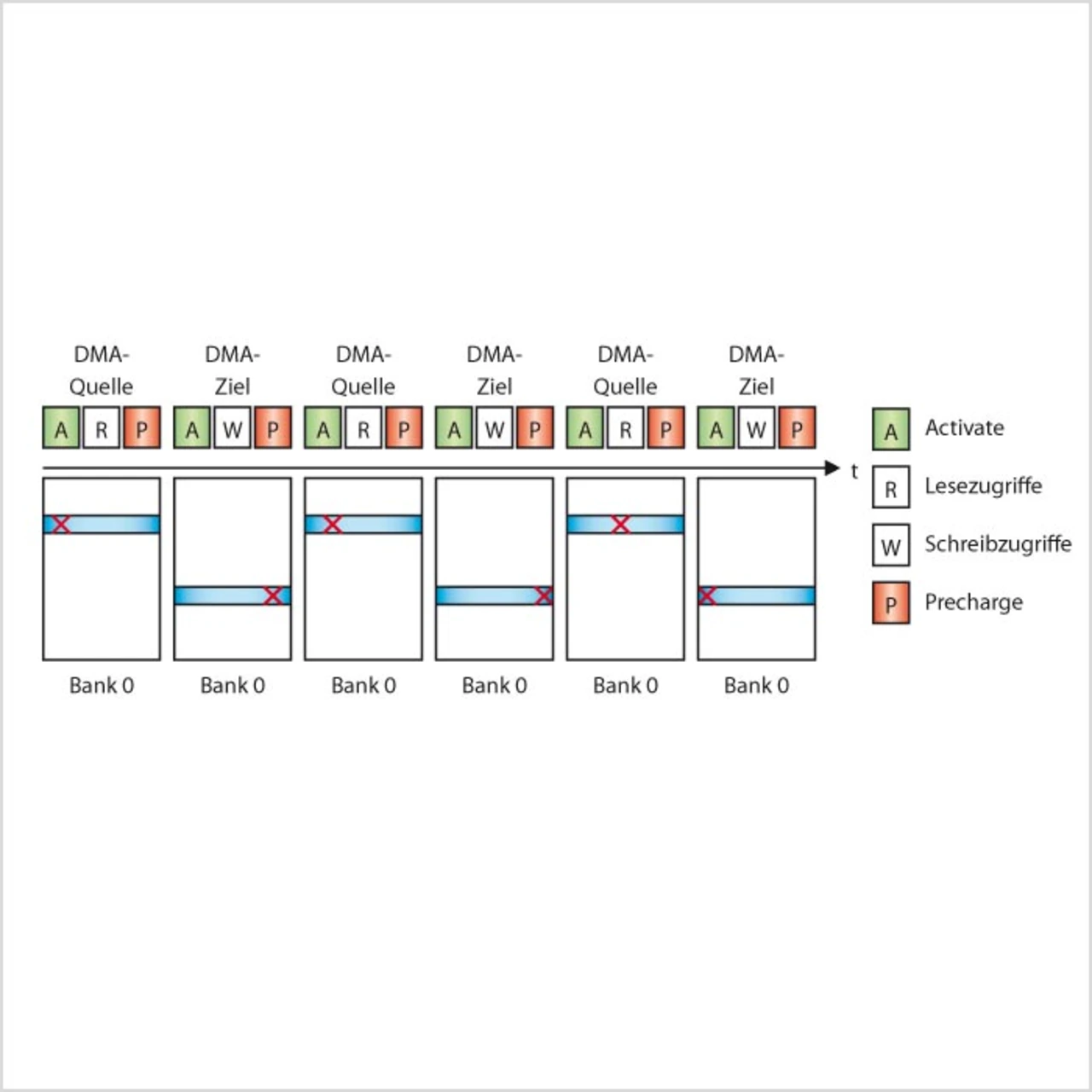

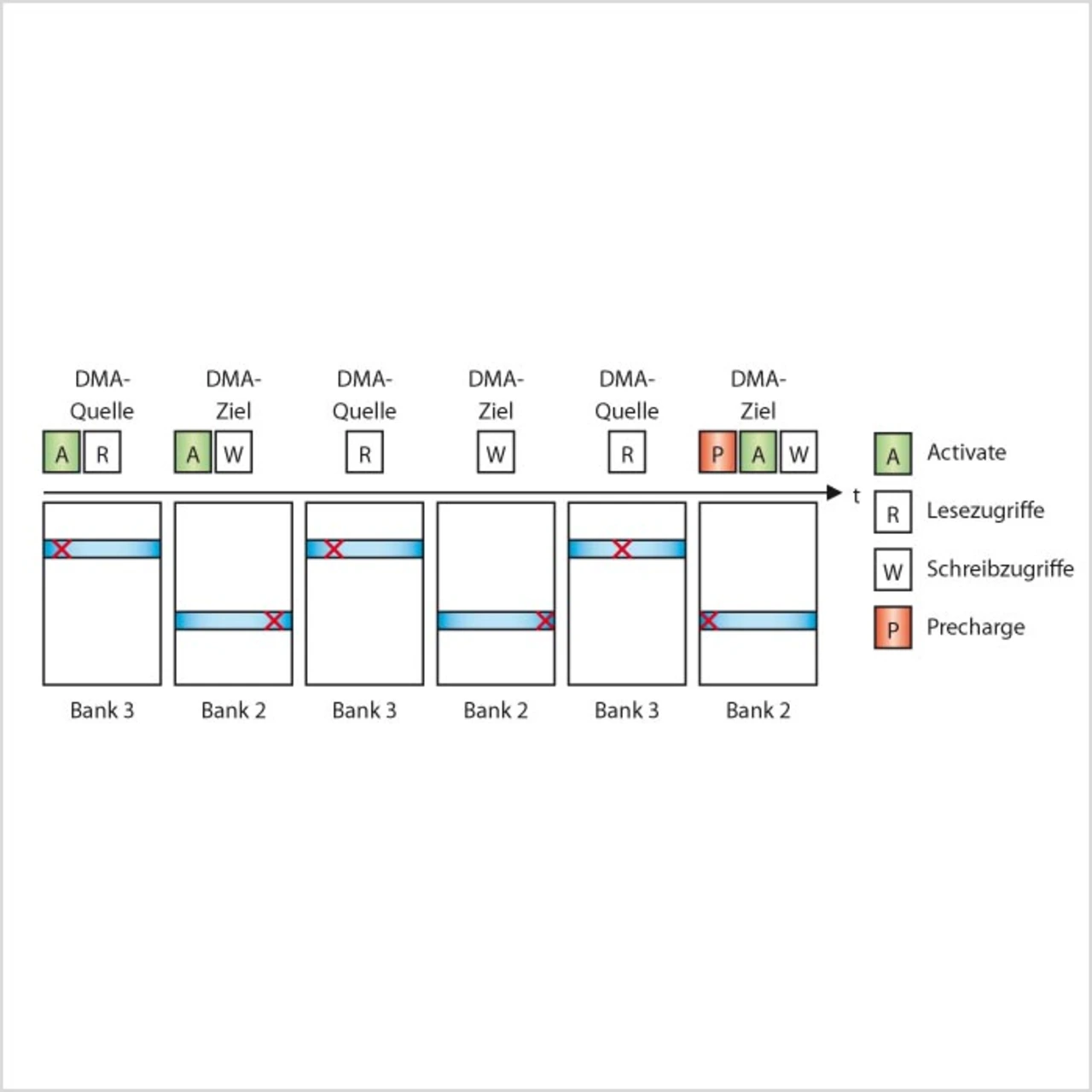

Bei der Optimierung von SDRAM-Datentransfers durch Speicher-DMAs (DMA zum Transfer von Speicher zu Speicher) ist es ratsam, die Quell- und die Zielarrays in unterschiedliche Bänke zu legen (vorausgesetzt, die Speicherschnittstelle unterstützt Multibanking wie bei der Blackfin-Familie, d.h., der Speichercontroller hat die Möglichkeit, alle internen SDRAM-Bänke parallel zu verwalten), da dies die ACTIVATE- und PRECHARGE-Operationen zum Öffnen und Schließen einer Page (welche sehr zeitaufwendig sind) minimiert. Bild 4 und Bild 5 demonstrieren die Verbesserung, welche durch eine bewusste Aufteilung der Quell- und Zielarrays in verschiedene Speicherbänke realisiert werden kann.

Bei DDR, DDR2 und DDR3 lassen sich Leistungsverbesserungen erzielen, wenn sequenziell auf die Daten im RAM zugegriffen werden kann. Der Grund für dieses Phänomen sind die festen Burst-Längen von 2 (DDR), 4 (DDR2) und 8 (DDR3), d.h., es werden mindestens 2, 4 oder 8 Datenpakete pro Adressierung durch den DSP übertragen. Bei nicht-sequenziellen Zugriffen auf das DDRx-SDRAM nimmt die Datenrate (Bytes pro Zyklus) ab, da hier immer mehrere Daten hintereinander übertragen und die nicht benötigten Daten verworfen werden. Dieser Nachteil bei nicht-sequenziellen Zugriffen auf DDR2 und DDR3 kann nur teilweise durch die höhere Taktrate ausgeglichen werden.

- DSP-Algorithmen effizient implementieren – Teil 1 #####

- DSP-Algorithmen effizient implementieren – Teil 1

- Phase 1: Die mathematische Modellierung des Problems

- Phase 3: Anpassung des Algorithmus an den Prozessor

- Bereitstellung von Programm-Code und Daten

- DSP-Algorithmen effizient implementieren – Teil 1