Blick ins Kerngehäuse

Der Cortex-M3 im Vergleich zu ARM7 – Was ist neu?

Fortsetzung des Artikels von Teil 1

Der Cortex-M3 im Detail

In seinen Marketingaussagen hebt ARM u.a. hervor, dass der Cortex-M3 32-bit-Performance zum 8-bit-Preis liefert, die Implementierungskosten niedrig sind und der Core sich für Anwendungen in drahtloser Vernetzung, Automotive, Industrie, weißer Ware, Spielzeug und medizinischen Geräten nutzen lässt. Was steckt hinter diesen Behauptungen? Abgesehen davon, dass z.B. der Preis keine Eigenschaft des Cores ist, gibt es durchaus Neuerungen, die obige Aussagen erhärten. Bei diesen Neuerungen verzichtete ARM bewusst auf die Aufwärtskompatibilität von den bisherigen ARM-Cores, um wirklich Neues zu schaffen. Der Cortex-M3 ist ein RISC-Prozessor mit der ARMv7-M-Architektur. Diese Architektur enthält einen neuen Befehlssatz. Während die meisten ARM7-Derivate zwei Befehlssätze verstehen – den ARM- und den Thumb- Befehlssatz, zwischen denen wahlweise gewechselt werden kann –, versteht der Cortex-M3 „nur“ den Thumb-2- Befehlssatz.

Durch diese vermeintliche Einschränkung kommt der Core mit einem sehr einfachen Aufbau aus. Er benötigt nur eine relativ kleine Anzahl von ca. 33 000 Gattern, was natürlich einen positiven Einfluss auf den Stromverbrauch und die Siliziumgröße (Herstellkosten) hat. Der ARM7 hatte den umfangreichen ARM-Befehlssatz, mit den Vorteilen einer effektiven und schnellen Abarbeitung. Dieser 32-bit-Befehlssatz ist für „kleinere“ Applikationen zwar sehr effektiv, aber die Code- Größe war im Vergleich nicht optimal. Hierfür wurde der 16-bit-Thumb- Befehlssatz ergänzt. Er hat nicht die gleiche Mannigfaltigkeit und Performance, aber da er ein 16-bit-Befehlssatz ist, benötigt er weniger Programmspeicher.

Der Befehlsmodus kann funktionsweise umgeschaltet werden. Manche Compiler können dies auch blockweise, wie z.B. der von Tasking. Dadurch lässt sich alles, was schnell sein muss, im ARM-Modus und alles andere größenoptimiert im Thumb-Modus compilieren und so das Optimum an Performance und Code- Größe erreichen.

Optimierter 16-/32-bit-Befehlssatz

Der Cortex-M3 hat nur den Thumb-2- Befehlssatz. Hier hat ARM bereits ein Optimum geschaffen. Thumb-2 ist ein Thumb-Befehlssatz mit 32-bit-Erweiterungen. Er ist annähernd so leistungsstark wie ARM und hat fast die gleiche Code-Größe wie Thumb, ohne dass zwischen beiden Modi hin und her geschaltet werden muss. Detailliert wird hierauf in einem weiteren Artikel eingegangen. Die Cortex-M3-Architektur bietet noch einen weiteren Vorteil. Sowohl für Startup-Code als auch für Interrupt- Service-Routinen wird kein Assembler- Code mehr benötigt. Wo beim ARM7 noch Assembler-Code steht, um die Stackpointer und Eigenschaften der verschiedenen Modi zu initialisieren oder um in der Interrupt-Service- Routine Register zu sichern und die Modi umzuschalten, übernimmt beim Cortex-M3 diese Aufgaben die CPU. Alles andere kann in C geschrieben werden.

Bezüglich der Arithmetik enthält der Thumb-2-Befehlssatz DSP-ähnliche Instruktionen – auch das ist neu. So kann eine 32-bit- Multiplikation in einem Zyklus durchgeführt werden. Auch Divisionen werden schneller ausgeführt. Vorzeichenbehaftete oder vorzeichenlose 32-bit-Divisionen benötigen zwischen zwei und zwölf Zyklen. Sowohl dem ARM- als auch dem Thumb- und Thumb-2-Befehlssatz fehlen Bitmanipulationsbefehle. Bei einem ARM7 musste also ein Setzen oder Löschen eines Bits im Speicher oder in einem Special Function Register (SFR) durch Lesen, Ver-Oderung oder Ver-Undung und Zurückschreiben realisiert werden – ein Nachteil gegenüber Architekturen, die das unterstützen.

Jobangebote+ passend zum Thema

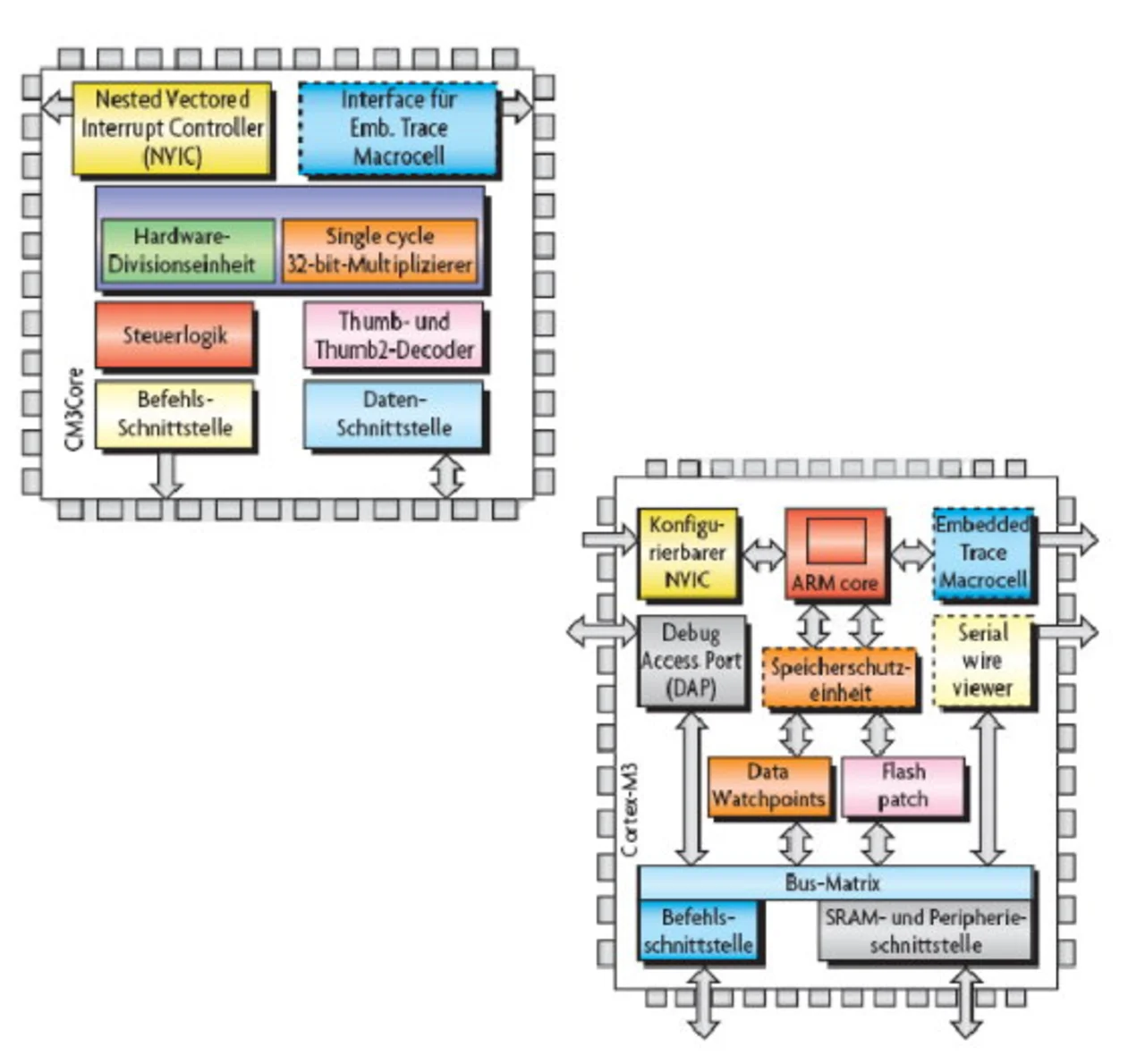

Auch hier wurde Abhilfe mit der „Bit-Banding“-Methode geschaffen. Zwei dedizierte 1-Mbyte-Adressbereiche im RAM und für SFRs haben im Hintergrund je einen 32 Mbyte großen Bit-Banding- Alias-Bereich. Wird ein Wert mit dem LSB 1 auf eine Adresse im Alias-Bereich geschrieben, so wird automatisch das entsprechende Bit-Band-Bit gesetzt und beim LSB-Wert 0 gelöscht. Hiermit ist auf diese Bereiche ein direkter Bit-Zugriff ohne read/modify/write möglich. Ein weiterer Vorteil des Cortex-M3 ist, dass er eine Harvard-Bus-Architektur aufweist, d.h., Code und Datenbusse sind getrennt (Bild 1).

Dies hat nicht nur Einfluss auf die Befehlsabarbeitung bei Schreib- und Lesezugriffen in den Datenspeicher, sondern erlaubt auch DMA-Zyklen, die ablaufen können, ohne dass die Befehlsabarbeitung hierdurch gestört wird. Bei den klassischen ARM-Controllern hört nun der ARM-spezifische Teil auf, alles Weitere ist Aufgabe der Designer des endgültigen Derivates. Auch grundlegende Peripherieeinheiten wie Interrupt-Controller, Systick Timer und die Sleep Modes wurden von jedem Chiphersteller selbst definiert und unterscheiden sich damit. Ein Wechsel vom ARM7-Derivat eines Herstellers zu einem anderen Hersteller erfordert schon bei elementaren Applikationen größere Eingriffe. Außerdem bedeutet die Trennung der Peripherieeinheiten vom Core und dem enthaltenen Debug-Interface auch, dass das Debug-Interface auf diese Peripherie keinen direkten Zugriff haben kann. Nicht so beim Cortex-M3.

- Der Cortex-M3 im Vergleich zu ARM7 – Was ist neu?

- Der Cortex-M3 im Detail

- Die neue Peripherie

- Einstieg in die STM32-Welt