Blick ins Kerngehäuse

Der Cortex-M3 im Vergleich zu ARM7 – Performance und Speicherbedarf

Fortsetzung des Artikels von Teil 1

Leistungsfähiger Thumb2-Befehlssatz

Der STM32 hat – wie jeder Cortex- M3-Controller – einen ARMv7-M-Befehlssatz. Dieser Befehlssatz geht zurück auf den Thumb-Befehlssatz des ARM7, der mit Thumb2-32-bit-Befehlen erweitert wurde. Damit vereint die CPU mit dem Thumb2-Befehlssatz die Vorteile eines leistungsfähigen 32-bit- Befehlssatzes mit den Vorteilen der kleinen Code-Größe des 16-bit- Thumb-Befehlssatzes. Die Performance- Benchmarks sind sehr umstritten, da sie sehr von der Applikation abhängen. Deshalb wird hier nur kurz darauf eingegangen und nur ein Vergleich von ARM zitiert.

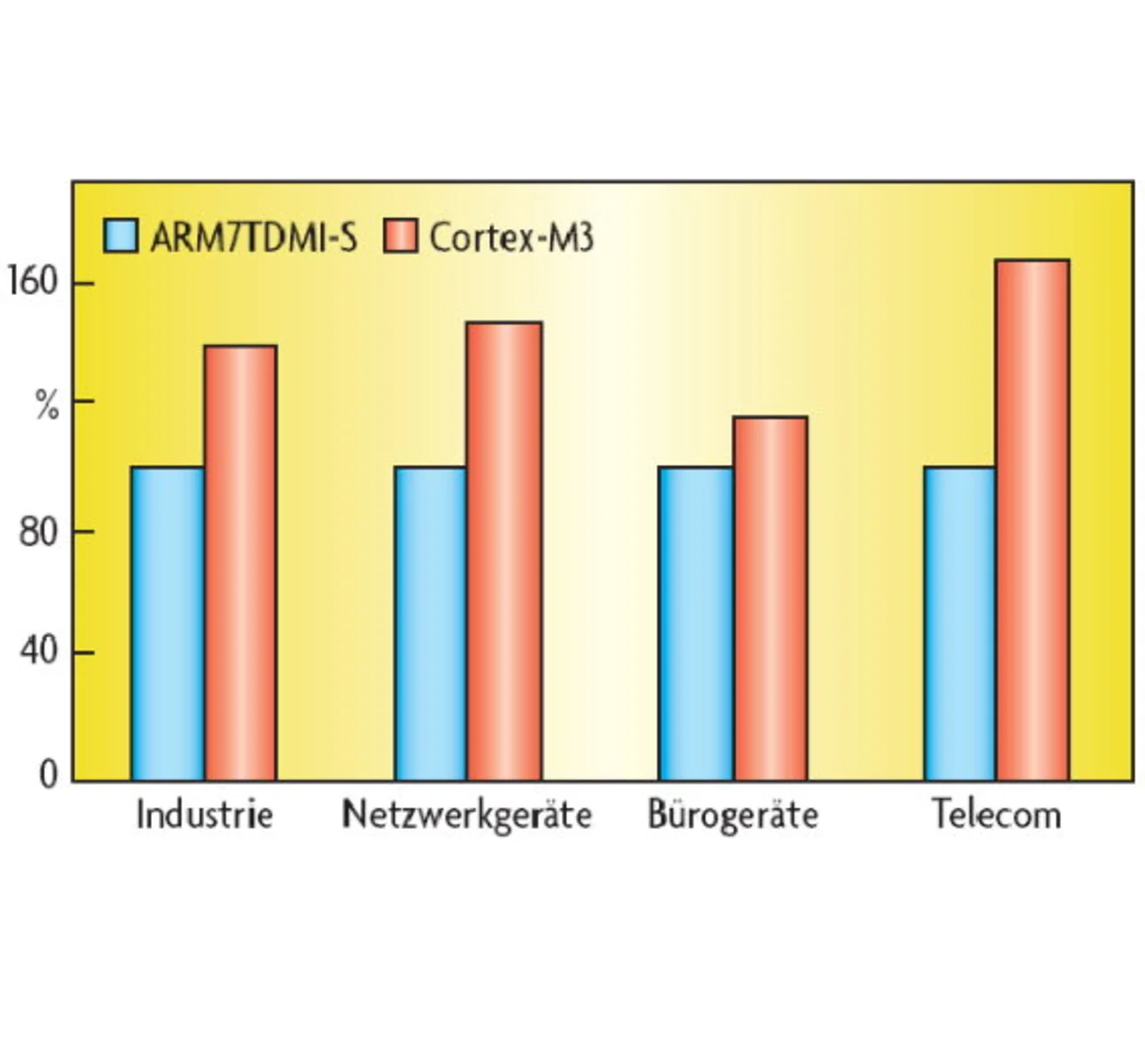

Bild 1 zeigt den Vergleich zwischen ARM7 und Cortex- M3 für verschiedene Applikationen aus den Bereichen Industrie, Netzwerkgeräte, Office und Telecom. Dies passt auch zu den Dhrystone-Benchmark- Aussagen, die für ARM7 0,95 Dhrystrone-MIPS/MHz und bei Cortex- M3 1,25 Dhrystone-MIPS/MHz angeben. Neben dem optimierten Befehlssatz wurde die ALU auch mit DSP-ähnlichen Befehlen erweitert, womit Multiplikationen in einem Zyklus und Divisionen in zwei bis sieben Zyklen durchgeführt werden können. Zusätzlich kamen noch verbesserte Sprungbefehle, if/then-bedingte Ausführungsblöcke und optimierte Befehle zur Datenbearbeitung hinzu. Zur direkten Bearbeitung von einzelnen Bits wurden die Bit-Banding- Adressbereiche geschaffen, die den direkten schnellen Zugriff auf einzelne Bits ohne read/modify/write-Zyklen zulassen.

Schnelle Interrupt-Latenzzeit

Eine deutliche Verbesserung gegenüber den ARM7-Controllern ist die Interrupt- Verarbeitung des Cortex-M3. Sie wurde beschleunigt, besser durch Hardware unterstützt und ist damit insbesondere für echtzeitkritische Systeme besser verwendbar, da die Interrupt- Latenzzeit nun deterministisch geworden ist. Ein ARM7-Core hat zwei Interrupts, den FIQ und den IRQ. Wird der FIQ, wie vorgesehen, für einen schnell zu bearbeitenden Interrupt genutzt, so müssen sich alle anderen Interrupts den IRQ teilen, wofür einiges an Software-Aufwand nötig ist, damit der IRQ von anderen IRQ-Quellen unterbrochen werden kann („nested interrupts“). Unbequemerweise war hierfür auch Assembler-Code nötig. Beim Cortex-M3 ist mit dem Nested Vector Interrupt Cotroller (NVIC) nun eine deutlich bessere Anbindung an den Core integriert.

Die Vektortabelle kann bis zu 256 Einträge enthalten, und jede Interrupt-Quelle hat hier einen festen Vektor mit einem Eintrag der entsprechenden Interrupt-Service- Routine. Wird ein Interrupt von einer Peripherie-Einheit angemeldet, so bedient die CPU diesen Interrupt, indem sie zunächst eine Reihe Register auf dem Stack sichert. Dies geschieht in Microcode, es ist also keine Software hierfür nötig. Die CPU benötigt hierfür zwölf Push-Zyklen. Währenddessen wird die Zieladresse für diesen Interrupt von der Vektortabelle gelesen, sodass der erste ISR-Befehl nach den zwölf Zyklen ausführbereit ist. Ein sehr schnelles und deterministisches Verfahren. Selbstverständlich geschieht das Wiederherstellen der Register vom Stack am Ende einer Interrupt- Service-Routine entsprechend. Noch effektiver wird dieses Verfahren, wenn mehrere Interrupts nacheinander behandelt werden.

Ein typischer Anwendungsfall ist, dass während eines höher prioren Interrupts ein niedriger priorisierter ansteht. In diesem Fall ist es unnötig, beim Verlassen der Interrupt-Service-Routine die gesicherten Register wiederherzustellen, um sie dann gleich wieder auf dem Stack zu sichern. Dies erspart sich auch die CPU, was als „tail chaining“ bezeichnet wird. Bei zwei direkt hintereinander abgearbeiteten Interrupts sind lediglich sechs Zyklen zwischen dem ersten und dem zweiten Interrupt nötig. Das Wiederherstellen der Register geschieht dann nach der zweiten ISR. Ein besonderer Fall ist, dass am Ende der ISR beim Wiederherstellen der Register ein erneuter Interrupt eintritt. Auch hier erspart sich die CPU doppelte Arbeit: Das Wiederherstellen der Register wird abgebrochen, der Stackpointer auf die Position vor der Wiederherstellung gesetzt, und der neue Interrupt kann bearbeitet werden. Ein anderer oft eintretender Fall ist, dass ein höher priorisierter Interrupt einen niedriger priorisierten unterbricht.

Geschieht das während der Push-Zyklen am Beginn („late arrival“), werden diese Pushs zu Ende geführt und gleich die höher priorisierte ISR ausgeführt. Am Ende wird wie oben beschrieben („tail chaining“) gleich zur niedriger priorisierten ISR geschaltet. Der direkte Vergleich zwischen ARM7 und Cortex-M3 bezüglich Interrupt- Bearbeitung ergibt eine Interupt- Latenz bei ARM7 von 24 bis 42 Zyklen, bei Cortex-M3 von nur zwölf Zyklen. Vergleicht man die Inter-Interrupt- Latenz, ergibt dies bei ARM7 24, bei Cortex-M3 nur sechs Zyklen. Dies ist eine deutliche Verbesserung.

Jobangebote+ passend zum Thema

- Der Cortex-M3 im Vergleich zu ARM7 – Performance und Speicherbedarf

- Leistungsfähiger Thumb2-Befehlssatz

- Verkleinerte Code-Größen, bessere Speicherausnutzung