Welcher Rechenknecht darf es sein?

ARM-Cortex-M3-MCU-Implementierungen und deren Unterschiede

Fortsetzung des Artikels von Teil 1

On-Chip-Bus-Architektur

Neben den eher offensichtlichen Unterschieden der verschiedenen Hersteller wie z.B. die Implementierung der ARM Cortex-M3 Ref. 1 oder Ref. 2 oder der gewählten Peripherie (z.B. CAN, USB, A/D- oder D/A-Umsetzer) gibt es weniger auffällige Architekturmerkmale, wie zum Beispiel die AMBA-Bus-Architektur. Diese kann bei der richtigen Anwendung und dem richtigen Verständnis einen entscheidenden Leistungsvorteil bringen.

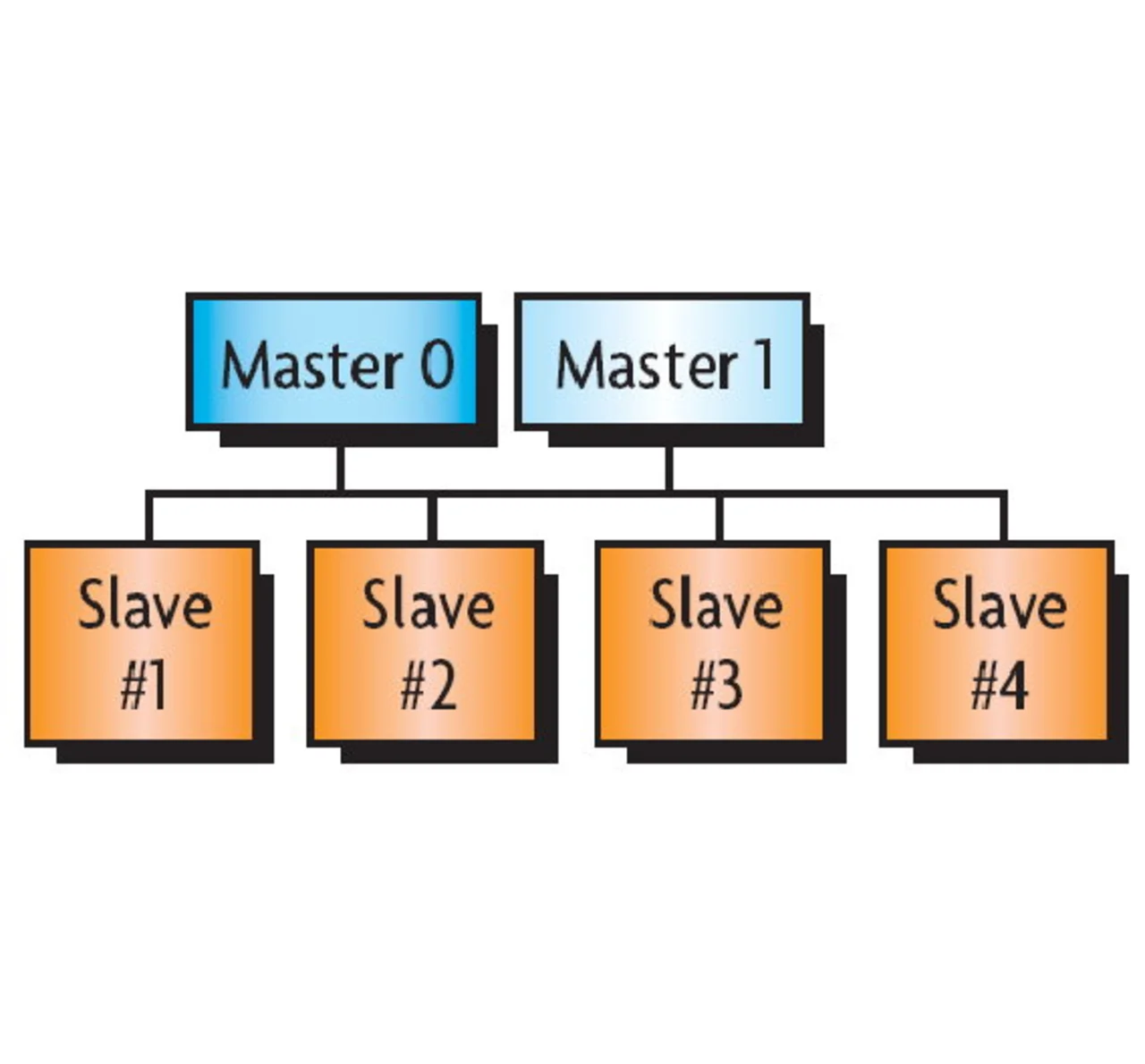

Prinzipiell sind bei AMBA 2.0 zwei Möglichkeiten zu unterscheiden. Die Multi-Master-AHB-Bus-Architektur (Bild 3) weist sich dadurch aus, dass immer nur ein Master (z.B. Core oder DMA) über einen AHB-Bus auf eine Peripheriebaugruppe (Slave an diesem Bus) oder den Speicher zur gleichen Zeit zugreifen kann.

Man sieht häufig, dass die dadurch möglicherweise entstehenden Engpässe etwas abgeschwächt werden, indem man die Peripheriebaugruppen auf zwei AHB-Busse aufteilt. Das Prinzip bleibt bestehen, es wird hier eine Arbiterlogik gebraucht, welche die Rechtevergabe regeln muss, wer gerade den Bus für wie lange verwenden kann. Keiner der anderen Peripheriebaugruppen, die an diesem Bus liegen, kann zur selben Zeit mit einen anderen Master Daten austauschen.

Jobangebote+ passend zum Thema

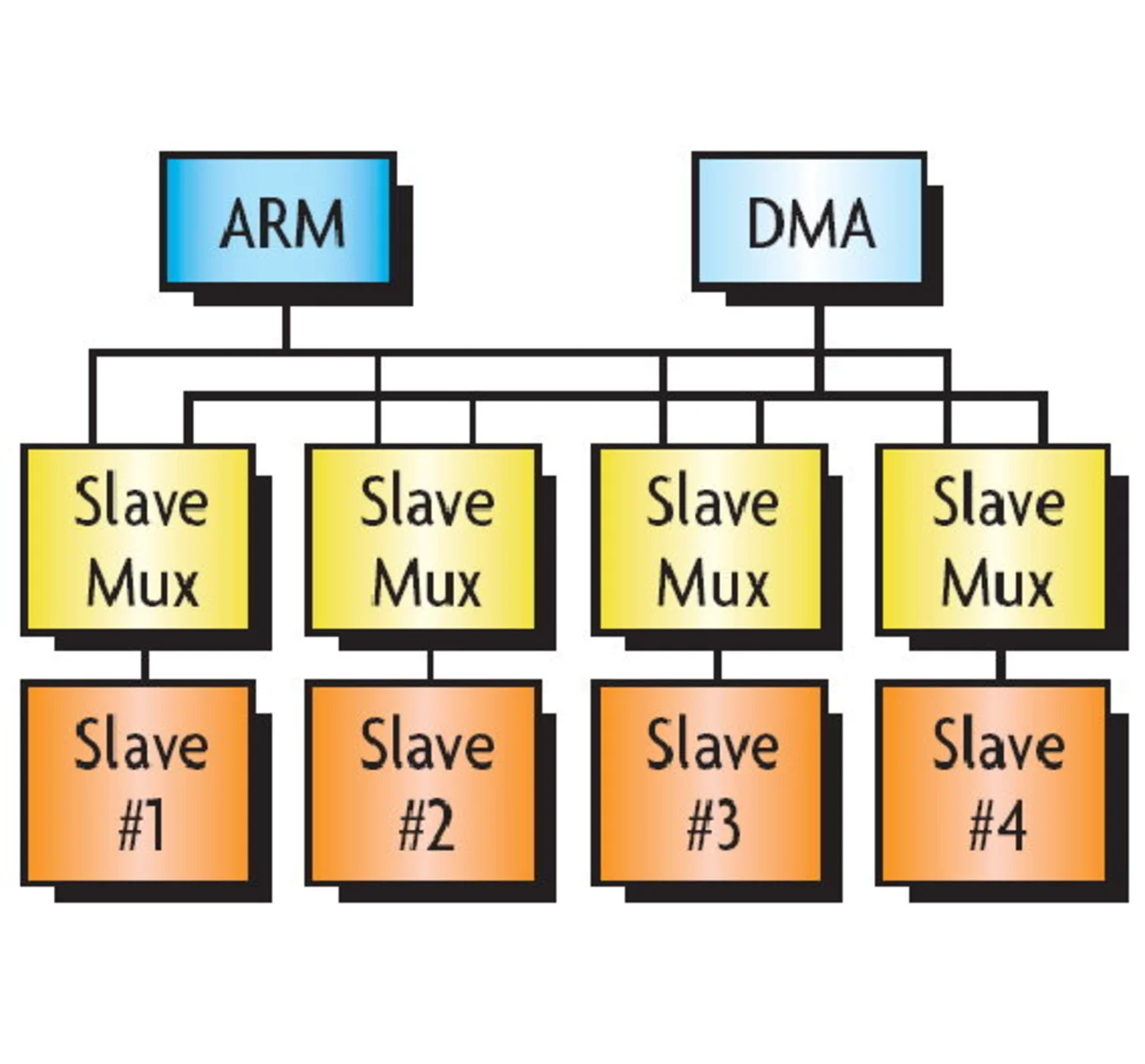

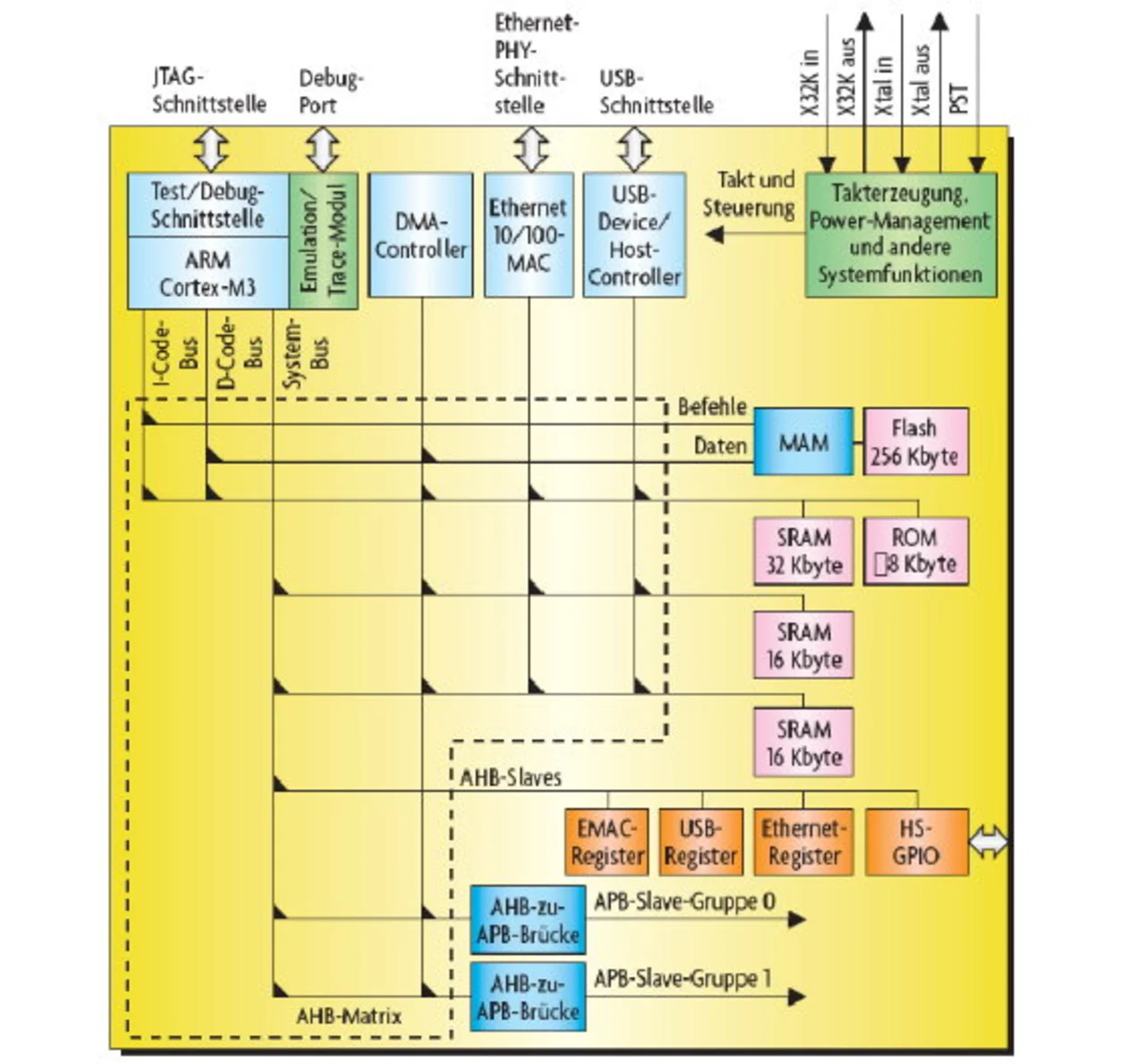

Die zweite Möglichkeit ist das Multi- Layer-AHB-Bus-System (Bild 4). In dieser Architektur gibt es mehrere parallele AHB-Busse zu allen nötigen Peripheriebaugruppen und zum Speicher. Dieses hat den Vorteil, dass verschiedene Master (z.B. ARM-Core und DMA) gleichzeitig Daten mit verschiedenen Peripheriebaugruppen oder dem Speicher austauschen können. Man spricht von einem X-Layer-AHBBus- System, wenn X parallele AHBBusse zu den Peripheriebaugruppen im System sind. Das X, also die Anzahl der AHB-Busse, richtet sich im System meistens danach, wie viele eigenständige Master im System vorhanden sind (z.B. ARM-Core, DMA, USB Host oder CAN). Bild 5 zeigt beispielhaft eine Implementierung beim LPC1700.

Die Qual der Wahl

Insgesamt kann man hinsichtlich Cortex- M3-basierter MCUs zwischen fünf Herstellern auswählen. Wie bereits erwähnt, hat die Firma Luminary Micro, die 2009 von Texas Instruments gekauft wurde, als erste im März 2006 einen ARM Cortex-M3-basierenden Mikrocontroller auf den Markt gebracht. Bis heute wurden mehr als 130 verschiedene Varianten und viele unterschiedliche Evaluations- und Referenz-Kits für verschiedene Anwendungen veröffentlicht. Unterstützt werden diese Referenz- Kits mit einer ausführlichen StellarisWare- Software-Bibliothek für Grafik und einer Treiber-Bibliothek für Anwendungen wie Motorsteuerung und grafische Ansteuerelemente über ein QVGA-16-bit-Farb-LCD.

STMicroelectonics war der erste der etablierten ARM-Partner und Mikrocontroller- Hersteller, der sein Portfolio mit dem ARM Cortex-M3 Ref. 1 erweitert hat. Die STM32-Familie ist seit 2007 auf dem Markt und erfreut sich wachsender Beliebtheit.

Wie Texas Instruments bietet auch STM eine Reihe verschiedener Starter- und Referenz-Kits an, die durch eine gute Software-Bibliothek unterstützt werden. Unter anderem enthält diese Bibliothek Software-Module für Motorsteuerungs- Anwendungen und die Unterstützung des neuen Sicherheitsstandards für Haushaltsgeräte (IEC60330), der seit Oktober 2007 für Neugeräte bindend ist. Weitere interessante Punkte dieser Implementierung sind das vom Core getrennte Debug-Modul, das auch bei „versehentlicher“ Verprogrammierung des Clock-Trees den Zugriff auf den Core ermöglicht, sowie eine Takt-Sicherheits-Schaltung, die einen Ausfall des externen Taktes (z.B. des Quarzes) bemerkt und auf einen internen Oszillator umschalten kann, ohne dass der Core „abstürzt“.

NXP hat eine 100- MHz-Variante des ARM Cortex-M3 angekündigt. Diese wird die erste sein, die auf der Ref.-2-Version des ARMCore basiert. Ebenso wie STM und Atmel kann auch NXP bei der Implementierung von ARM-Cores für Mikrocontroller auf eine mehrjährige erfolgreiche Zusammenarbeit mit ARM zurückblicken. NXP kann auf einen bestehenden Kundenkreis aufbauen und an die Erfolge mit dem LPC2000 anknüpfen. Die Peripheriebaugruppen (z.B. USB, CAN) sehen ähnlich aus wie bei dem LPC2000, haben aber auch einige Neuerungen speziell für Motorsteuerungsanwendungen vorgesehen. Der LPC1700 wird einen speziellen Motorsteuerungs-PWM-Block und eine Quadratur-Encoder-Schnittstelle (QEI) enthalten. Für die erfolg reichsten Produkte wie z.B. LPC2366 wird NXP eine pinkompatible Variante des LPC1700 anbieten. Bei den optionalen Komponenten hat NXP an nichts gespart und so ziemlich alles implementiert, was ARM zur Verfügung stellt. Der LPC1700 wird eine MPU und alle Debug- und Trace-Komponenten wie ETM enthalten.

Toshiba ist der erste japanische Mikrocontroller- Hersteller, der dieses Jahr mit einem ARM Cortex-M3- basierten Produkt (TMPM330 und TMPM380) auf dem Markt kommt. Starter-Kits stehen schon jetzt mit Tool-Unterstützung von Keil und IAR Systems zu Verfügung. Ungewöhnlich und interessant ist, dass Toshiba auch 5 V Versorgungsspannung unterstützt. Wie alle anderen hat auch Toshiba spezielle Peripheriebaugruppen, die Motorsteuerungs-Anwendungen unterstützen, in der TMPM370- Variante der Familie. Wie STM hat Toshiba darauf geachtet, den neuen Sicherheitsanforderungen nach IEC 60730 gerecht zu werden und zu unterstützen. Atmel ist auch einer der etablierten ARM-Partner und wird sein ARM-basiertes Controller-Portfolio dieses Jahr mit einer ARM-Cortex-M3-Ref.-2-Variante erweitern. Wie NXP und auch STM kann auch Atmel auf bestehende Plattformen und Peripheriebaugruppen aus anderen ARM-Architekturen (AT91SAM7 und AT91SAM9) zurückgreifen. So kann bestehenden oder auch neuen Kunden immer populärer werdende Technologie in bekannter Umgebung angeboten werden. In Tabelle 3 sind die heute verfügbaren Informationen über die Cortex-M3-Implementierungen zusammengefasst.

| Hersteller | Cortex-M3 Ref. | maximale Taktfrequenz | Bus-System zu Slaves | MPU | DMA | Flash-Zugriff | ETM |

|---|---|---|---|---|---|---|---|

| LMI | 1 | 50 MHz |

Multi-Layer-AHB, 1x ABP |

ja | nein | nein | nein |

| STM | 1 | 72 MHz |

Multi-Layer-AHB, 2x APB | nein | ja |

nein | ja |

| NXP | 2 | 100 MHz | Multi-Layer-AHB, 2x APB | ja | ja | ja | ja |

| Atmel | 2 | 84 MHz | Multi-Layer-AHB |

ja | ja | ja | ? |

Tabelle 3. Vergleich der Eigenschaften unterschiedlicher Cortex-M3-Implementierungen.

Zusammenfassung und Ausblick

ARM wird mit der Cortex-M3-Architektur einen weiteren Schritt zum „Quasi“-Standard für 32-bit-Mikrocontroller machen. Dieses Jahr werden viele neue ARM-Cortex-M3-Varianten von zahlreichen Herstellern auf den Markt kommen. Man sollte etwas Zeit investieren und sich die technischen Details genau ansehen, um die relevanten Unterschiede und das richtige Derivat für das nächste Produkt zu finden. Der von ARM angekündigte Cortex- Mikrocontroller-Software-Interface- Standard (CMSIS) wird einen weiteren guten Beitrag zur Kompatibilität und Produktivitätsteigerung bei der Software-Entwicklung leisten. Viele der genanten Hersteller haben ihre Unterstützung angekündigt. Es bleibt abzuwarten, wann und in welcher Form diese auch umgesetzt wird.

- ARM-Cortex-M3-MCU-Implementierungen und deren Unterschiede

- On-Chip-Bus-Architektur