Schaltungstechnik für Sensoren

Diskrete Verstärker optimieren

Fortsetzung des Artikels von Teil 2

Offsetspannung minimieren

Offsetspannung minimieren

Die größte Fehlerquelle für diese Verstärkerimplementierung ist die hohe Offsetspannung am Eingang. Zum Großteil bestimmt durch die Fehlanpassung der Eingangs-FETs, kann diese Offsetspannung bis zu 10 mV betragen. (Das Datenblatt für den LSK389 nennt eine Fehlanpassung von 20 mV. Ein so hoher Pegel wurde während der Tests jedoch nicht festgestellt). Eine Verstärkung von 100 erzeugt einen Ausgangsoffset von 1 V und macht den Verstärker somit praktisch unbrauchbar. Bevor sich dieses Bauteil als Vorverstärker eignet, muss die hohe Eingangsoffsetspannung gesenkt werden. Dies erfolgt mit dem Digitalpotentiometer »AD5292« von Analog Devices. Es gibt zwei Möglichkeiten, diesen Offset mit Hilfe des Potentiometers zu reduzieren.

Jobangebote+ passend zum Thema

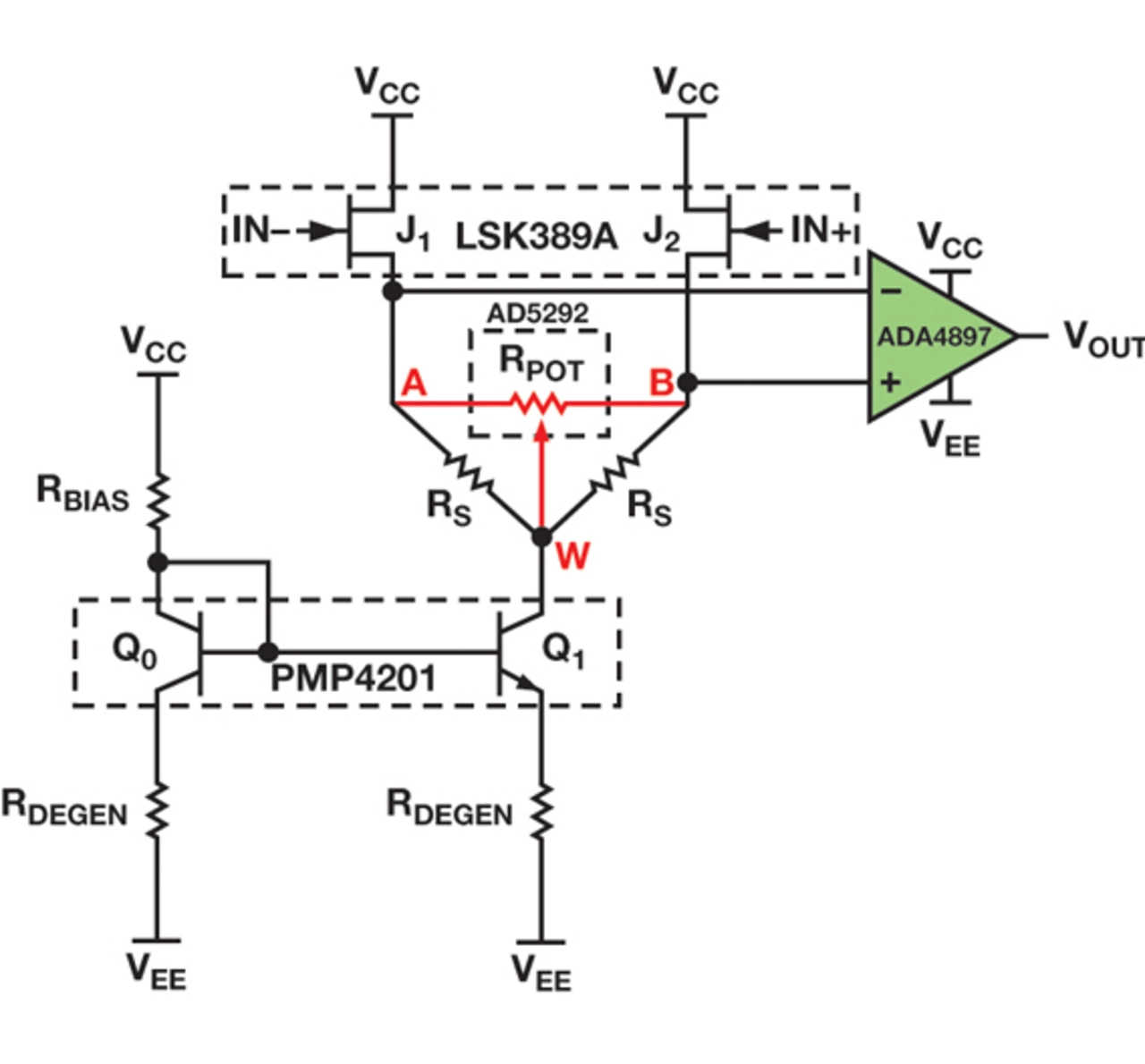

Bei den für diesen Artikel verwendeten Exemplaren des Verstärkers schwankte die Eingangsoffsetspannung von 1 mV bis 10 mV. Das Datenblatt für den LSK389 zeigt, dass der Drain-Reststrom IDSS um bis zu 10% variieren kann. Dies beeinträchtigt die VGS der Bauteile und bewirkt eine Offsetspannung. Zum Glück ergibt sich der Offset aus ungleichen Ruheströmen durch die JFETs. So lassen sich die Stromquellen, die diese Ströme liefern, entsprechend einstellen und dieser Fehler kompensieren. Eine Methode, wie sich eine Offsetspannung von Null erreichen lässt, zeigt Bild 6.

Ein Digitalpotentiometer wie das AD5141 oder AD5292 kann verwendet werden, um den Strom durch die Eingangsbauteile einzustellen. Tabelle 3 zeigt wichtige Spezifikationen dieser Bauteile, bestehend aus einem Potentiometer mit drei Anschlüssen, das über eine SPI-Schnittstelle gesteuert wird, um den Schleifer für eine genaue Widerstandseinstellung exakt zu positionieren.

| Bauteilnummer | Speisespannung in V | Nennwiderstand in Ω | Widerstandstoleranz in % | Auflösung in Bit | Betriebstemperatur in °C |

|---|---|---|---|---|---|

| AD5141 | ±2,5 | 10, 100 | 8 | 8 | -40 bis +125 |

| AD5292 | ±16 | 20, 50, 100 | 1 | 10 | -40 bis +105 |

Tabelle 3: Spezifikationen der Digitalpotentiometer

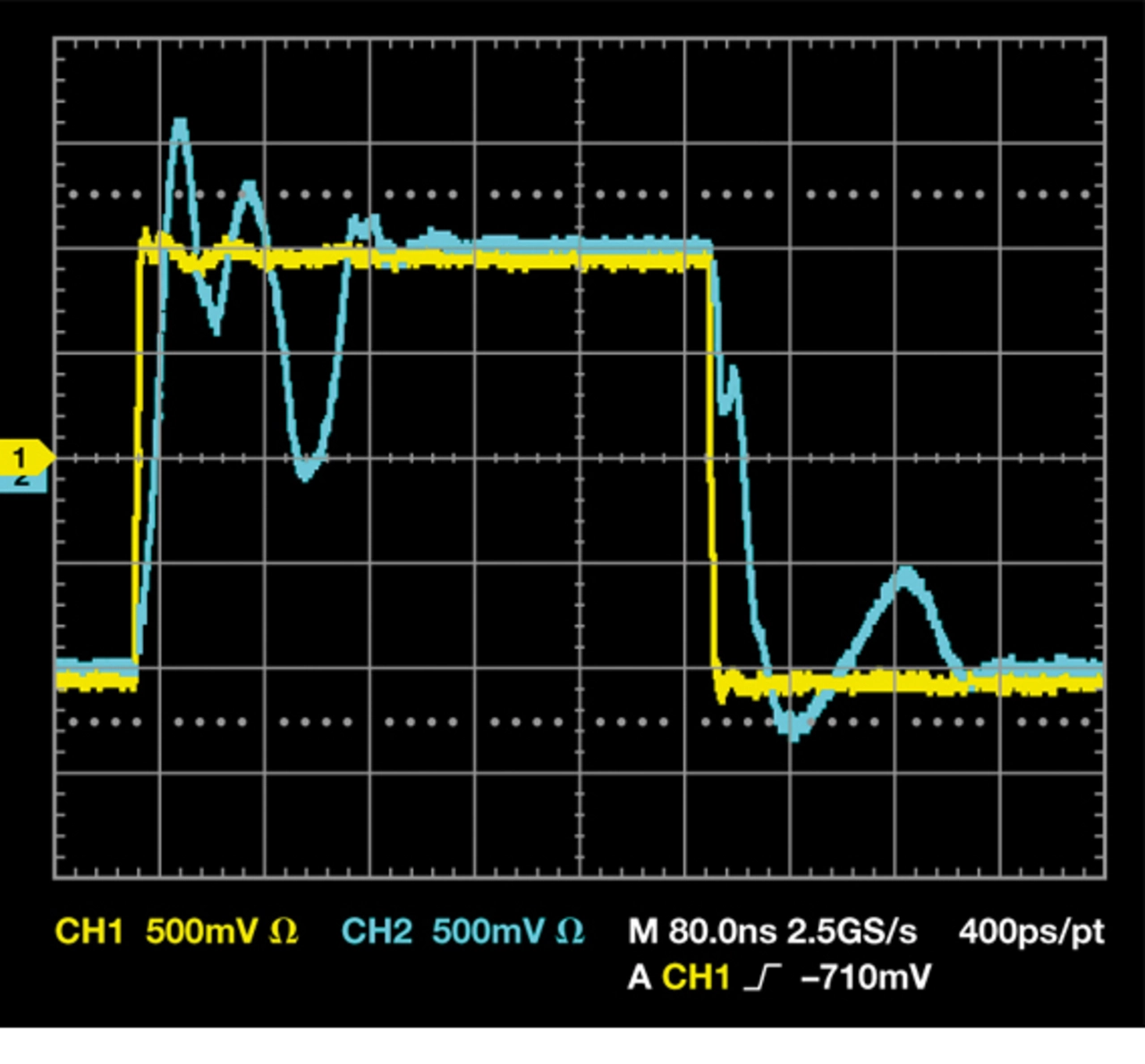

Leider haben diese Digitalpotentiometer große parasitäre Kapazitäten (bis zu 85 pF), die bei hohen Frequenzen Probleme bei der Stabilität sowie Überschwingen verursachen können.

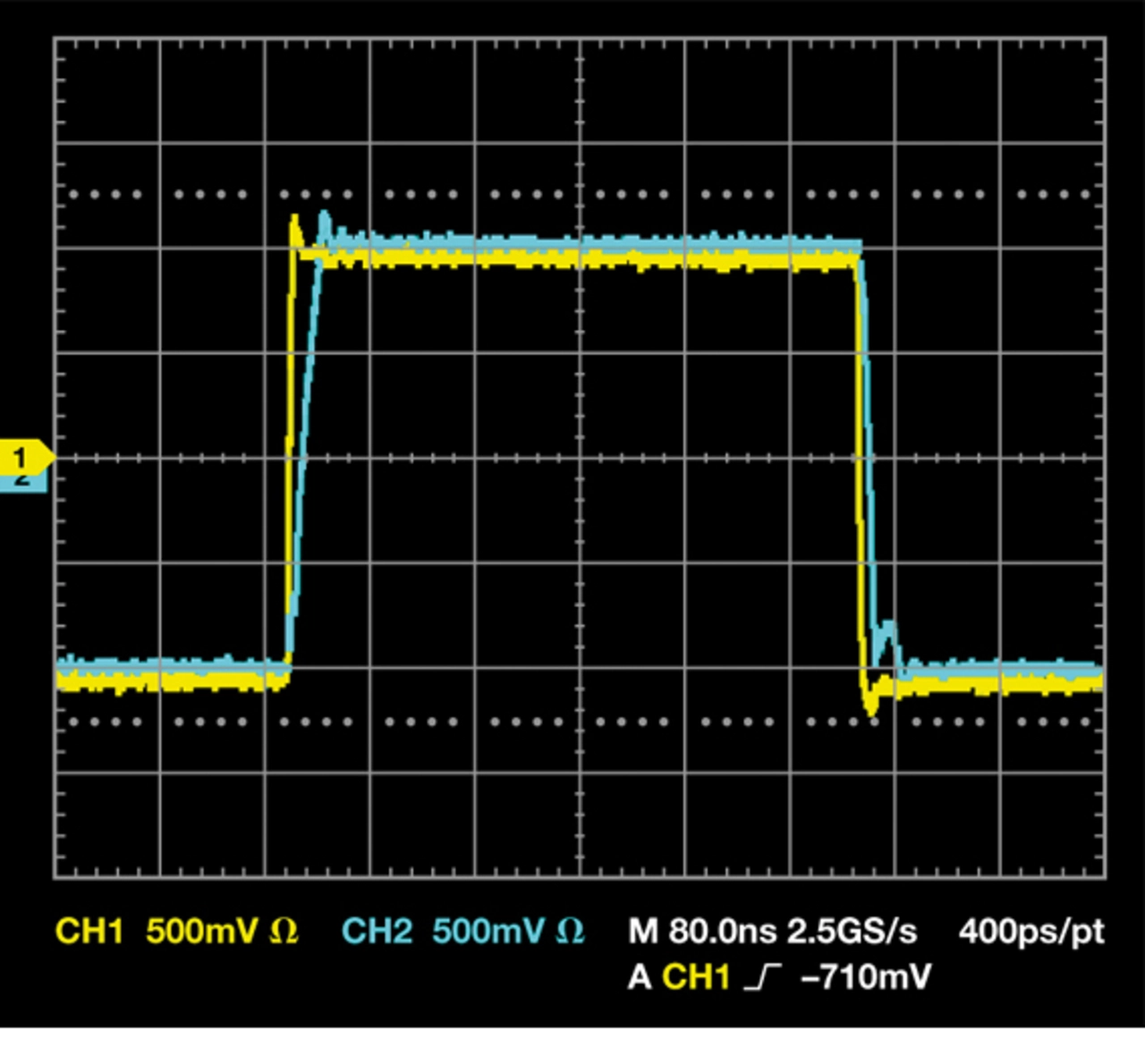

Bild 7a und b zeigt die Sprungantwort des Verstärkers mit und ohne dieses Potentiometer. Die parasitäre Kapazität von 85 pF befindet sich zwischen der Quelle des Eingangs-FETs und Masse.

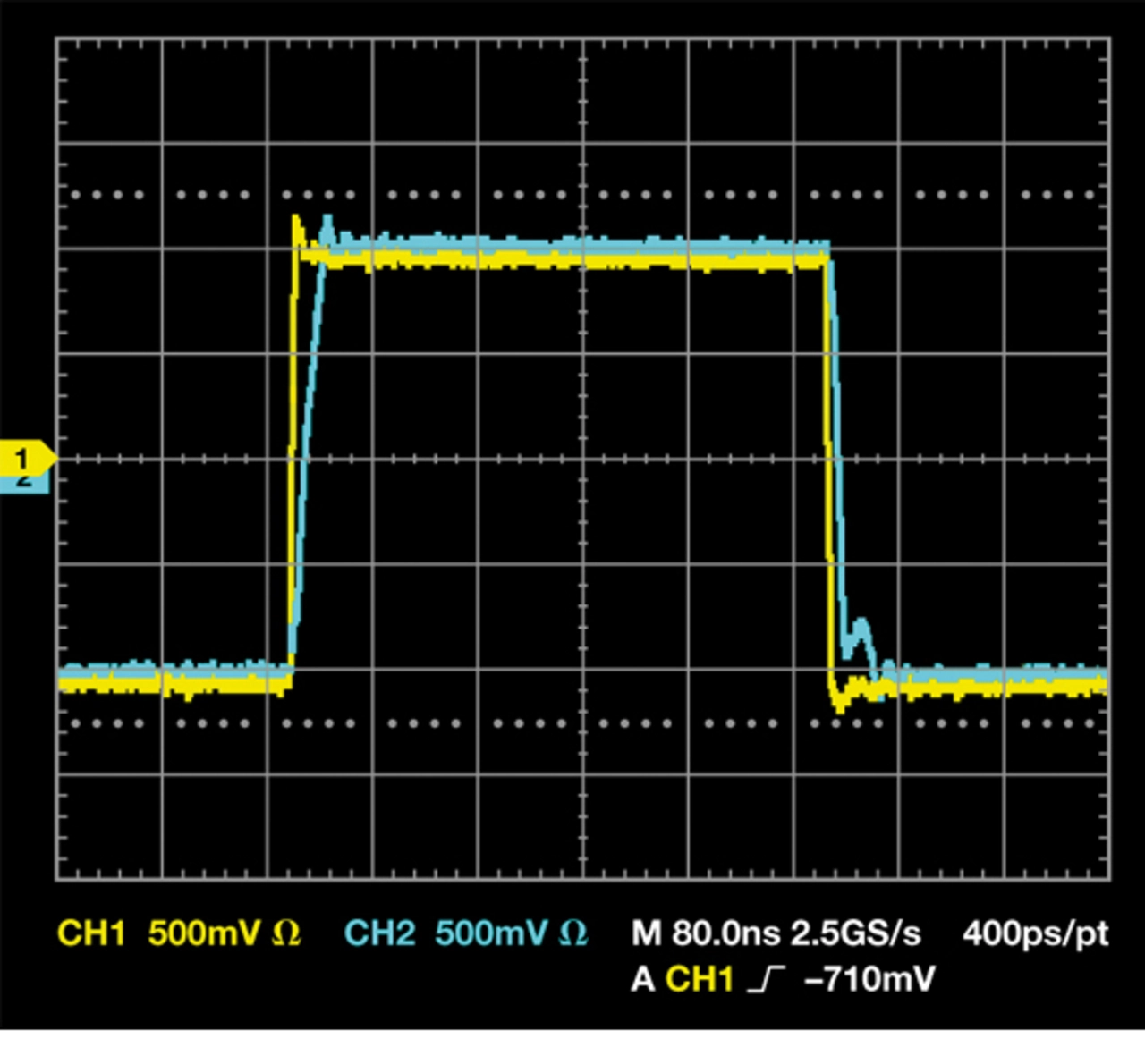

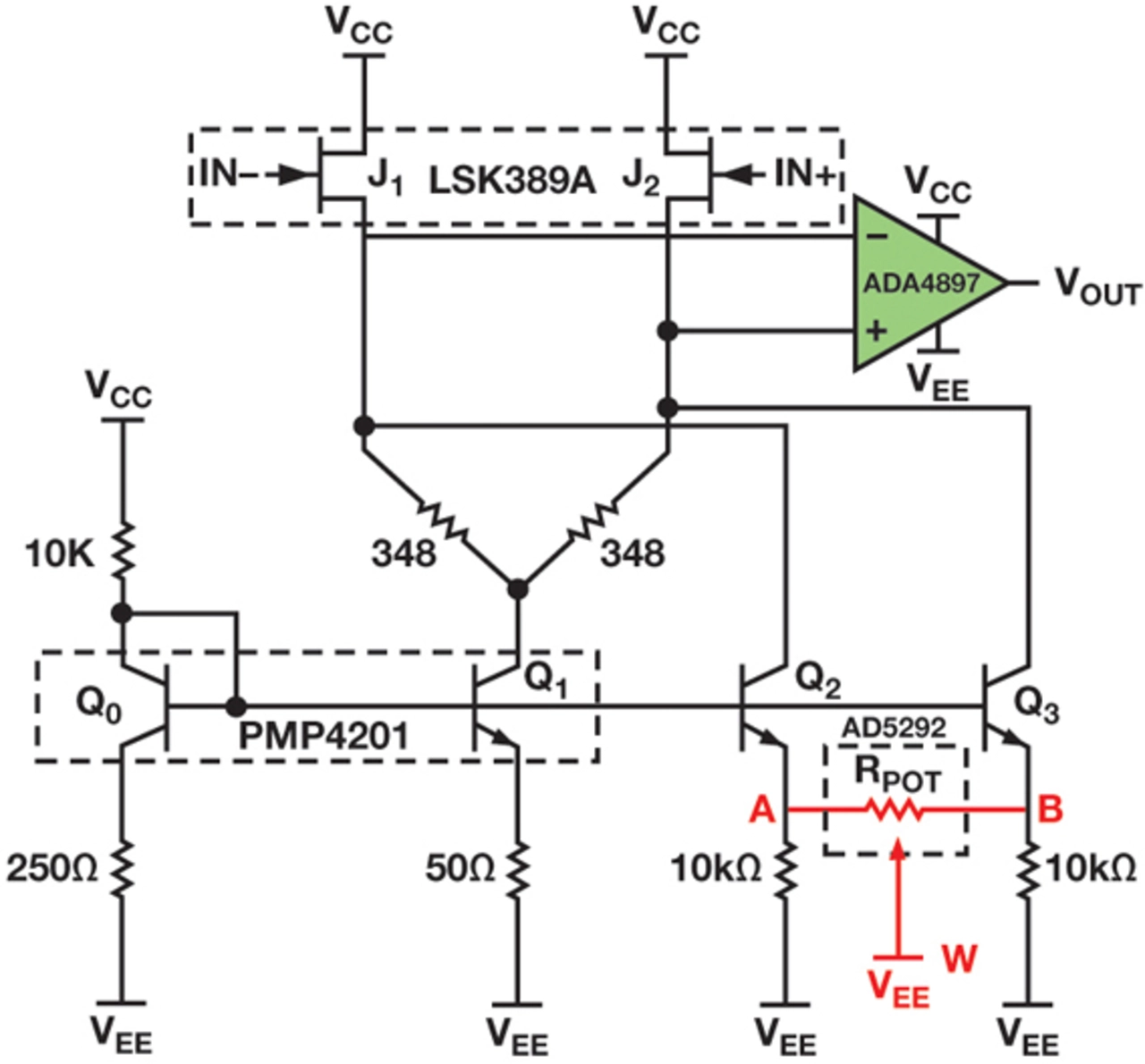

Dies verursacht signifikantes Überschwingen bei hohen Frequenzen. Ein alternativer Biasing-Aufbau, der die Eingangsoffsetspannung reduziert, während geringes Rauschen und Stabilität bei hohen Frequenzen erhalten bleiben, zeigt Bild 8.

Bei beiden genannten Biasing-Methoden wird das Digitalpotentiometer verwendet, um den Strom durch jeden FET so lange einzustellen, bis ihre Gate-Source-Spannungen zueinander passen und so die Eingangsoffsetspannung minimiert wird. Das Biasing-Konzept in Bild 8 stellt sicher, dass die große parasitäre Kapazität des Potentiometers bei hohen Frequenzen weder Instabilitäten noch Überschwingen verursacht. Das Konzept arbeitet mit einer Kombination der zwei Stromquellen-Konfigurationen in den Bildern 3 und 4. Der Stromspiegel bestehend aus Q0/Q1 liefert den Großteil des Stromes an die FETs, indem der Kollektorstrom gesplittet wird. Dadurch verursachen die Biasing-Transistoren fast kein Rauschen. Q0, Q2 und Q3 bilden einen eher traditionellen Stromspiegel, jedoch mit höherem Rauschen. Diese sind mit einem Degenerationswiderstand versehen, damit sie nur 1% bis 2% des Gesamt-FET-Ruhestromes (etwa 30 μA) aufnehmen.

Dies reicht nicht aus, um signifikantes Rauschen einzuführen, erlaubt aber genug Einstellmöglichkeit, um eine Offsetspannung von 10 mV leicht zu senken. Wichtiger ist, dass sichergestellt ist, dass die parasitäre Kapazität des Potentiometers den Ausgang nicht beeinträchtigt. Somit bleibt das Rauschen dank der Splitting-Widerstände am Source-Anschluss (RS) gering. Die Offsetspannung lässt sich mit den Widerständen an Q2 und Q3 zuverlässig senken. Parasitäre Elemente der Potentiometer wirken sich nicht auf den Ausgang aus.

Bild 9 zeigt die Sprungantwort für die mit dem Stromspiegel getrimmte Version.

Digitalpotentiometer sind also eine einfache Möglichkeit, die Offsetspannung zu minimieren. Sie arbeiten in einem großen Bereich

von Umgebungstemperaturen und Spannungen, in dem der Offset minimiert werden kann. Die Eingangsoffsetspannung für den Ver-

stärker LSK389/ADA4897 wurde mit Hilfe eines 20-kΩ-Potentiometers AD5292 auf einige Mikrovolt reduziert. Der AD5292 enthält einen 20-mal programmierbaren Speicher, in dem sich die Schleiferposition nach der Einstellung der Offsetspannung permanent speichern lässt. In dieser Implementierung kam das Evaluation-Board des AD5292 zum Einsatz, um das Offset-Trimming-Potentiometer extern anzuschließen. Für kompaktere Schaltungen lässt sich das Digitalpotentiometer auf der Leiterplatte unterbringen und über seine integrierten seriellen Schnittstellenpins programmieren.

- Diskrete Verstärker optimieren

- Rauschquellen am Eingang

- Offsetspannung minimieren

- Offsetdrift minimieren