Zertifizierung von Multi-Core-Systemen

Sicher auf mehreren Kernen

Fortsetzung des Artikels von Teil 1

Wie stark bremst ein gemeinsamer Cache?

Der L1-Cache ist in der Regel in einen Datencache und einen Befehlscache unterteilt, während alle anderen Ebenen Daten und Befehle speichern. Die meisten Mehrkernprozessoren besitzen einen eigenen L1-Daten- und-Befehlscache für jeden Kern, während sich die Architektur der L2- und L3-Caches je nach Prozessorfamilie unterscheidet.

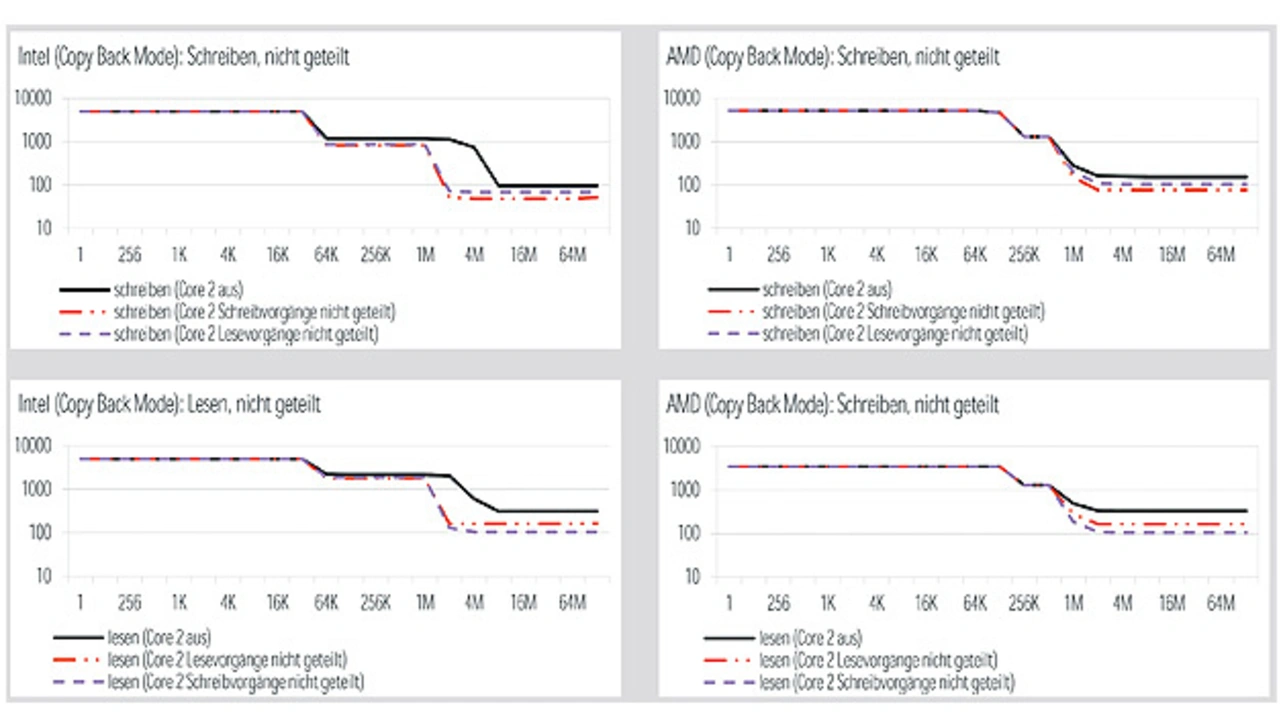

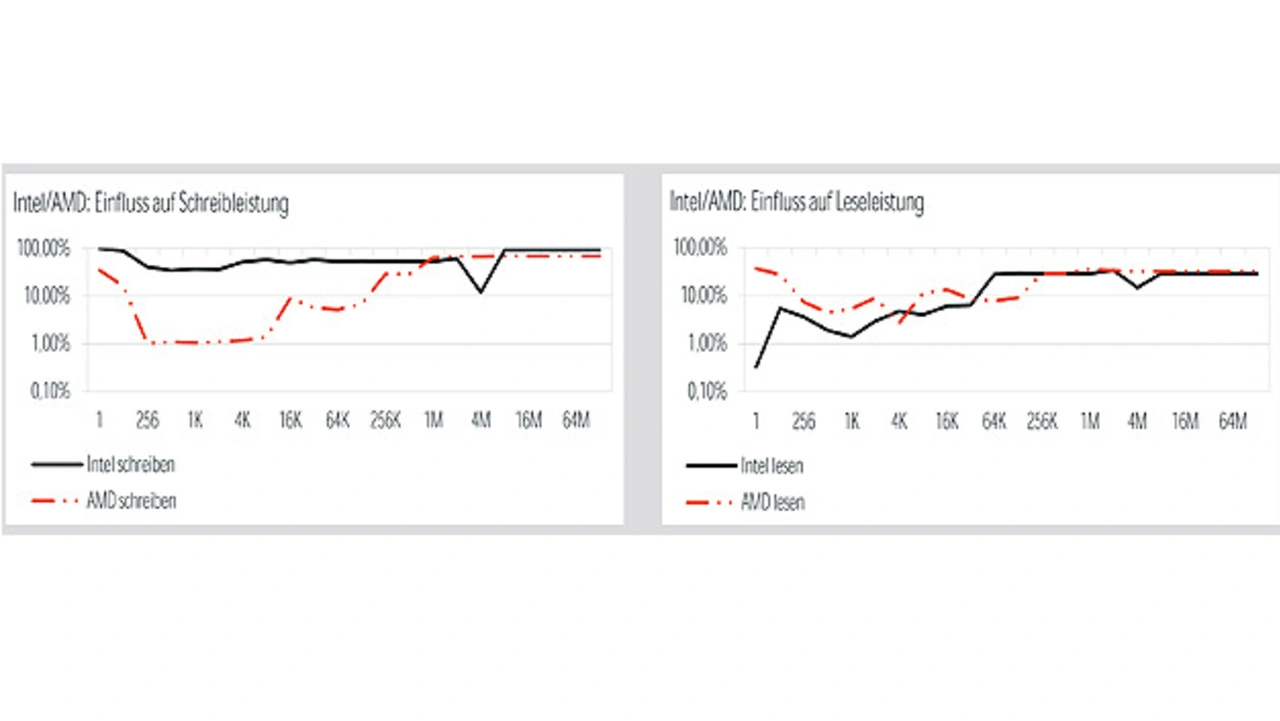

Gemeinsam verwendeter Cache ist in einem Mehrkernprozessor einer der Hauptgründe für Interferenzen. Ein Vergleich des Lese- und Schreibdurchsatzes zwischen Doppelkernprozessoren von Intel und AMD zeigt die Auswirkungen eines gemeinsam genutzten L2-Cache. Der Intel-Prozessor verfügt über einen eigenen L1-Cache für jeden Kern. Der L2-Cache wird von beiden Kernen gemeinsam benutzt. Der AMD-Prozessor besitzt getrennte L1- und L2-Caches für jeden Kern. Bild 2 zeigt die Ergebnisse für beide Prozessoren. Wenn der Datensatz klein genug ist, um in den (für jeden Kern eigenen) L1-Cache zu passen, zeigen der Intel- und der AMD-Prozessor keinen Leistungsverlust, wenn der zweite Kern aktiv wird. Wenn der Datensatz kleiner als der den Kernen zugängliche L2-Cache ist und dieser nicht gemeinsam genutzt wird (AMD-Prozessor), verursacht der zweite Kern ebenso keinen Leistungsabfall. Wenn der Datensatz jedoch kleiner als der für einen Kern verfügbare L2-Cache ist und der L2-Cache gemeinsam genutzt wird (Intel-Prozessor), hängt der Leistungsverlust durch den zweiten Kern von der Größe des Datensatzes ab und liegt zwischen 30 und 95 % für Schreibvorgänge und zwischen 19 und 92 % für Lesezugriffe. Die größte Auswirkung (92 %) ist dann festzustellen, wenn der Datensatz der Größe des L2-Cache genau entspricht. Mit einem Kern passen die Daten nämlich noch vollständig in den L2-Cache, während mit zwei Kernen alle Daten vom Speicher abgerufen werden müssen, was bedeutet, dass an dieser Stelle die Leistung des L2-Cache mit der Leistung des Speicherbusses verglichen wird. Ist der Datensatz deutlich größer als der L2-Cache, liegt der größte durch den zweiten Kern verursachte Leistungsverlust bei rund 50 % für Lese- und Schreibvorgänge.

Jobangebote+ passend zum Thema

Cache-Kohärenz

Ein weiterer wichtiger Aspekt bei der Cache-Verwendung ist die Konsistenz der lokalen Caches, die mit einer gemeinsam genutzten Ressource verbunden sind. In Mehrkernsystemen mit Unified Memory ist die Cache-Kohärenz von besonderer Bedeutung. Cache-Kohärenz bedeutet: „Wenn einer der lokalen Caches des Kerns CA einen Bezug zur physikalischen Ressource Px besitzt und der im Cache gespeicherte Wert aktueller ist als der in der Ressource Px gespeicherte, muss jeder Lesezugriff von jedem Kern (einschließlich dem Kern CA) den im Cache des Kerns CA gespeicherten Wert bereitstellen.“ Die Kohärenz zwischen den Caches wird mit Hilfe des Cache-Kohärenz-Protokolls aufrechterhalten.

Wenn beide Kerne nur lesen, zeigt der zweite Kern im Falle des Intel-Prozessors über den gesamten Datensatz-Bereich fast keine Auswirkungen auf die Leistung, während die Leistung beim AMD-Prozessor auf 50 % sinkt, wenn der Datensatz größer als der L2-Cache ist. Wenn beide Kerne nur schreiben, wird der Intel-Prozessor vom gleichzeitigen Schreiben viel weniger beeinträchtigt als der AMD-Prozessor. Die Abhängigkeit von der Datensatzgröße ist jedoch ähnlich (Bild 3).

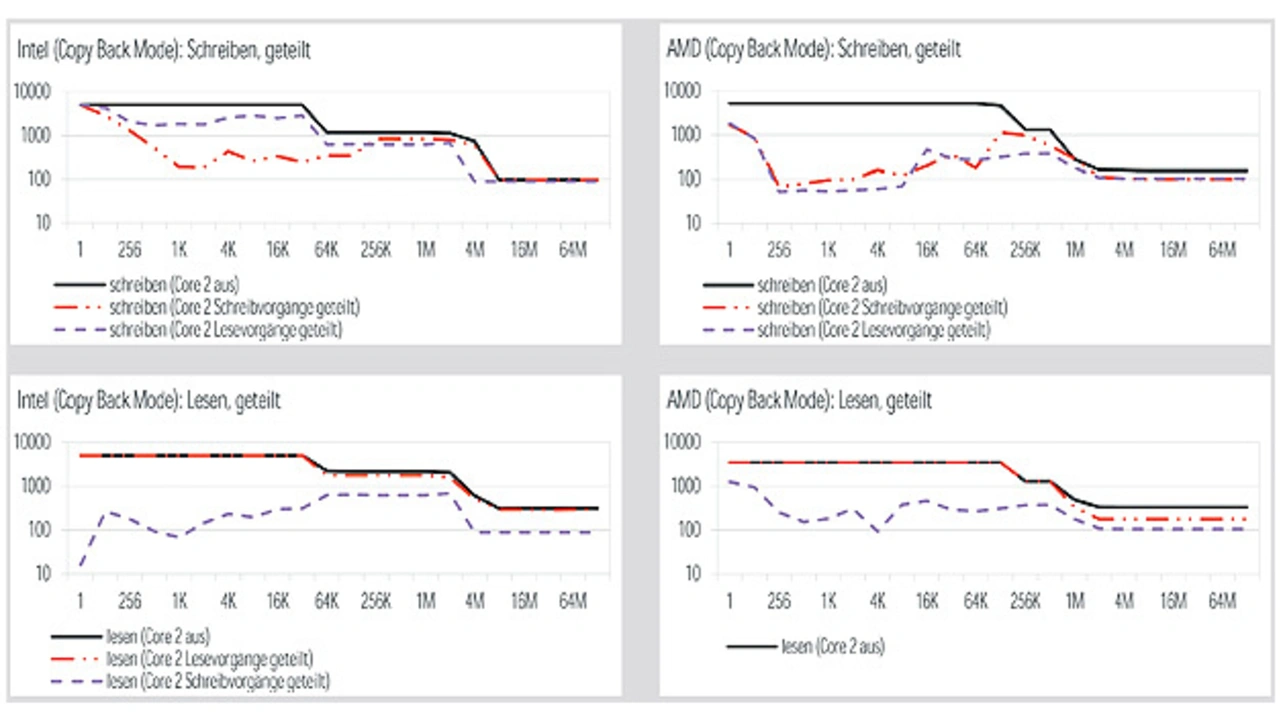

Wenn ein Kern denselben Datensatz liest, den der andere Kern schreibt, verhalten sich der Intel- und der AMD-Prozessor vollkommen unterschiedlich. Bild 4 zeigt den relativen Datendurchsatz für beide Prozessoren im Vergleich zum Datendurchsatz, wenn nur ein Kern aktiv ist. Beim Intel-Prozessor wird der schreibende Prozessor von einem gleichzeitigen Lesevorgang viel weniger beeinträchtigt als beim AMD-Prozessor. Der höchste Leistungsverlust erreicht jedoch ebenfalls 90 %, sollte die Datensatzgröße 4 MB betragen.

Beim AMD-Prozessor liegt der Leistungsverlust bei kleinen Datensätzen bei 99 %, bei großen Datensätzen bei rund 50 %. Vergleicht man den Einbruch der Leseleistung, dann stellt sich heraus, dass auf dem Intel-Prozessor das Lesen bei sehr kleinen Datensätzen beinahe vollständig blockiert wird. Beim AMD-Prozessor ist diese Auswirkung nicht zu beobachten. Werden die Datensätze größer, verhalten sich der Intel- und der AMD-Prozessor ähnlich. Für mittelgroße Datensätze beträgt der Verlust rund 90 % für beide Prozessoren.

Datenbusse, Interrupts – Engpässe im System

Die Ergebnisse der Leistungsmessungen (Bilder 2 und 3) zeigen, dass die Bandbreite des Speicherbusses zwischen den Kernen geteilt wird. Wenn die Kerne einen Datensatz bearbeiten, der so groß ist, dass die Caches keinen Einfluss haben, sinkt die Leistung auf 50 % ab, wenn beide Kerne aktiv sind. Dieselbe Wirkung wurde auf dem PCI-Bus gemessen. Während eine Cache-Trefferrate von 0 % beim Speicherzugriff sehr unwahrscheinlich ist, stellt sie auf dem PCI-Bus den Normalfall dar, da auf PCI-Geräte normalerweise mit deaktivierten Caches zugegriffen wird.

Die durch gleichzeitigen Zugriff auf gemeinsame E/A-Geräte hervorgerufene Leistungsminderung hängt hauptsächlich vom Bus ab, der das Gerät mit dem Prozessor verbindet (z.B. der PCI-Bus), sowie vom Gerät selbst. Ein Gerät, das nur eine Anfrage nach der anderen bearbeiten kann, kann eine zweite Anfrage für Hunderte von Mikrosekunden blockieren.

Auf einer Mehrkernplattform wird ein Hardware Interrupt in der Regel auf einen Kern geleitet. Sind mehrere Geräte mit einer Interrupt-Leitung verbunden und werden diese Geräte nicht vom selben Kern bedient, muss der Kern, der den Interrupt empfängt, diesen an den/die anderen Kern(e) weiterleiten und diese(n) dazu bringen, den Interrupt-Status seiner/ihrer Geräte zu überprüfen. Geteilte Interrupts können erhebliche Interferenzen zwischen den Kernen verursachen. Diese müssen durch ein geeignetes Plattformdesign verhindert werden.

- Sicher auf mehreren Kernen

- Wie stark bremst ein gemeinsamer Cache?

- Software-Interferenzkanäle

- Sicherheit kostet Prozessorzeit