Mikrocontroller-Entwicklungstools

Energiesparen vom Chip bis zur Software

Fortsetzung des Artikels von Teil 1

Die richtige Prozesstechnik

Für jedes Funktionspaket gibt es eine entsprechende Prozesstechnologie. Dabei sollte man sich nicht nur auf eine Technologie verlassen, die den geringsten theoretischen Leckstrom aufweist, nur weil der Baustein lange Zeit im Sleep-Modus verbringt. Im Sleep-Modus ist es möglich, die Stromzufuhr zu großen Bereichen der MCU zu deaktivieren, was die Komponenten mit Leckströmen aus der Gleichung herausnimmt. Leckströme sind ein großes Problem, wenn Schaltkreise aktiv sind. Dies lässt sich aber durch fortschrittliche Transistoren ausgleichen, die wesentlich effizienter schalten.

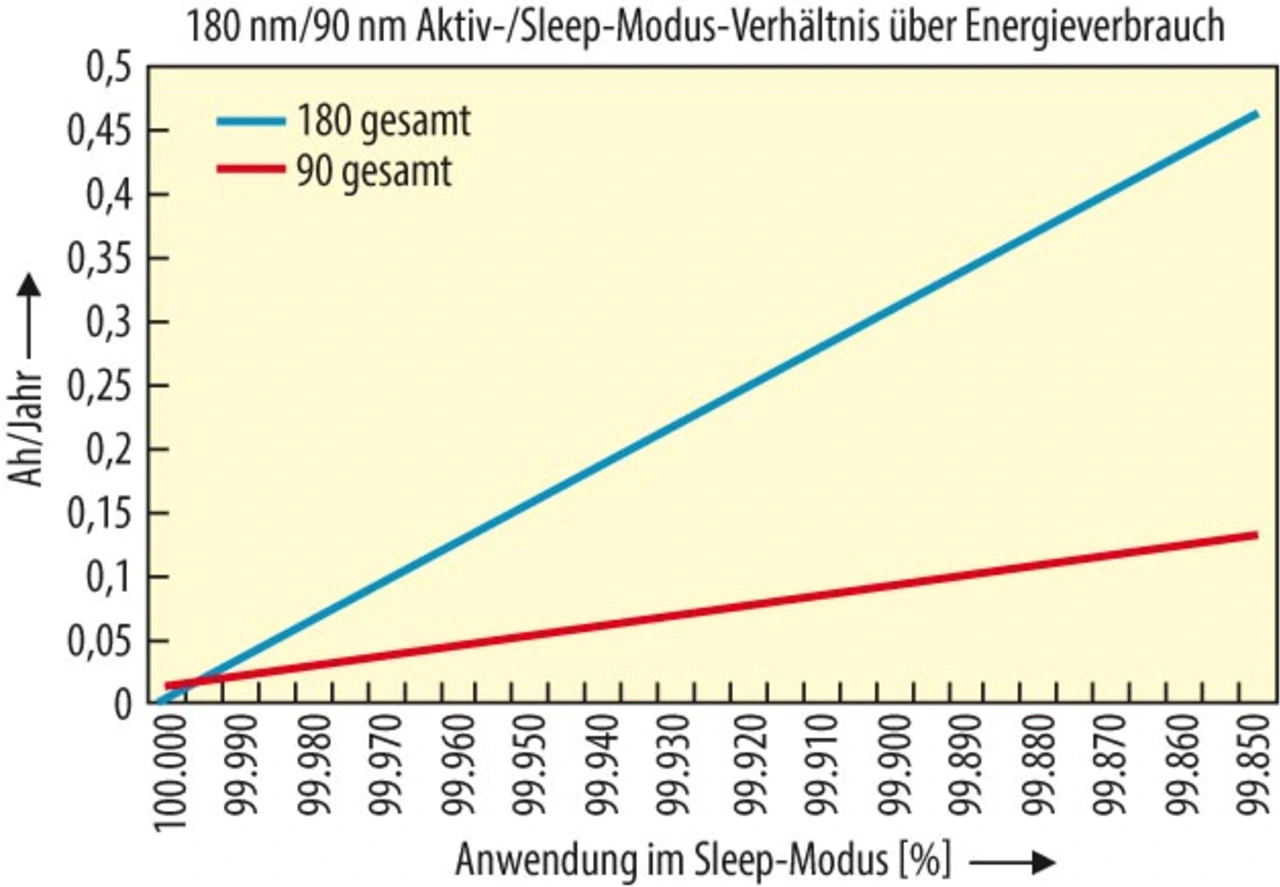

Der Leckstrom bei einem 90-nm-Prozess ist in etwa fünfmal höher als bei einem 180-nm-Prozess. Die Leistungsaufnahme im Aktivmodus ist um den Faktor 4 geringer – dieser basiert jedoch auf einem weitaus größeren Absolutwert. Eine 180-nm-MCU weist z.B. einen aktiven Stromverbrauch von 40 mA und einen Deep-Sleep-Stromverbrauch von 60 nA auf. Die Verbrauchswerte einer 90-nm-Implementierung weisen eine auf 10 mA verringerte aktive Stromaufnahme auf, dafür aber mit 300 nA eine höhere Stromaufnahme im Sleep-Modus.

Im vorigen Beispiel muss eine MCU in 90-nm-Technologie zu 0,0008 % der Zeit aktiv sein, um energieeffizienter zu sein. Anders gesagt: wenn das System eine Sekunde am Tag aktiv ist, ist die 90-nm-Version in etwa 1,5-mal energieeffizienter als ein 180-nm-Baustein. Darum muss bei der Wahl der Prozesstechnologie die Einschalt-/Aktivitätsdauer der Anwendung bekannt sein (Bild 2).

Jobangebote+ passend zum Thema

Nach der Wahl der geeigneten Prozesstechnologie hat der IC-Entwickler die Option, die Energieeffizienz weiter zu optimieren. Bei seiner Einführung wurde das Konzept des Clock Gating nur rudimentär angewendet. Clock Gating sorgt für ein komplexeres Design, da der Entwickler sich im Klaren sein muss, welche Logikpfade ein Taktsignal zu einem bestimmten Zeitpunkt benötigen.

Taktverteilung

Die meisten MCUs weisen eine hierarchische Struktur zur Verteilung der Taktsignale auf, zusammen mit den entsprechenden Spannungspegeln in jedem Teil des IC. Die Funktionseinheiten, wie die Befehlsverarbeitungsblöcke und Peripherie, sind in Gruppen organisiert. Jeder dieser Gruppen wird über ein eigenes Takt- und Stromversorgungsnetzwerk gespeist. Das Taktsignal für jede Gruppe stammt von einer gemeinsamen Taktquelle und einem Frequenzteiler oder -multiplizierer. Die Spannung für jede Peripheriegruppe wird über Leistungstransistoren und Spannungsregler bereitgestellt, wenn die Gruppen verschiedene Spannungen erfordern. Dieser Ansatz ist immer häufiger anzutreffen.

Um die Design-Komplexität zu verringern, verwenden MCUs ein relativ einfaches Clock-Gating-Schema, bei dem ganze Taktbäume deaktiviert werden können, solange keine Funktionseinheiten innerhalb einer Gruppe aktiv sind. Logik, die sich im Leerlauf befindet und keine nützliche Arbeit verrichtet, wird dabei aber wie die aktive Gruppe mit einem Taktsignal versorgt. So kann die Addierer-Einheit in einem CPU-Core getaktet werden, selbst wenn der aktuelle Befehl eine Verzweigung ist. Das durch das Taktsignal ausgelöste Schalten innerhalb der Addiereinheit erhöht den Energieverbrauch um den Faktor C·U²·f.

Verbesserte Design-Tools und Techniken erhöhen die Granularität des Clock Gating. Dabei erhalten die Peripherie- und Funktionseinheiten kein Taktsignal, wenn während dieses Zyklus keine Arbeit ausgeführt werden muss.

Spannungsskalierung ermöglicht weitere Energieeinsparungen, indem an eine bestimmte Gruppe von Funktionseinheiten bei Bedarf eine niedrigere Spannung geliefert wird. Dies geschieht mit Hilfe von integrierten Spannungsreglern oder DC/DC-Wandlern und Überwachungsschaltkreisen, die sicherstellen, dass der IC mit der erforderlichen Spannung arbeitet.

Stromversorgung und Skalierung der Rechenleistung

Integrierte Spannungsregler bieten dem Entwickler mehr Flexibilität. Ein integrierter Abwärts-Wandler (wie er in Silicon Labs’ SiM3L1xx-MCUs enthalten ist) wandelt die 3,6 V einer Batterie in 1,2 V um – bei einem Wirkungsgrad von mehr als 80 %. Viele MCUs bieten diese Funktion nicht und verwenden Linearregler, um die Spannung auf den erforderlichen Pegel zu wandeln – mit höheren Verlusten. In fortschrittlichen Implementierungen lässt sich der Abwärts-Regler abschalten, wenn die Batterie soweit entladen wurde, dass eine Wandlung keinen Sinn mehr macht. Die Stromversorgung lässt sich daher über der Lebensdauer auf mehr Energieeffizienz trimmen – und das mit Hilfe von Software.

Energieeffiziente Embedded-Anwendungen stützen sich auf ein Software-Design, das die Hardware-Ressourcen optimal ausnutzt. „Optimal“ bezieht sich dabei nicht nur auf die Anwendung, sondern auch auf die Hardware-Implementierung. Ebenso gilt: Je flexibler die Hardware in Sachen CPU, Takt, Spannung und Speichernutzung ist, desto größer ist das Energiesparpotenzial, das der Entwickler erzielen kann. Hardware-affine Software-Tools bieten Entwickler von Embedded-Systemen ein größeres Bewusstsein, welche Einsparungen möglich sind.

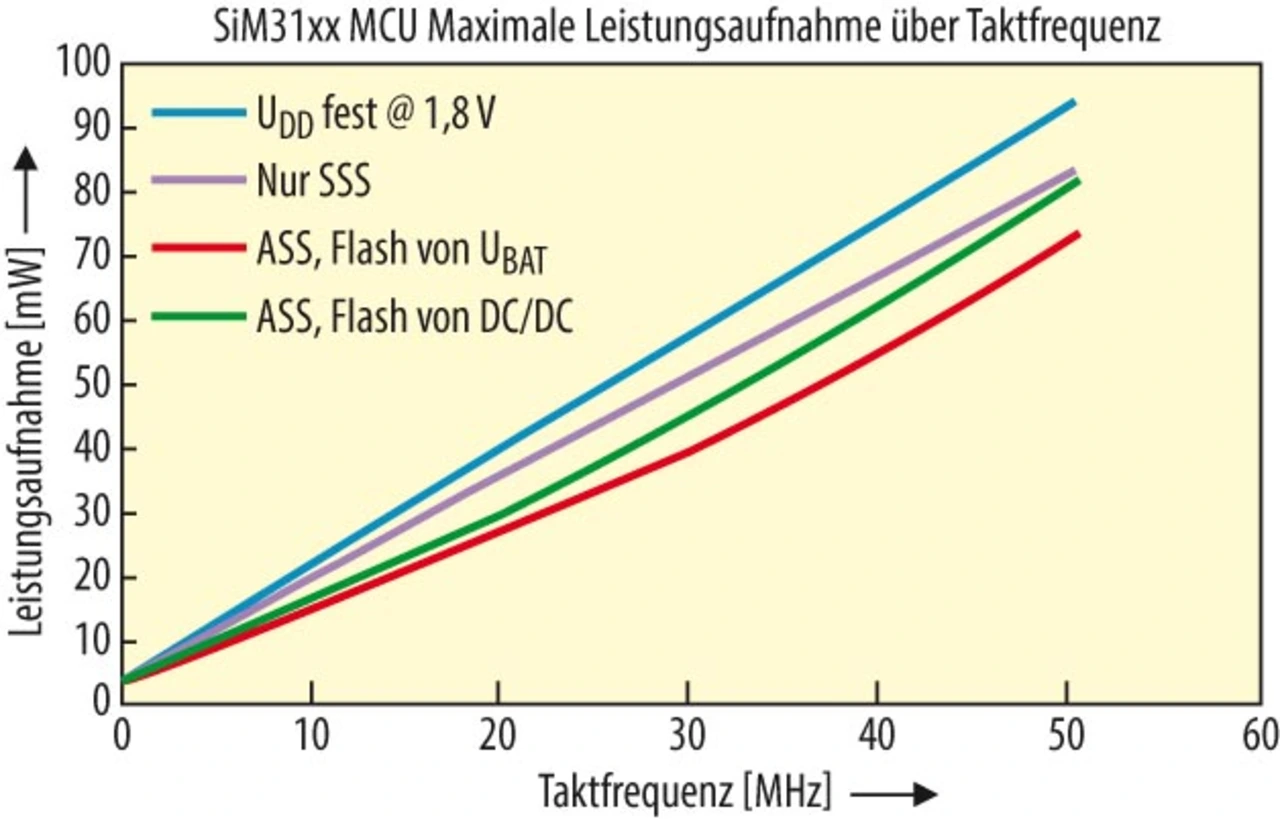

Eine Möglichkeit ist die dynamische Spannungsskalierung (Bilder 3 und 4). Auf dem Chip integrierte DC/DC-Wandler und Überwachungsschaltkreise verringern die Versorgungsspannung, sobald die Anwendung die Befehle nicht mehr mit höchster Geschwindigkeit ausführen muss. Unter diesen Umständen arbeitet das System mit einer geringeren Stromaufnahme. Der Vorteil: Die Eingangsspannung kann im Laufe der Produktlebensdauer variieren. Die folgenden Diagramme zeigen den Unterschied zwischen fehlender Spannungsskalierung (UDD fest), statischer Spannungsskalierung (SSS) und aktiver Spannungsskalierung (ASS).

Ein interessanter Nebeneffekt der aktiven Spannungsskalierung ist, dass sie sich je nach Eingangsspannung des Systems ändern lässt. In unserem Beispiel ist es effizienter, wenn die Eingangsspannung 3,6 V beträgt, um die interne Logik und den Flash-Speicher über den internen DC/DC-Wandler zu versorgen. Sinkt die Eingangsspannung, z.B. wenn sich die Batterie im Laufe der Zeit entlädt, ist es effizienter, das Flash-Speicher-Subsystem über die Eingangsspannung direkt zu versorgen, da die interne Logik bei niedrigeren Spannungen als der Speicher betrieben werden kann. Die SiM3L1xx-MCUs von Silicon Labs bieten eine flexible Versorgungsarchitektur mit sechs separaten und variablen Versorgungsdomänen, die jede Art von dynamischer Optimierung ermöglichen.

CMOS-Logikschaltkreise arbeiten langsamer, wenn deren Spannung verringert wird. Wenn die Anwendung eine geringere Rechenleistung tolerieren kann (meist bei der Bearbeitung von Kommunikationsprotokollen, die Daten mit einer Mindesttaktfrequenz erfordern), kann die quadratische Verringerung des Energieverbrauchs bei einer niedrigeren Spannung zu hohen Einsparungen führen. Leckströme stellen bei der Spannungsskalierung eine Untergrenze dar. Dauert jede Funktion zu lang, nehmen die Leckströme in der Energiegleichung überhand und erhöhen den Gesamtenergieverbrauch. Darum macht es Sinn, eine Funktion so schnell wie möglich auszuführen und den Prozessor anschließend in den Sleep-Modus zu versetzen. Dies minimiert den Leckstrom-Anteil.

Man nehme z.B. eine Anwendung mit Funksensor, die einen erheblichen Digitalsignal-Verarbeitungsaufwand erfordert: einen Glasbruchdetektor. Hier kommt die Fast-Fourier-Transformation (FFT) zum Einsatz, um die Vibrationen zu analysieren, die von einem Audiosensor an der Glasscheibe kommen (Glasbruch erzeugt charakteristische Frequenzen). Die FFT ist relativ komplex, so dass deren Ausführung bei einer niedrigeren Taktfrequenz (verursacht durch die verringerte Spannung) wahrscheinlich den Leckstrom erheblich erhöht. Und das selbst bei älteren Prozesstechnologien. Am besten ist dann die Befehlsausführung mit maximaler Taktfrequenz und die Rückkehr in den Sleep-Modus bis zu dem Zeitpunkt, an dem Ergebnisse an den Host berichtet werden müssen.

Der Funkprotokoll-Code stellt jedoch unterschiedliche Anforderungen. Funkprotokolle haben feste Timings für Ereignisse. In diesem Fall lassen sich die Protokolle vollständig in Hardware abwickeln. Es macht mehr Sinn, die Core-Spannung des Prozessors zu verringern. Der Code für die Paket-Zusammenstellung und -Übertragung läuft dann mit einer Geschwindigkeit passend zum Funkprotokoll.

Das Hinzufügen von Hardware-Blöcken wie Direct Memory Access (DMA) kann die Verbrauchsabwägung ebenfalls beeinflussen. Viele DMA-Controller, wie der des ARM-Cortex-M3-Prozessors, erfordern ein regelmäßiges Eingreifen des Prozessors. Intelligentere DMA-Controller ermöglichen dem Prozessor, Paket-Header zu berechnen, Daten zu verschlüsseln, Pakete zu erstellen und dann die Aufgabe der Paket-Übergabe in geeigneten Intervallen an die Speicher-Puffer des Funk-Frontends weiterzugeben. Die meiste Zeit, in der die Funkverbindung aktiv ist, kann der Prozessor im Sleep-Modus verbleiben, was Energie einspart.

- Energiesparen vom Chip bis zur Software

- Die richtige Prozesstechnik

- Speichernutzung

- Tools für mehr Energieeffizienz