Viel mehr als nur in die Höhe bauen

Wie wird 3D-NAND-Flash industrietauglich?

Hat früher „Bungalow-Größe“ mit der 2D-NAND-Technologie ausgereicht, muss man jetzt für Terabyte-Kapazitäten in die Höhe bauen. Doch wie meistert dieses „Hochhaus“ auch die harten Anforderungen industrieller Anwendungen? Ein Überblick.

Bei der 3D-NAND-Technologie stapelt man die Flash-Zelle in die dritte Dimension. Die Anzahl der Stockwerke oder Layer ist das Gütesiegel für das Beherrschen dieser Technologie. So gibt es bereits bis zu 96 Stockwerke im „Terabyte-Hochhaus“. Fehlerkorrektur, Aufbau der Flash-Zellen, verfügbare P/E Cycle bestimmen dabei die Statik.

Speichermedien in 2D-SLC- und MLC-NAND sind Entwicklern bestens bekannt. Ihr Einsatzbereich liegt heute vorwiegend im industriellen Bereich. Sie haben ihren Anteil am Gesamtmarkt erobert. Aufgrund der Kosten-Nutzen-Relation haben die Hersteller entschieden, hier keine weiteren Die Shrinks anzustreben. Somit ergeben sich nun Grenzen in puncto Kosteneinsparung und – vor allem bei MLC – Kapazitätssteigerungen. Es wird nun also erforderlich, für größere Speicherkapazitäten 3D-NAND industrietauglich zu machen.

Fehlerkorrektur war schon immer da

NAND–Flashes benötigen eine Fehlerkorrektur. Dies ist schon immer eine Anforderung der Flash–Hersteller an die NAND–Flash-Controller-Hersteller. Die Unterschiede liegen lediglich im Umfang, welcher betrieben werden muss, um Raw-Bit-Fehler zu korrigieren. Bei der 43-nm-Technologie (SLC) lag die geforderte ECC-Fähigkeit des Controllers bei 1 bit pro 512 Byte, bei 24 nm (SLC) bereits bei 8 bit pro 512 Byte. Hier werden Fehler erkannt und ggfs. korrigiert. Deutlich ausgeprägter sind die Steigerungen bei 2D-MLC- und 3D-TLC-Technologien. Ein funktionierendes ECC-Verfahren ist die Voraussetzung, dass die vom Flash-Hersteller minimal garantierten P/E Cycles erreicht werden können.

Verfügbare P/E Cycles

Vergleicht man die Anzahl der minimal garantierten P/E Cycles von 15-nm-2D-MLC mit der von 64-Layer-3D-TLC, sind diese mit 3000 P/E Cycles gleich. Erreicht wurde das für die 3D-NAND-Produkte durch die Vergrößerung der Strukturbreite und ein leistungsstärkeres ECC-Verfahren. Beim 2D-MLC kommt das BCH-Verfahren zum Einsatz. Dieses ist in der Lage, bis zu 72 Bitfehler pro 1 kB gelesener Daten zu erkennen und zu korrigieren.

Um bei 3D-NAND-Produkten ein vergleichbares Ergebnis zu erreichen, ist dieses ECC-Verfahren nicht mehr ausreichend. Deshalb kommt jetzt das stärkere LPDC-Verfahren zum Einsatz. Es ist in der Lage, bis zu 340 Bitfehler pro 2 kB gelesener Daten zu erkennen und zu korrigieren. Damit werden auch bei 3D-NAND-Produkten die 3000 P/E Cycles (oder 30.000 P/E Cycles im pSLC Mode) erreicht. Damit gelingt es, die gleiche Lebensdauer bei 3D-TLC- und 2D-MLC-Flash zu erreichen.

Aufbau der Flash–Zellen

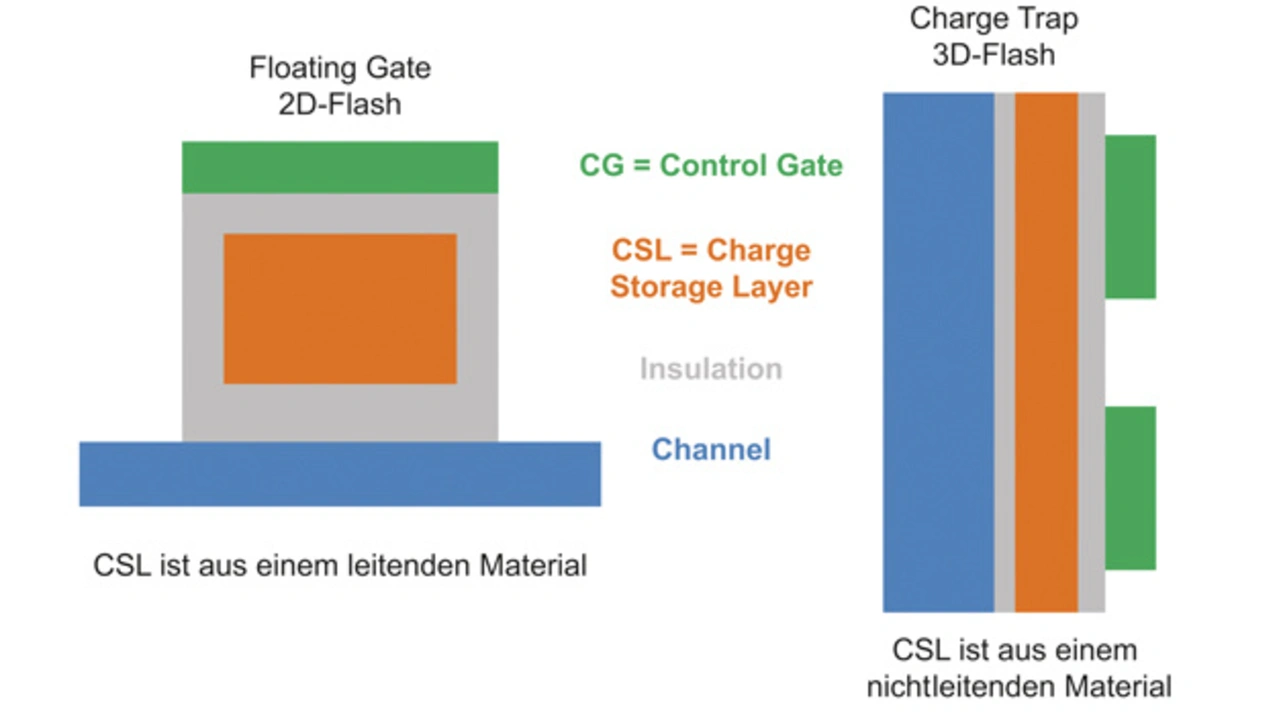

Eine weitere Veränderung, die mit 3D-NAND Einzug gehalten hat, ist der grundlegende Aufbau der Speicherzelle. Hier gab es bei Kioxia den Wandel vom Floating Gate zur Charge- Trap-Technologie. Um den Unterschied dieser beiden Technologien auf den Punkt zu bringen, muss man sich den Charge Storage Layer (CSL) anschauen.

Beim Floating Gate bestand diese Schicht aus einem leitenden Material, welches komplett von einer Isolationsschicht umgeben wird. Hierdurch konnten die gespeicherten Elektronen gehalten werden. Bei der Charge-Trap-Technologie besteht der CSL aus einem nichtleitenden Material (Bild 1). Deshalb ist eine komplette Umhüllung mit einer Isolationsschicht nicht nötig. Hieraus ergibt sich ein Vorteil bei der 3D-Fertigung. Der CSL kann als durchgehender Kanal gefertigt werden.

Jobangebote+ passend zum Thema

Die Charge-Trap-Technologie bei 3D-Flash bringt aber auch Herausforderungen mit sich, da sich die Elektronen in einer nichtleitenden Schicht (Insulation) nur schlecht bewegen können. Daher ist eine Charge Trap sehr gut geeignet, um Informationen in Form von Elektronen lange im CSL zu halten. Wird Information in einer Charge Trap gespeichert, so gelingt es nicht allen Elektronen, tief genug in den CSL einzudringen. Elektronen, die nur oberflächlich in den nichtleitenden CSL eingedrungen sind, werden diesen nach kurzer Zeit wieder verlassen. Die Information in der Speicherzelle beginnt sich zu verschieben. Man spricht dabei auch vom Fast Detrapping. Dieser Effekt führt zu einer erhöhten Anzahl an Raw Bit Errors, welche vor der Datenausgabe vom ECC korrigiert werden müssen. Hieraus entstehen spezielle Anforderungen, die der Controller für ein industrietaugliches Produkt beherrschen muss.

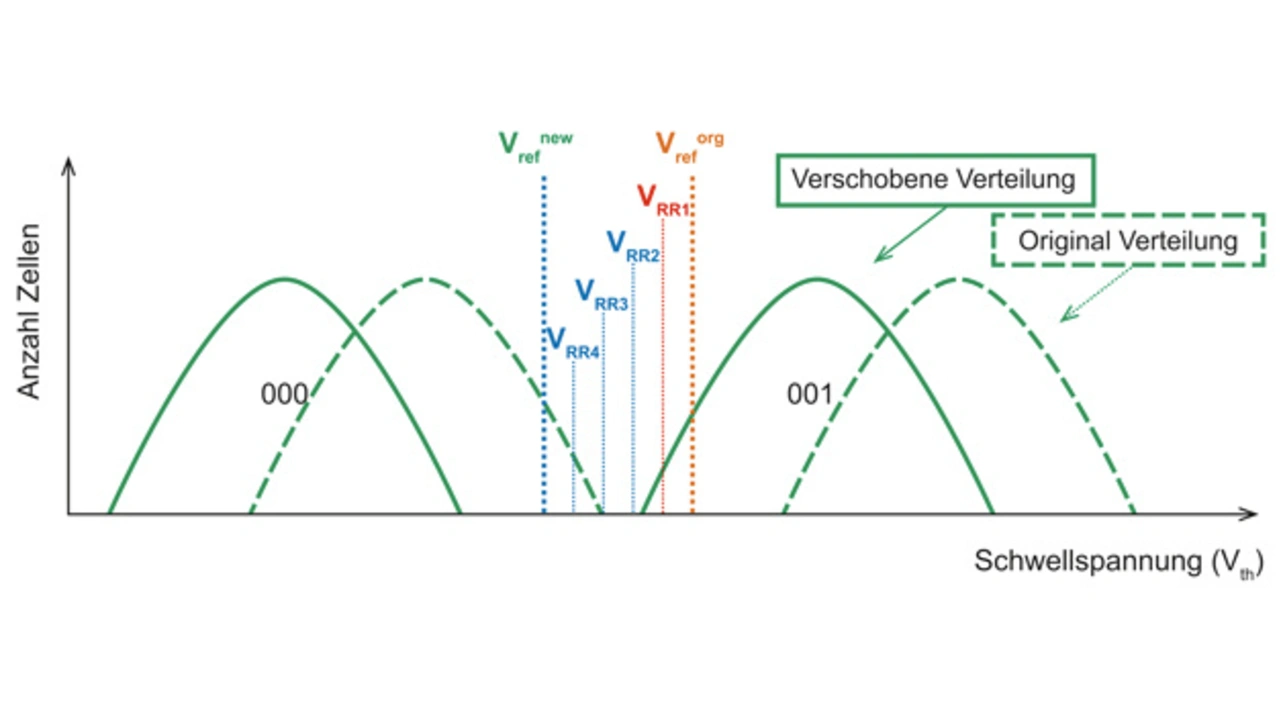

Um eine Information aus einer NAND-Flash Speicherzelle zu lesen, müssen Referenzspannungen angelegt werden (Bild 2). Darüber lässt sich der Informationsgehalt einer Speicherzelle eindeutig bestimmen. Durch das Fast Detrapping beginnt die Speicherzelle nach kurzer Zeit, Elektronen zu verlieren. Die Verteilung bewegt sich nach links, bei vorerst gleichbleibender Referenzspannung. Sobald Vreforg in den Bereich der Verteilung „001“ eintritt, kommt es zu Raw Bit Errors. Diese werden vom LDPC ECC erkannt und korrigiert.

Dabei nutzt das ECC die Fähigkeiten des Read-Retry- (RR) Algorithmus, welcher die Referenzspannung schrittweise versetzt, um die richtige Information zu ermitteln. Dies kann in mehreren Schritten erfolgen. Jeder Schritt ist eine Leseoperation und benötigt dementsprechend Zeit. Im gezeigten Beispiel werden Informationen ohne Raw Bit Errors erst dann gelesen, wenn VRR2 erreicht ist. Die optimale neue Referenzspannung Vrefnew liegt sogar noch ein paar Schritte weiter. Bis zu VRR2 gab es zwei zusätzliche interne Leseoperation, welche die Latenz erhöhen und die Lese-Performance reduzieren. Beginnt bei jeder Leseoperation für jede Speicherzelle der Durchlauf beim „alten“ Startpunkt Vreforg, kann dies gravierende Auswirkungen auf die Lese-Performance über den gesamten Speicher haben.

Diese Herausforderungen müssen für industrielle Anforderungen gemeistert werden. Deshalb setzt Xmore auf industrielle Flash Controller. Eine entsprechend entwickelte und getestete Firmware ist ebenso grundlegend wichtig. Im oben gezeigten Beispiel startet der RR-Algorithmus nicht bei jeder weiteren Speicherzelle beim ursprünglichen Startpunkt Vreforg. Die Firmware merkt sich den vorhergegangenen erfolgreichen RR-Schritt (VRR2) und beginnt jetzt bei diesem Punkt. Hierdurch werden deutlich weniger Raw Bit Errors gelesen. Auch die Anzahl der erforderlichen Korrekturen sinkt deutlich. Die Lese-Performance bleibt stabil auf hohem Niveau.

Fazit

Der Einsatz eines leistungsstarken Fehlerkorrekturverfahrens (LDPC) in Verbindung mit einem klugen RR-Algorithmus trägt dazu bei, dass 3D-TLC-NAND Flash in industriellen Speicherlösungen erfolgreich Einzug gehalten hat. Passende Flash Controller und die dazugehörige Firmware wurden entwickelt, um den Anforderungen von 3D-NAND gerecht zu werden. Die Bedürfnisse des industriellen Marktes können erfüllt werden. Die NAND-Flash-Hersteller wie z.B. Kioxia sind sich dessen bewusst und bieten qualitativ hochwertige 3D-NAND-ICs für den Einsatz im industriellen Temperaturbereich an. Xmore greift hierauf für seine industriellen Speicher gerne zu. Durch das Zusammenspiel dieser Schlüsselkomponenten ist 3D-NAND bereit für die Anwendung im industriellen Umfeld.

- Wie wird 3D-NAND-Flash industrietauglich?

- Glossar