Audi zFAS

Enorme Datenmengen bewältigen

Fortsetzung des Artikels von Teil 1

Aufbau und Bestandteile des zFAS

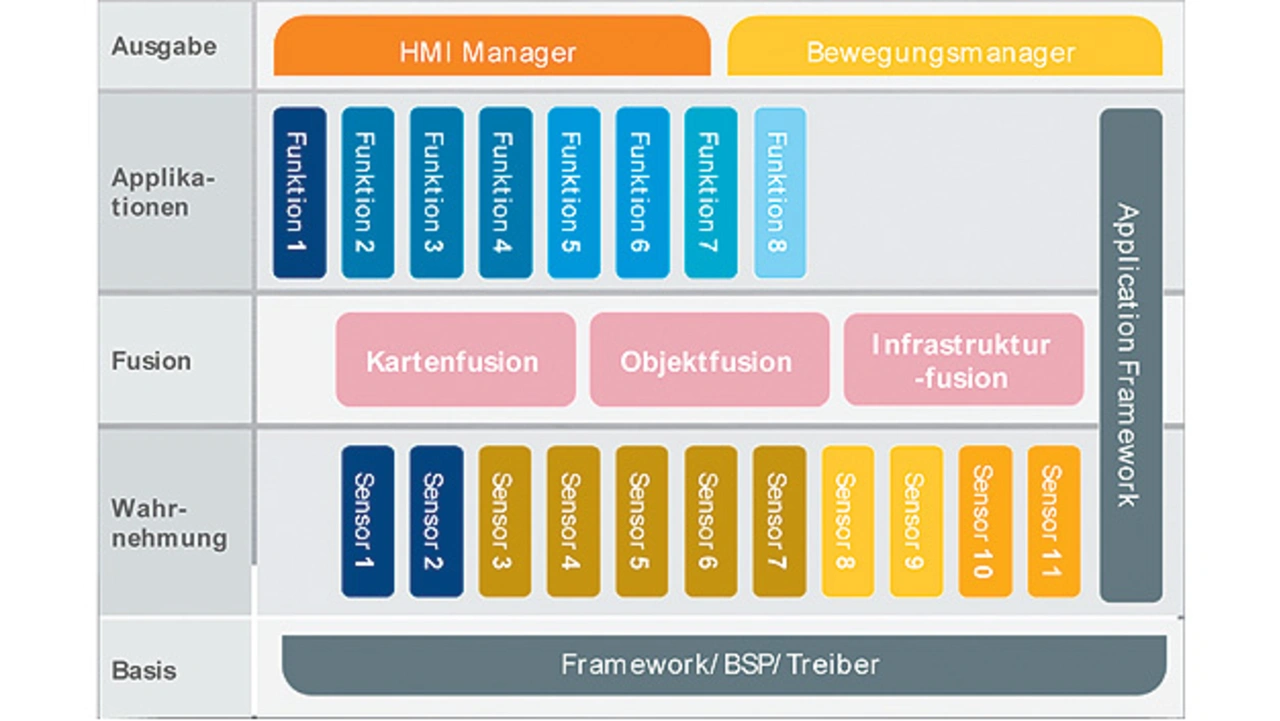

Der Aufbau der zFAS-Architektur (Bild 4) setzt sich im Wesentlichen aus drei Ebenen zusammen: Wahrnehmung, Fusion und Applikationen. Auf der Wahrnehmungsebene geht es um die Anbindung der verschiedenen Sensoren. Die Fusionsebene teilt sich wiederum in die drei Bereiche Objekt-, Karten- und Infrastrukturfusion auf. Darüber befindet sich die Applikationsebene, auf der zahlreiche Einzelfunktionen die Ergebnisse der Sensorfusion beispielsweise für die Quer- oder Längsführung nutzen. Die drei Fusionsarten stellen dabei unterschiedliche Anforderungen an die zFAS-Hardware:

- Objektfusion: Hier werden die ausgewerteten Sensorinformationen beispielsweise in Form von Objektlisten zusammengeführt. Dabei hat jedes Objekt gewisse Attribute, wie etwa eine Geschwindigkeit. Bei der Objektfusion spielen zudem Zeitstempel eine wichtige Rolle. Denn jeder Sensor erfasst zu bestimmten Zeitpunkten sein Umfeld. Das Steuerungssystem muss genau wissen, wann die einzelnen Signale jeweils detektiert wurden, um die Daten korrekt zusammenführen zu können. Alle zu einem Objekt gehörenden Informationen müssen dazu in einer gemeinsamen Darstellung zusammengebracht werden. Aus Hardware-Sicht handelt es sich bei der Objektfusion im Wesentlichen um einen sequenziellen Rechenvorgang.

- Kartenfusion: Anschaulich beschrieben bewegt sich ein Fahrzeug bei der Kartenfusion auf einem großen Schachbrett. Für jedes Feld wird bei der Fusion ermittelt, ob das Auto darüber fahren kann oder nicht. Dieser Vorgang erfordert die Berechnung großer paralleler Strukturen.

- Infrastrukturfusion: Hier geht es darum, Orte auf einer Navigationskarte um zusätzliche Informationen zu ergänzen. Wenn etwa ein Verkehrszeichen erkannt wird, wird es in die Karte eingetragen. Auch die Informationen der Frontkamera zur Spurerkennung fließen hier mit ein. Ziel der Infrastrukturfusion ist eine möglichst präzise Beschreibung der Fahrtstrecke vor dem Fahrzeug inklusive Kreuzungen, Abbiegungen und Verkehrsschildern. Wie bei der Kartenfusion finden hier überwiegend parallele Rechenvorgänge statt.

Um diese komplexen Aufgaben zu bewältigen, ist das zFAS mit mehreren Prozessoren und System-on-Chips (SoCs) ausgestattet. Im Wesentlichen gehören dazu die folgenden Chips:

- der Mobilprozessor Tegra K1 von Nvidia,

- das Bildverarbeitungs-SoC EyeQ3 von Mobileye,

- der Mikrocontroller Aurix TC297T von Infineon und

- das SoC-FPGA Cyclone V von Altera.

Auch TTTech ist mit seiner Lösung für deterministisches Ethernet eng in die Entwicklung des zFAS eingebunden. Die Fertigung des zentralen Steuergeräts erfolgt bei Delphi.

Aufgabenverteilung bei der Hardware

Die gesamte Rechenleistung der oben genannten Hardware-Komponenten entspricht ungefähr der Leistungsfähigkeit der kompletten Elektronikarchitektur eines gut ausgestatteten Mittelklasseautos. Dabei übernimmt jede Komponente spezielle Aufgaben. An besonders komplexe Applikationen sind allerdings auch mehrere zFAS-Bausteine beteiligt.

Der EyeQ3 etwa kümmert sich auf Basis der von Mobileye bereitgestellten Algorithmen um die Signalverarbeitung bei der Frontkamera. Für die Signale der vier Top-View-Kameras ist dagegen der Tegra K1 zuständig, der die parallele Verarbeitung großer Datenmengen beherrscht. „Wir haben uns für zwei verschiedene Prozessoren entschieden, weil wir sehr große Datenmengen verarbeiten müssen“, erläutert Vukotich. So fällt beispielsweise auch die Auswertung der Fahrerbeobachtungskamera in das Aufgabengebiet des K1. Beim pilotierten Fahren ist eine Überwachung des Innenraums notwendig, um sicherzustellen, dass der Fahrer wie vom Gesetzgeber gefordert jederzeit eingreifen kann – und nicht etwa Zeitung liest. Falls doch, würde der Fahrer aufgefordert, wieder die Kontrolle zu übernehmen, und die Pilotierungsfunktion deaktiviert.

Die Kartenfusion und wesentliche Teile aller anderen Fusionen laufen hauptsächlich über das FPGA Altera Cyclone, das ebenfalls bestens für eine massiv parallele Datenverarbeitung geeignet ist. Das Cyclone-FPGA ist zusätzlich für die Ethernet-Kommunikation und die Verarbeitung der Ultraschall-Sensorsignale zuständig. Die SoCs des zFAS sind über eine Ethernet-Lösung von TTTech miteinander verbunden. Die zentrale Zeitsteuerung übernimmt dabei das FPGA als eine Art Gateway.

Der Aurix TC297T wiederum verfügt über eine Lockstep-Architektur sowie eine spezielle Sicherheitsmanagement-Einheit, um Sicherheitsfunktionen bis ASIL D unterstützen zu können. Beim zFAS ist der Aurix u.a. für die Kommunikation nach außen zuständig. Er ist zudem mit in die Objektfusion eingebunden und vor allem laufen zahlreiche Funktionen der Applikationsebene auf dem Infineon-Mikrocontroller.

- Enorme Datenmengen bewältigen

- Aufbau und Bestandteile des zFAS

- Zusammenarbeit mit Halbleiterherstellern