Risiken im Industrieumfeld vermeiden

Funktionale Sicherheit einfach umsetzen

Fortsetzung des Artikels von Teil 1

Zufällige Bitfehler in der digitalen Logik: Zufällige Bitfehler kommen in der digitalen Logik und in den Speicherblöcken gelegentlich vor. In unserem exemplarischen Drucksensorsystem soll es beim Laden der vorgegebenen werksseitigen Offseteinstellung zu einem zufälligen Bitfehler kommen. Dieser Fehler ist nicht tolerierbar, da er den voreingestellten Offsetfehler des Systems verfälscht und sich auf das Umwandlungsergebnis auswirkt.

Bei den Functional-Safety-ADCs von ADI gibt es jedoch Funktionen, die in regelmäßigen Zeitabständen CRC-Prüfungen (Cyclic Redundancy Checks) der Speicher durchführen und dem Anwender etwaige Bitfehler melden. All diese Fehler lassen sich mit einem System-Reset beheben.

SPI-Übertragungsfehler: Bei jedem System, das Daten über ein Medium überträgt, kommt es während der Übertragung zu einigen Bitfehlern. Die Häufigkeit, mit der dies geschieht, wird mit der Bitfehlerrate (Bit Error Rate, BER) angegeben. In unserem Beispiel des Drucksensorsystems kann man von einem BER von weniger als 10–7 ausgehen, wenn die Übertragung an einen Mikrocontroller auf derselben Leiterplatte mit einer Distanz von 10 cm und durch digitale Isolatoren erfolgt. Nehmen wir an, dass elektromagnetische Störbeeinflussungen auf die SPI-Leitungen einwirken und zu einem Bitfehler bei der Übertragung des ADC-Umwandlungsergebnisses vom AD7768-1 zum Mikrocontroller führen. Ein Bitfehler in den ADC-Daten kann verheerende Folgen haben, wenn dadurch ein Druckaufbau im Gasbehälter unbemerkt bleibt. Mit einer CRC-Prüfung am Ankunftsort der übertragenen Daten können Anwender jedoch feststellen, ob während der Übertragung ein Bitfehler aufgetreten ist, um das ADC-Umwandlungsergebnis gegebenenfalls erneut zu prüfen.

Taktfehler am externen Master: Wenn Anwender Bedenken bezüglich der Unterdrückung der Netzfrequenz von 50 Hz beziehungsweise 60 Hz in einer Drucksensor-Anwendung haben, ist ein präziser und jitterarmer externer Master-Takt wichtig, um die Kerbe in der Kennlinie des digitalen Filters auf die richtige Frequenz einzustellen. Kommt es dazu, dass die Taktquelle nicht mehr verbunden, verschlissen oder beschädigt ist, so stellt dies ein Problem dar, da bestimmte Frequenzanteile des Stromnetzes dann in die konvertierten ADC-Daten durchschlagen können. Der External-Clock-Qualifier kann einen Fehler melden, wenn die externe Taktquelle nicht korrekt angeschlossen ist oder entfernt wurde. Daraufhin kann der Anwender Not-Umwandlungen mit dem internen RC-Oszillator durchführen, während an der externen Master-Taktquelle die notwendigen Wartungsmaßnahmen durchgeführt werden.

POR-Flag: Das POR-Flag im ADC wird gesetzt, wenn ein System hochgefahren oder erfolgreich zurückgesetzt wurde. Sollte es dagegen zu einem unerwarteten Reset kommen, können sich in den ADC-Daten unerwartete Ergebnisse einstellen. Mithilfe des POR-Flags lassen sich unerwartete Resets erkennen.

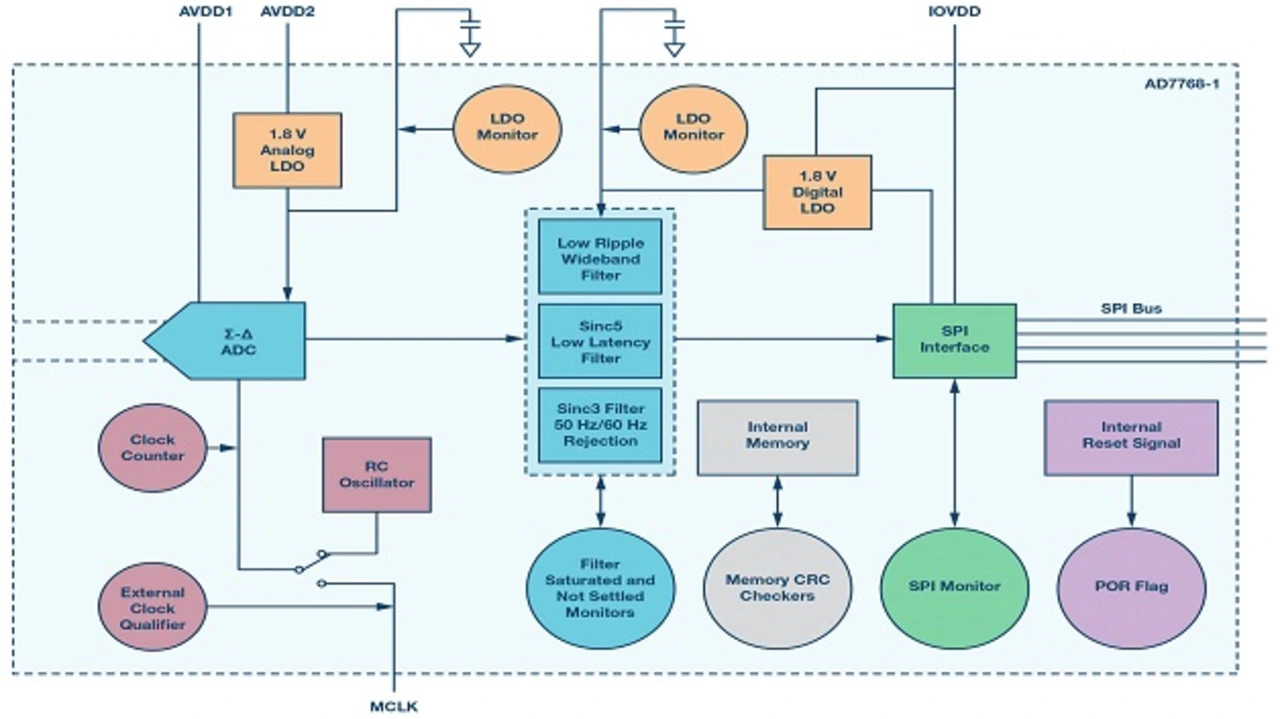

Bild 4 verdeutlicht, wie diese internen Diagnose-Merkmale des ADCs AD7768-1 an die Funktionen angeschlossen sind, die sie zu überwachen haben.

Funktional sicheres Datenerfassungssystem

Mithilfe der von dem Baustein AD7768-1 gebotenen Functional-Safety-Merkmale lässt sich das nachfolgend skizzierte Datenerfassungssystem realisieren. Nach dem Einschalten der Versorgungsspannung kann man die folgenden Sicherheitsfunktionen aktivieren:

- SPI-Integrity-Monitore,

- Überwachung des LDO-Ausgangspegels,

- Filtersättigungs-Monitor,

- External-Clock-Qualifier und

- CRC-Monitore für interne Logik und Speicher.

Systemkalibrierungen lassen sich ebenso wie die Ausgänge der LDO-Regler mit dem internen analogen Diagnose-Multiplexer validieren. Als nächstes haben Anwender die Möglichkeit, die Funktionen zum Anfügen des 8-Bit-Statusbytes an das Ende des 24-Bit-Datenstreams sowie des 8-Bit-SPI-CRC-Worts zu aktivieren. Der 8-Bit-CRC-Wert wird auf Basis des 8-Bit-Befehlsworts, des 24-Bit-Datenstreams und des 8-Bit-Statusworts berechnet. Sollten Anwender Bedenken wegen des damit einhergehenden Verarbeitungsaufwands haben, können sie den Continuous-Readback-Modus aktivieren, mit dem kein 8-Bit-Befehlswort angegeben werden muss. Stattdessen lässt sich der Inhalt der Datenregister durch Anlegen eines seriellen Takts an den Baustein auslesen, wie in Bild 6 gezeigt.

Das Resultat ist ein Datenerfassungssystem, dessen Verstärkungs- und Offsetfehler verifiziert wurden und das Diagnoseinformationen an den Anwender übergibt, sobald die ADC-Daten ausgelesen werden. Die Ausgänge des LDO-Reglers, die Eingänge des Analog-Front-Ends, die interne digitale Logik und der Speicher werden fortlaufend überwacht. Die Anwender haben die Gewissheit, dass die Integrität der SPI-Kommunikation und die Temperatur des IC bekannt sind. (kv)