Analyse von komplexen Bus-Link-Modellen

Mehr sehen mit dem Scope

Fortsetzung des Artikels von Teil 3

Link-Analyse-Techniken für DDR

Die Link-Analyse wurde für sehr schnelle serielle Anwendungen entwickelt, eignet sich jedoch auch für andere Fälle, wie z.B. DDR-Speicher. Normalerweise wird mit hochohmigen Tastköpfen auf DDR-Signale zugegriffen, was aber Reflexionen, die am Testpunkt sonst nicht vorhanden sind, verursachen kann. Mit der Link-Analyse-Software lässt sich nun aber eine Messung an anderen Testpunkten simulieren. Dabei können die durch die Messschaltung und die eigentlich unerwünschten Testpunkte des Signalzugriffs verursachten Reflexionen entfernt werden.

Jobangebote+ passend zum Thema

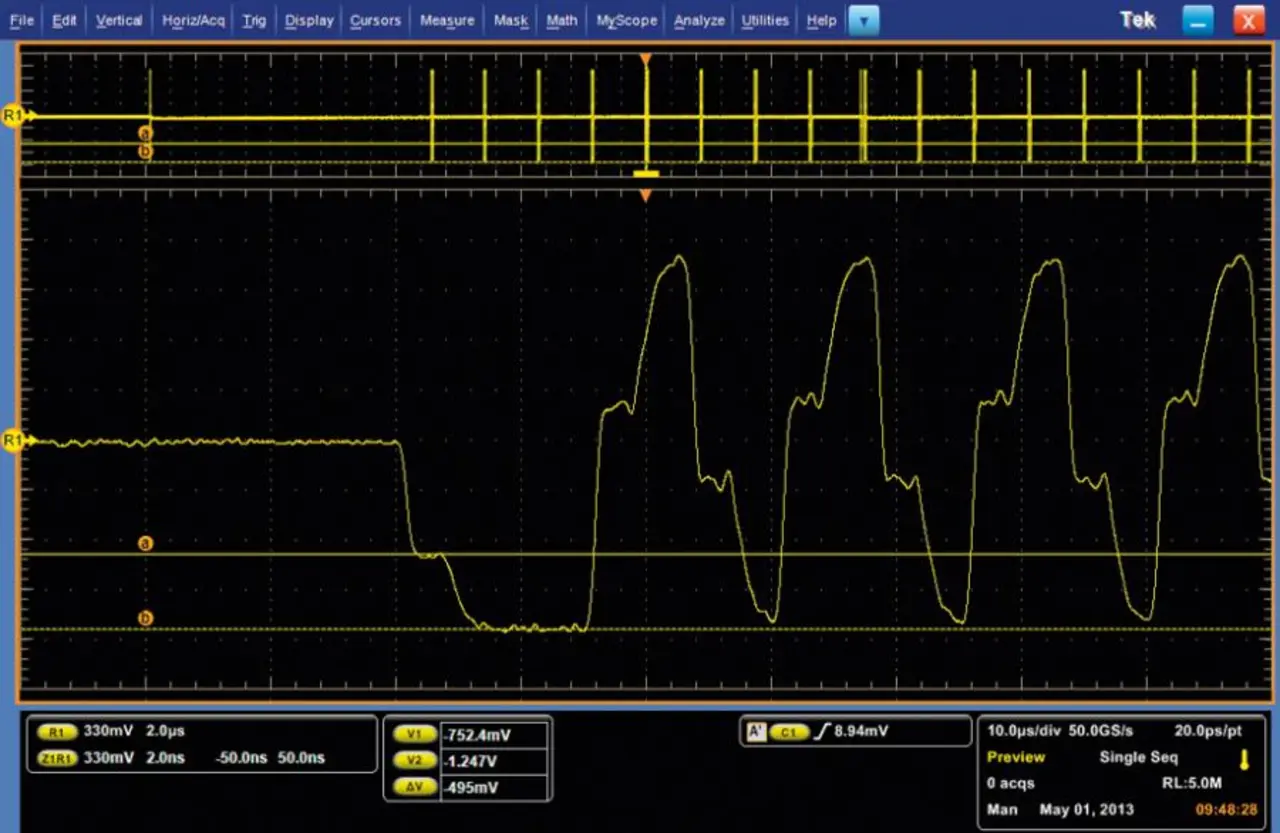

Ein typisches Szenario ist in Bild 7 dargestellt. Das erfasste Signal enthält deutliche Reflexionen durch eine Impedanz-Fehlanpassung zwischen der Übertragungsleitung und dem Eingang des Empfängers. Ohne eine Nachbearbeitung des erfassten Signals kann dieses nicht analysiert werden.

Wie bereits erwähnt, müssen für ein De-Embedding der Reflexionen die Modelle von Sender, Kanal und Empfänger bekannt sein. Es ist häufig schwierig, Modelle für alle Link-Komponenten zu erhalten. Dann lassen sich die obigen Annäherungen nutzen, um die Reflexionen beim erfassten Signal zu kompensieren. Die Verzögerung auf der Übertragungsleitung und die Last-Impedanz des Empfängers können durch einfache Zeit- und Spannungsmessungen geschätzt werden. Mittels Cursor lässt sich das Verhältnis von reflektierter zu eingespeister Spannung abschätzen:

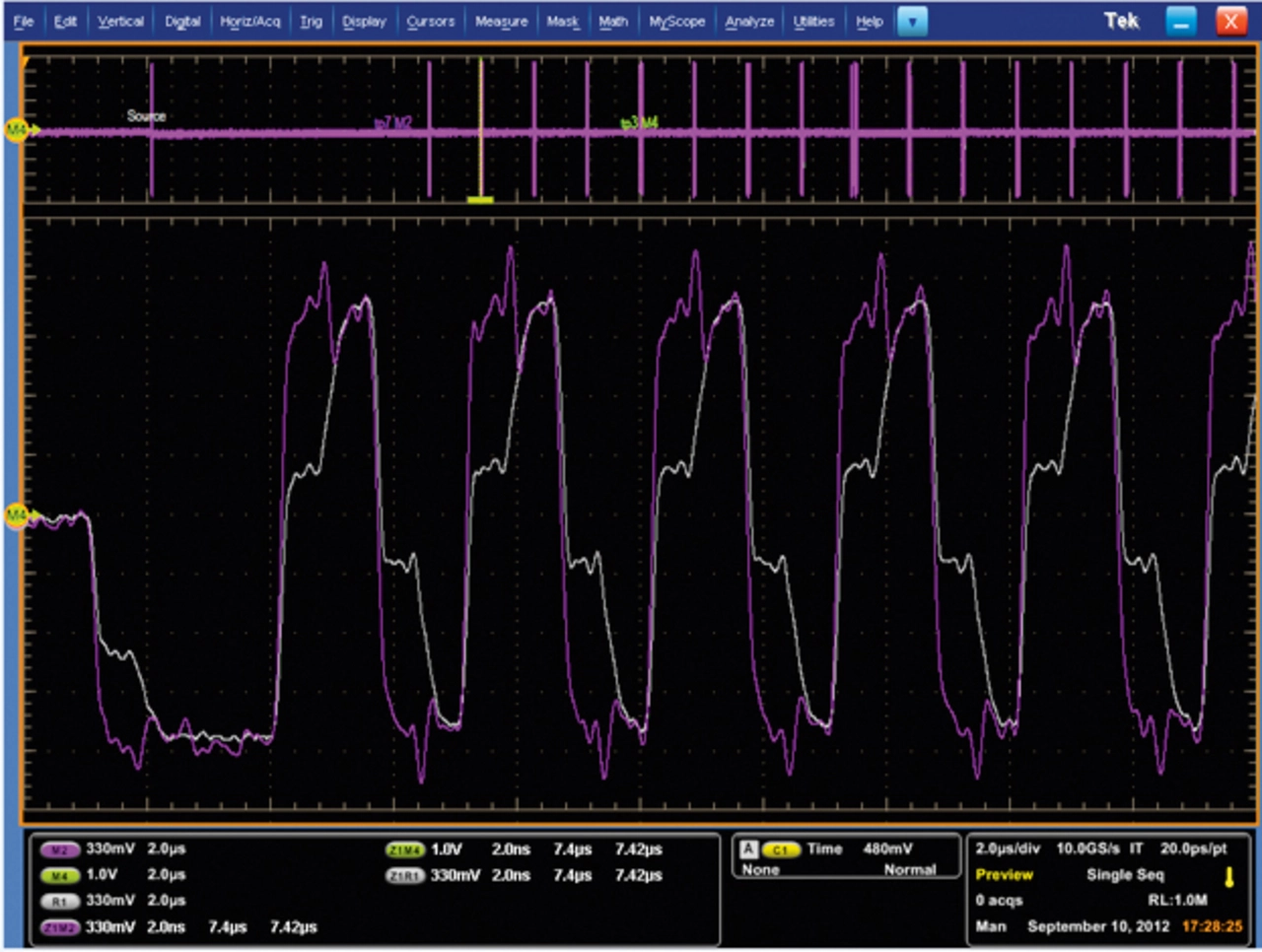

Für das in Bild 6 dargestellte Signal gilt: U2 = 1,2 V und U1 = 0,75 V. Dadurch kann die RX-Eingangsimpedanz auf 200 Ω geschätzt werden. Der nächste Schritt besteht darin, die Verzögerung auf der Übertragungsleitung von der physischen Position des Tastkopfs bis zum gewünschten Messpunkt zu schätzen. Mittels Cursor wird die Reflexion für Hin- und Rücklauf mit 660 ps ermittelt (Bild 8). Um die Zeit zwischen dem Tastkopf-Punkt und dem gewünschten Testpunkt zu ermitteln, muss dieser Wert durch 2 geteilt werden.

Mit den Link-Analyse-Tools kann der Testpunkt am Eingang des Empfängers geschätzt werden. Dies erfolgt durch die Spezifikation der Verzögerung auf der Übertragungsleitung, des Gehäusemodells des Empfängers und der Eingangsimpedanz des Empfängers. In diesem Fall wurde das Gehäusemodell des Empfängers durch ein Viertor-S-Parameter-Modell definiert. Mit genauen Modellen des Senders, des Empfängers und der Übertragungsleitung wären genauere Endergebnisse möglich (Bild 9). Allerdings sind die durch die oben genannte Technik ermittelten Ergebnisse ausreichend genau, um eine Analyse des Signals einschließlich der Messungen und Protokoll-Dekodierung durchzuführen.

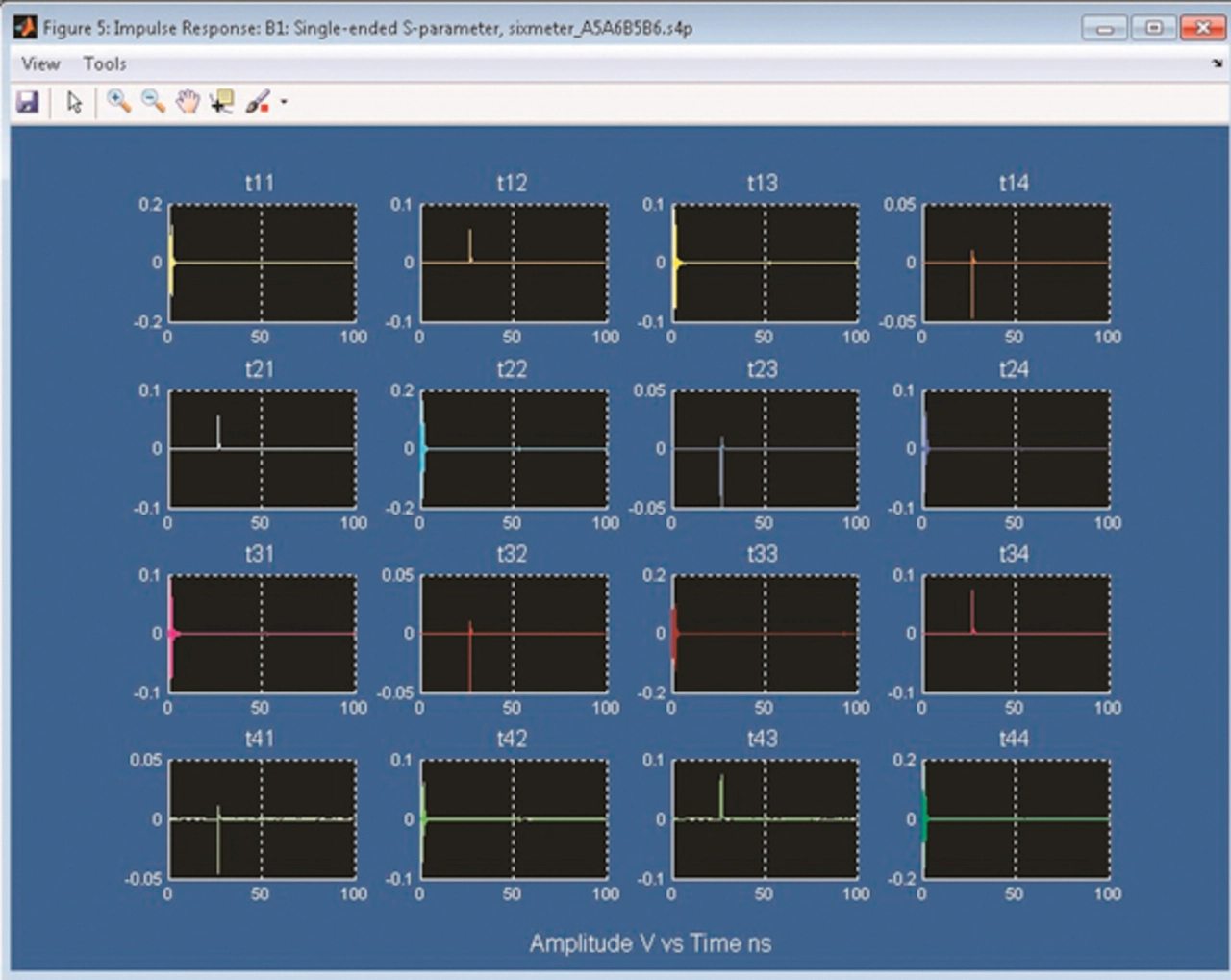

Eine Darstellung der Impulsantwort im Zeitbereich von jedem der oben beschriebenen S-Parameter-Vektoren ist unten in Bild 10 zu sehen. Dies liefert einen wertvollen Einblick, da so die Verzögerungen der Übertragungsterme sichtbar sind. Zudem zeigt dies, ob die Daten im Zeitintervall stabil sind, was für einen gültigen Satz von S-Parametern notwendig ist. Diese Darstellungen ergeben sich durch eine IFFT-Berechnung der S-Parameter-Daten im Frequenzbereich. Zudem ist oftmals eine Extrapolation der Daten im Frequenzbereich bis DC und manchmal auch eine Extrapolation auf eine höhere gewünschte Nyquist-Frequenz notwendig.

Letztlich wird eine robuste SDLA (Serial Data Link Analysis) immer wichtiger, da die Geschwindigkeiten zunehmen und die Baugrößen, Geometrien und Halbleiterstrukturen immer kleiner werden. Solche Analyse-Anwendungen ermöglichen dann eine Live-Oszilloskop-Darstellung von Signalen an simulierten Testpunkten. Mittels S-Parametern und Übertragungsleitungs- und RLC-Modellen lässt sich somit die Signal-Übertragungsfunktion für jeden Testpunkt erstellen. An jedem Testpunkt lassen sich dann verschiedene Funktionen ausführen, wie z.B. Protokoll-Decodierung, Jitter- und Augen-Analyse sowie mathematische Funktionen. Dies ist einfach mit Hilfe der Link-Analyse-Software auf Echtzeit-Oszilloskopen möglich, zum Beispiel den DPO/MSO-Geräten der Serie 70K von Tektronix. Der SDLA Visualizer ermöglicht dann ein De-Embedding der kompletten Messschaltung, die Simulation des Embedding einer Schaltung und die Entzerrung eines Empfängers. Der SDLA Visualizer mit DPOJET-Jitter- und Augen-Analyse stellt schließlich eine umfassende Simulations- und Messumgebung für Computer-, Kommunikations- und Speicher-Busse zur Verfügung.

Der Autor

|

Dean Miles

|

|---|

|

ist Senior Technical Marketing Manager bei Tektronix und für das High-Performance-Produktportfolio verantwortlich. Dean ist seit mehr als 20 Jahren für das Unternehmen tätig und hatte in dieser Zeit verschiedene Positionen inne, wie Global Business Development Manager für HF-Technologien und Business Development Manager für die Optical Business Unit. Dean hat bislang weltweit in mehr als 80 Ländern neue Technologien präsentiert und dabei mehr als 10.000 Ingenieure getroffen. |

- Mehr sehen mit dem Scope

- Sicherstellung korrekter Testtoleranzen

- Charakterisierung auf der Empfängerseite

- Link-Analyse-Techniken für DDR