4 x 100G-Datennetze

Metadaten sichern schnelle Netze

Fortsetzung des Artikels von Teil 1

Unterscheidungsmerkmale zwischen FPGAs

Ein wesentliches Unterscheidungsmerkmal der FPGA-Familie Stratix 10 GX ist Intels »Hyperflex«-Architektur, mit der die steigenden Anforderungen an den Datendurchsatz in heutigen Hochgeschwindigkeitsdesigns berücksichtigt werden. Hyperflex bietet eine Leistungsfähigkeit und Energieeffizienz, die mit herkömmlichen FPGA-Architekturen einfach nicht möglich ist.

Jobangebote+ passend zum Thema

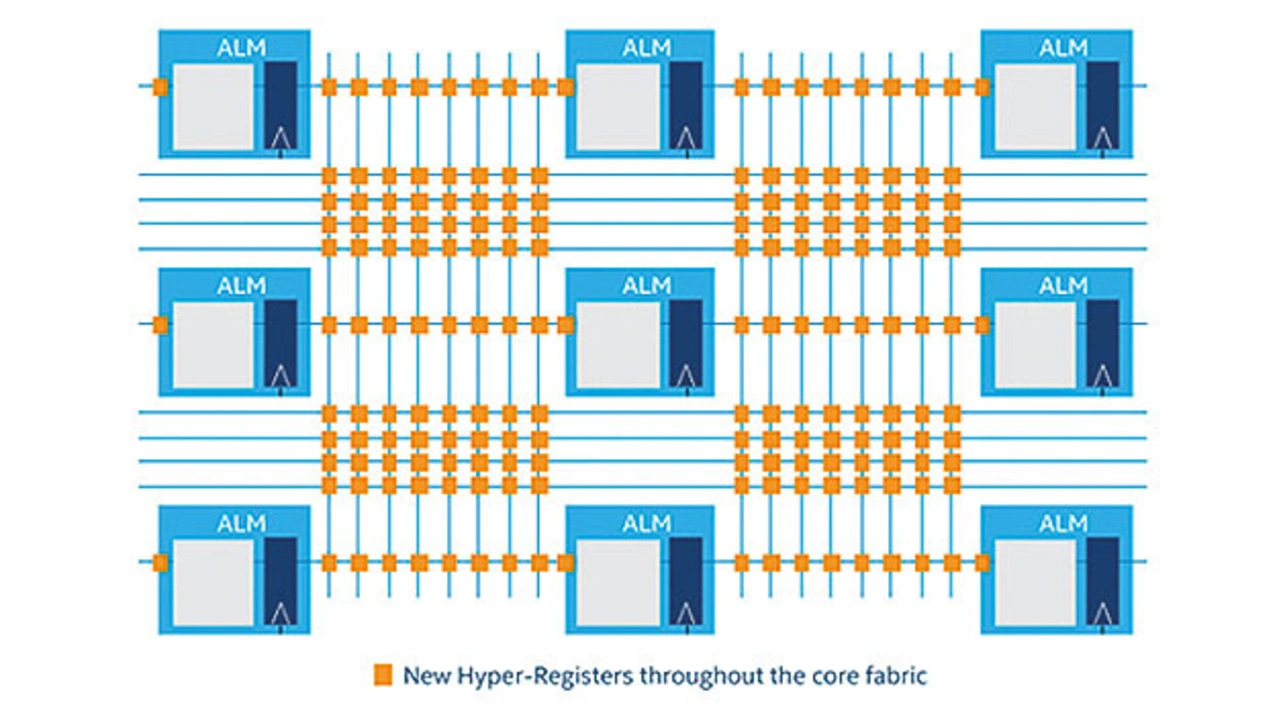

Die Hyperflex-FPGA-Architektur führt zusätzliche Bypass-Register in der gesamten FPGA-Verdrahtung ein. Diese Hyper-Register befinden sich auf jedem Interconnect-Routing-Segment und an den Eingängen aller Funktionsblöcke (Logik-, Speicher-und DSP-Blöcke). Sie unterscheiden sich von den herkömmlichen Registern, die in den ALMs (Adaptive Logic Modules) enthalten sind (Bild 4).

Mithilfe dieser Hyper-Register können FPGA-Entwickler Register neu terminieren, um kritische Pfade zu beseitigen; Pipeline-Register hinzufügen, um Routing-Verzögerungen zu beseitigen, und das Design auf höchste Leistungsfähigkeit trimmen. Dieser Ansatz bedeutet auch, dass alle Logikressourcen des FPGA für Logikfunktionen verfügbar sind, anstatt in herkömmlichen Architekturen als Durchgangszellen geopfert zu werden. Die Entwicklungstools können automatisch den optimalen Registerort auswählen und die Überlastung des Routings verringern.

ASICs sind eine Alternative zu FPGAs. Wie erwähnt, weisen ASICs festverdrahtete Funktionen auf, und FPGAs bieten Flexibilität, die Nutzern das einfache Ändern ihrer Designs ermöglicht – entweder nach dem Einsatz oder im Voraus – sofern sich die Spezifikationen ändern. Bei der 4 x 100G-Probe nutzt Telesoft FPGAs, um Upgrades vor Ort zu ermöglichen. Dies ist wichtig, da sich der Netzwerkverkehr selbst sowie die Informationen, an denen Kunden interessiert sind, ständig weiterentwickeln. Mit einem FPGA können die Entwickler von Telesoft ihren Probe neu programmieren, um Metadaten zu extrahieren, die Funktion für aktuelle Netzwerk- verkehrsprotokolle beschleunigen und neue Funktionen bereitstellen.

Die Perspektive der Daten

Um redundante Metadaten zu entfernen, werden mithilfe eines Frontend-Entduplizierungsmoduls alle als Duplikate identifizierten Pakete entfernt. Duplikate können aus verschiedenen Gründen auftreten, z.B. bei erneuten Übertragungen, einer nicht optimalen Netzwerkinfrastruktur oder einfach durch Überwachen des Netzwerks an mehreren Abgriffspunkten.

Pakete werden in Echtzeit enttunnelt – wenn ein Tunnel vorhanden ist, wird dieser automatisch erkannt und der eingekapselte Verkehr freigelegt. Für vollständige Sichtbarkeit werden in diesem Fall die Metadaten für das äußere Tunnelprotokoll und für den darin eingekapselten Verkehr extrahiert.

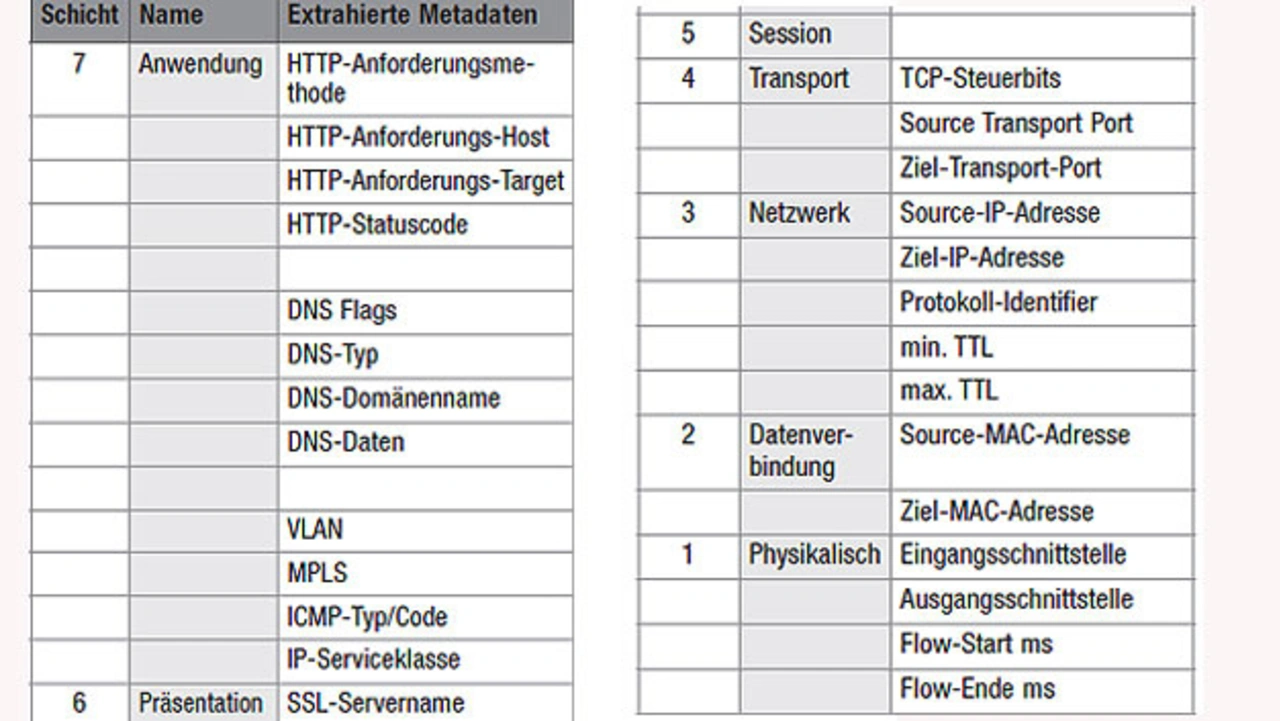

Die Metadatenextraktion ist funktionsreich und extrahiert Daten aus allen Layern des TCP/IP-Modells (Transmission Control Protocol), bis einschließlich der Anwendungsebene, wo die HTTP-Anforderungsmethode, der Host, das Target und der Statuscode an den Host gesendet werden. Darüber hinaus werden DNS-Pakete identifiziert und an den Host weitergeleitet, damit dieser DNS-Flags, Typ und Domänennamen extrahieren kann (Tabelle 2).

Um eine schnelle Host-Datenverarbeitung zu ermöglichen, werden die Metadaten über mehrere DMA-Warteschlangen (Direct Memory Access) an den Host übermittelt. Jede Warteschlange wird unabhängig von einem eigenen Host-Thread bedient. Das FPGA führt einen bidirektionalen datenflusssicheren Lastausgleich über die DMA-Warteschlangen durch und stellt so sicher, dass alle Pakete, die einem bestimmten uni- oder bidirektionalen Fluss zugeordnet sind, an dieselben Host-Verarbeitungs-Threads gesendet werden.

Die Host-DMA-Datenerfassung erfolgt über das DPDK-Framework (Data Plane Development Kit) für x86/64 und über die Schnittstelle »rte_ethdev«. Das DPDK wird wegen seiner Unterstützung für Lock-Free-Parallelität bevorzugt.

Da die Arbeitslast des Host sehr hoch sein kann, werden die Host-Anwendungen mithilfe der Intel-Compiler für C++ erstellt und verwenden verschiedene Funktionen der Intel Integrated Performance Primitives (Intel IPP), um die Leistungsfähigkeit zu maximieren. Zusätzlich zu diesen Funktionen verwendet die Anwendung auch SSE4.2- und AVX2-spezifische Befehlssatzerweiterungen, um bestimmte Rechenaufgaben auf Intel Xeon-CPUs zu verlagern, wann immer dies möglich ist.

Der Host führt eine zusätzliche Verarbeitung der Paket-Metadaten durch, um die Datenflusssätze (Data Flow Sets) mit zusätzlichen Metadaten anzureichern. So kann der Host eine Suche nach IPv4/IPv6-Adressbereichen anhand eines live programmierten Baums von CIDRs (Classless Inter-Domain Routings) durchführen, die Metadaten für Geolokalisierung, AS- und IP-Reputation-Metadaten bereitstellen. Da jeder dieser Faktoren zeitlich gebunden ist, kommt es darauf an, diese Abgleiche zum Zeitpunkt der Aufnahme durchzuführen.

Literatur:

[1] https://www.intel.com/content/www/us/en/products/programmable/fpga/new-to-fpgas/resource-center/overview.html vom 11. April 2019.

[2] Cisco: https://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-networking-index-vni/white-paper-c11-741490.html vom 14. Oktober 2019

Die Autoren

Claire Huckerby-Brown

ist eine staatlich geprüfte Ingenieurin und hält einen Batchelor-Grad in Elektrotechnik von der Universität Bath, Großbritannien. Derzeit ist sie als Field Application Engineer für FPGAs bei Intel PSG tätig. Huckerby-Brown verfügt über 15 Jahre Erfahrung mit FPGAs und war zuvor als ASIC-Entwicklerin bei einem großen Halbleiterhersteller tätig

Richard Parks

besitzt einen Master in Elektrotechnik von der Universität Southampton, Großbritannien, und ist derzeit FPGA Team Leader bei Telesoft Technologies. Parks arbeitet seit mehr als zehn Jahren auf den Gebieten Hardwarebeschleunigung und FPGA-Anwendungen.

- Metadaten sichern schnelle Netze

- Unterscheidungsmerkmale zwischen FPGAs