Speichermarkt

Steigende Preise und Aufbruch in die dritte Dimension

Fortsetzung des Artikels von Teil 1

Vorstoß in die dritte Dimension

Einige Hersteller stoßen deshalb bereits in die dritte Dimension vor. So haben Micron und Samsung das Hybrid Memory Cube Consortium gegründet. Die Grundidee des Hybrid Memory Cube (HMC) besteht darin, DRAM-Dies übereinander zu stapeln und über Through Silicon Vias zu verbinden. Die unterste Ebene dieses Stacks bildet ein dedizierter Logik-Chip. Micron will mit der Lieferung von Mustern ihrer 2-GBit-Versionen im Herbst dieses Jahres starten.

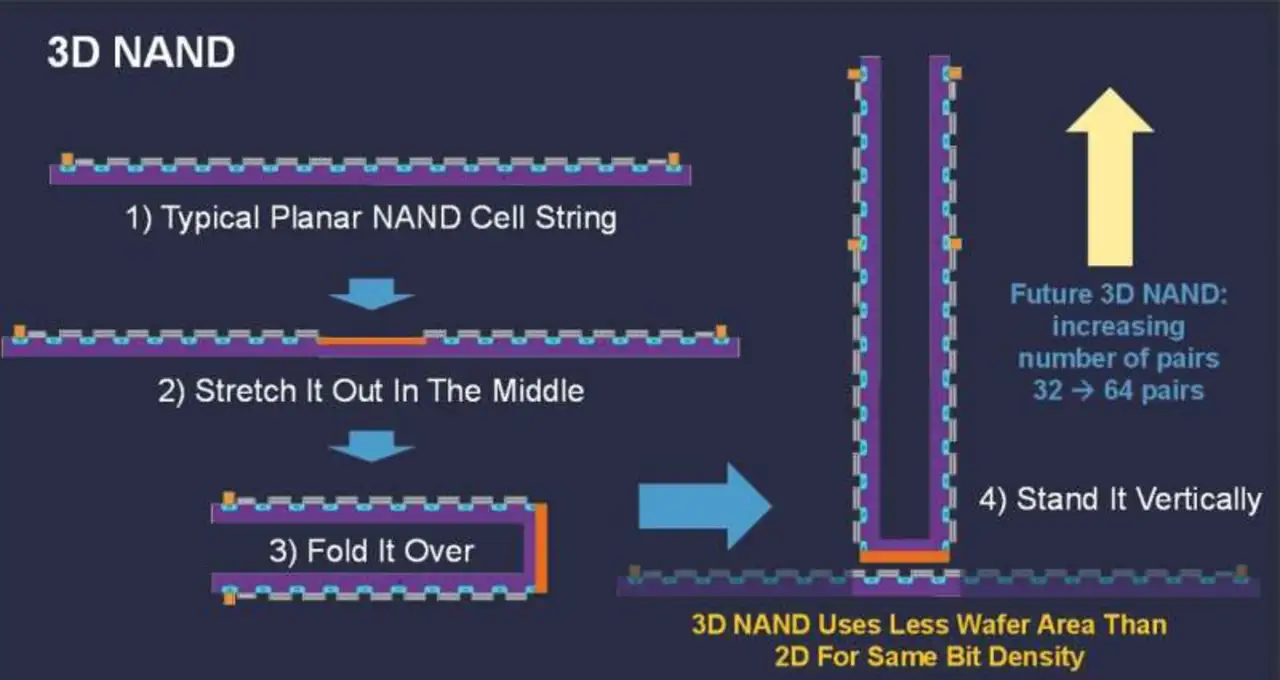

Auch die Hersteller von nichtflüchtigen Speichern gehen jetzt in die dritte Dimension, allerdings stapeln sie nicht dies übereinander sondern »falten« die NAND-Strings, so dass sie nicht planar parallel zum Wafer liegen, sondern um 90 Grad nach oben verdreht. So lassen sich viele Schichten übereinander legen. Erst kürzlich hatte Samsung den Start der Massenproduktion der der dreidimensionalen Vertical NAND-Flash-Speicher verkündet. Sie basieren auf einer Kombination aus der 3D-Charge-Trap-Flash-Technik und vertikaler Interconnects. Laut Samsung erreichen die Speicher gegenüber den herkömmlichen planaren NAND-Speichern auf Basis von 20-m-Prozessen die doppelte Dichte und gemessen an 10-nm-NAND-Flash-Zellen sogar die doppelte Schreibgeschwindigkeit. Das Schöne an der 3D-Technik: Die Lithografie stellt für die Speicherdichte nicht mehr den limitierenden Faktor dar. Die Speicherkapazität erhöht sich einfach über zusätzliche Schichten in der dritten Dimension. Samsung startet mit der Fertigung von 128-GBit-Typen sieht sich aber schon auf gutem Weg zum 1-TBit-Flash-Speicher.

Auch Toshiba setzt auf 3D-NAND-Speicher und hat ihre Technik auf den Namen »Pipe shaped Bit-Cost-Scalable« (p-BiCS) getauft. Muster will das Unternehmen noch in diesem Jahr auf den Markt bringen, die Fertigung in Stückzahlen soll nächstes Jahr starten.

IM Flash Technologies, das Joint-venture zwischen Intel und Micron, arbeitet ebenfalls an dreidimensionalen NAND-Flash-Speichern und rechnet damit, dass die ersten 3D-Versionen parallel zu den planaren Typen auf Basis der 15-nm-Prozesstechnik auf den Markt kommen werden. Während die Lithografie bei den 3D-NAND-Speichern nicht mehr den limitierenden Faktor darstellt, liegen die neuen Herausforderungen darin, dass Materialien gefunden werden müssen, die die hohen Temperatur-Budgets vertragen, die die Multilayer-Proezesse mit sich bringen. Außerdem müssen vertikale Kanäle mit hohem Öffnungsverhältnis (bis zu 80 : 1 laut Applied Materials) sehr präzise geätzt werden, wie Kevan Esfarjani, Vice President Technology & Manufacturing von Intel und Co-CEO von IM Flash Technologies, kürzlich auf dem IMEC Technology Forum erklärte.

Auf 3D-Techniken setzt auch Monolithic 3D. Das Unternehmen strukturiert die aktiven Schichten auf Wafern, spaltet sie über Ion-Cleaving vom Mutterwafer ab und bondet sie dann auf einem zweiten Wafer übereinander. Das hat laut Monolithic 3D gegenüber der herkömmlichen Through-Silicon-Via-Technik einige Vorteile und lässt sich auf NAND-Speicher genauso wie auf DRAMs oder Logik-ICs anwenden.

Ein ganz neuer Ansatz, um die Skalierungsschwierigkeiten der NAND-Speicher zu umgehen, stellen Alternative nichtflüchtige Techniken wie MRAMs (Magnetic RAMs), PCMs (Phase Change Memories) oder FeRAMs (ferroelektrische RAMs) dar, denen allerdings der Durchbruch auf breiter Front noch nicht gelungen ist. Kürzlich machte eine weitere Alterative von sich reden: Resistive RAMs, kurz ReRAMs. Die Grundidee besteht darin, dass ein Material durch Anlegen einer Spannung zwischen einem leitenden und einem nichtleitenden Zustand schalten kann. Damit ähnelt der ReRAM dem PRAM, erreicht aber schnellere Schaltgeschwindigkeiten. Auch an der ReRAM-Technik arbeiten die großen Speicherfirmen wie Toshiba, Sandisk und Panasonic (früher auch Elpida und Sharp). Im Februar 2012 hatte Rambus die Firma Unity für 35 Mio. Dollar übernommen, ein Start-up, der ReRAMs entwickelt hat und letztes Jahr noch guten Mutes war, schon 2014 einen TBit-Speicher vorstellen zu können.

Ebenfalls ab 2014 will die 2010 gegründete Crossbar ihrer ReRAM-Technik anbieten. Der vollständig CMOS-kompatible Prozess skaliert laut Crossbar bis hinunter zu 5 nm. Außerdem erlaubt diese Technik auch das 3D-Stacking, um höhere Speicherdichten zu erreichen. Zunächst zielt Crossbar auf den Einsatz als Embedded Memory in Controllern ab. Reine Speicherchips hoher Kapazität - auch Crossbar visiert die TBit-Region an - sollen dann in wenigen Quartalen folgen. »Wir sind an einem Wendepunkt angelangt, alle Hersteller arbeiten an Alternativen zu den herkömmlichen planaren DRAM- und NAND-Speichern: Auch wenn heute noch nicht feststeht, welche Technik den Durchbruch schafft so steht doch fest, dass wir demnächst eine solche neue Technik brauchen«, sagt Gerd Schauss von Samsung.

Jobangebote+ passend zum Thema

- Steigende Preise und Aufbruch in die dritte Dimension

- Vorstoß in die dritte Dimension