Mikrocontroller

XMOS - der Echtzeit-Prozessor

Fortsetzung des Artikels von Teil 1

Power Management ohne Kunstgriffe

Um den Stromverbrauch bei geringer Auslastung des Systems zu senken, wird auf gängigen 32-bit-Systemen ein entsprechendes Power Management implementiert, welches die Taktrate der Befehlsverarbeitung senken oder ganz einfrieren kann und alle Peripheriebaugruppen je nach Anforderungen mehr oder weniger funktionslos schalten kann. Während ersteres meist relativ einfach zu handhaben ist, insbesondere bei Prozessoren, die einen entsprechenden Halt-Befehl kennen, ist für das Power Management in den Peripherietreibern einiger Aufwand anzusetzen.

Beim XS1 entfällt die Notwendigkeit, Power Management zu implementieren, schlicht dadurch, dass es keine Peripheriebaugruppen gibt. Die einzelnen -Threads eines Kerns werden automatisch schlafen gelegt, sobald sie auf definierte Ereignisse warten. Sobald alle Threads eines bestimmten Kerns schlafen, stellt dieser selbstständig die Bearbeitung von Opcodes ein, senkt den Takt der System-Clock auf eine zuvor konfigurierte Rate (Active Energy Conservation) und somit den Stromverbrauch deutlich.

Jobangebote+ passend zum Thema

Ein typisches System, basierend auf einem XS1-G4 (4 Kerne, 400 MHz, etwa die Hälfte der Ports in Betrieb) weist eine maximale Stromaufnahme von etwa 1.820 mA auf (www.xmos.com/published/power-consumption-xs1-g-devices). Noch deutlich sparsamer ist beispielsweise ein System mit Single-Core XS1-L1 (500 MHz, ebenfalls etwa die Hälfte der Ports benutzt). Die maximale Stromaufnahme liegt hier bei 246 mA, im Active Energy Conservation Mode (System Clock 20 MHz) hingegen nur bei 24 mA. Der tatsächliche durchschnittliche Verbrauch liegt je nach Verwendung anteilig dazwischen (www.xmos.com/published/power-consumption-xs1-l-devices).

Kurze Latenzzeiten

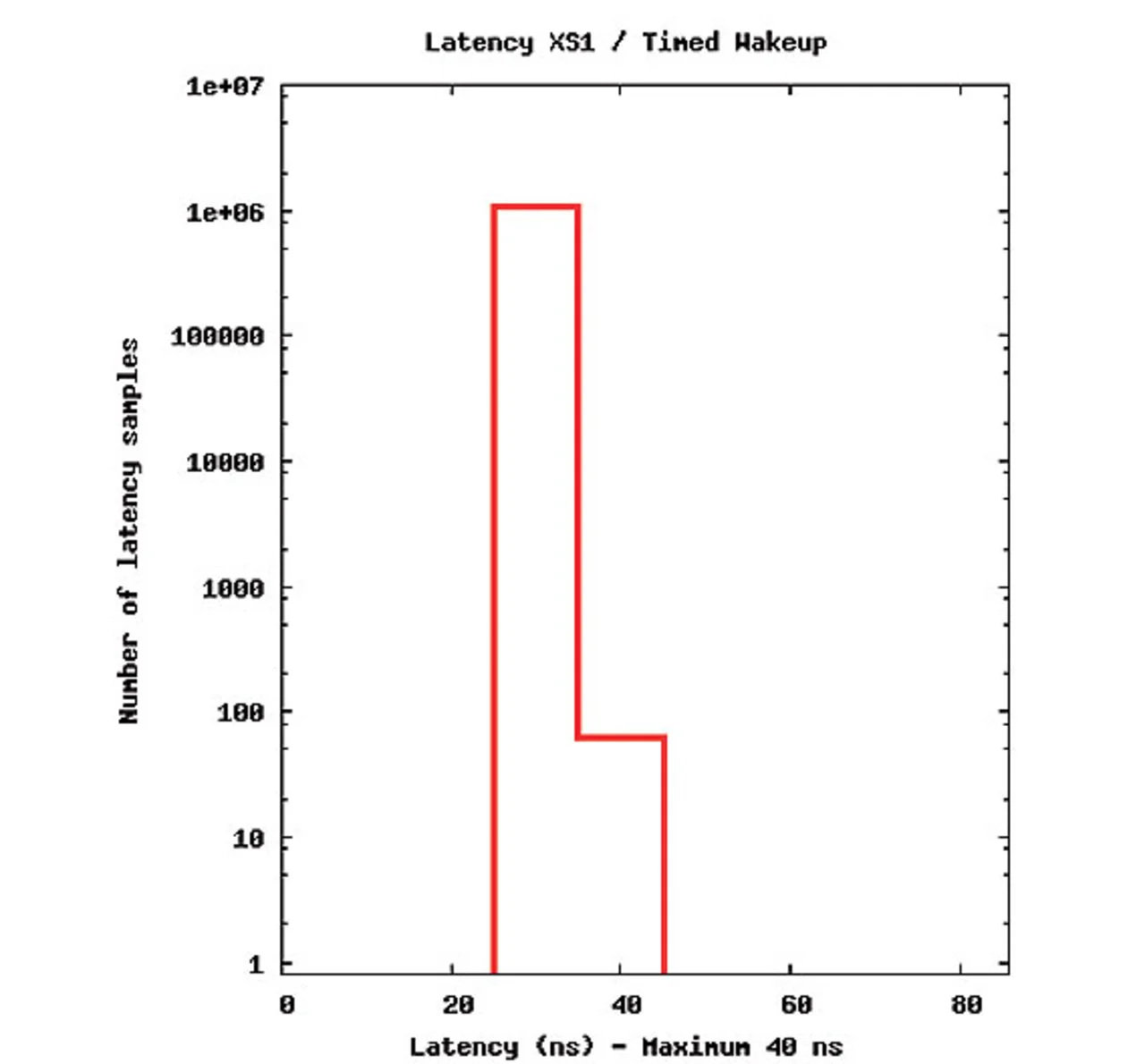

Um das Echtzeitverhalten des XS1 einordnen zu können, werden Tests durchgeführt, deren Ablauf mit den von OSADL durchgeführten Tests (www.osadl.org/Latency-plots.html) vergleichbar ist. Dazu wird auf einem Prozessor XMOS XS1-G4 mit vier Kernen wiederholt ein Prozess von einem Timer geweckt und die vom Prozess dann gemessene Zeit mit der vorgesehenen Weckzeit verglichen. Gemessen werden die Zeiten mit einer Auflösung von 10 Nano-sekunden. Außerdem wird während der Messung zusätzliche Last erzeugt, sowohl auf dem UART als auch seitens Ethernet. Wie berechnet beträgt die maximale Latenz 40 Nanosekunden (Bild 2).

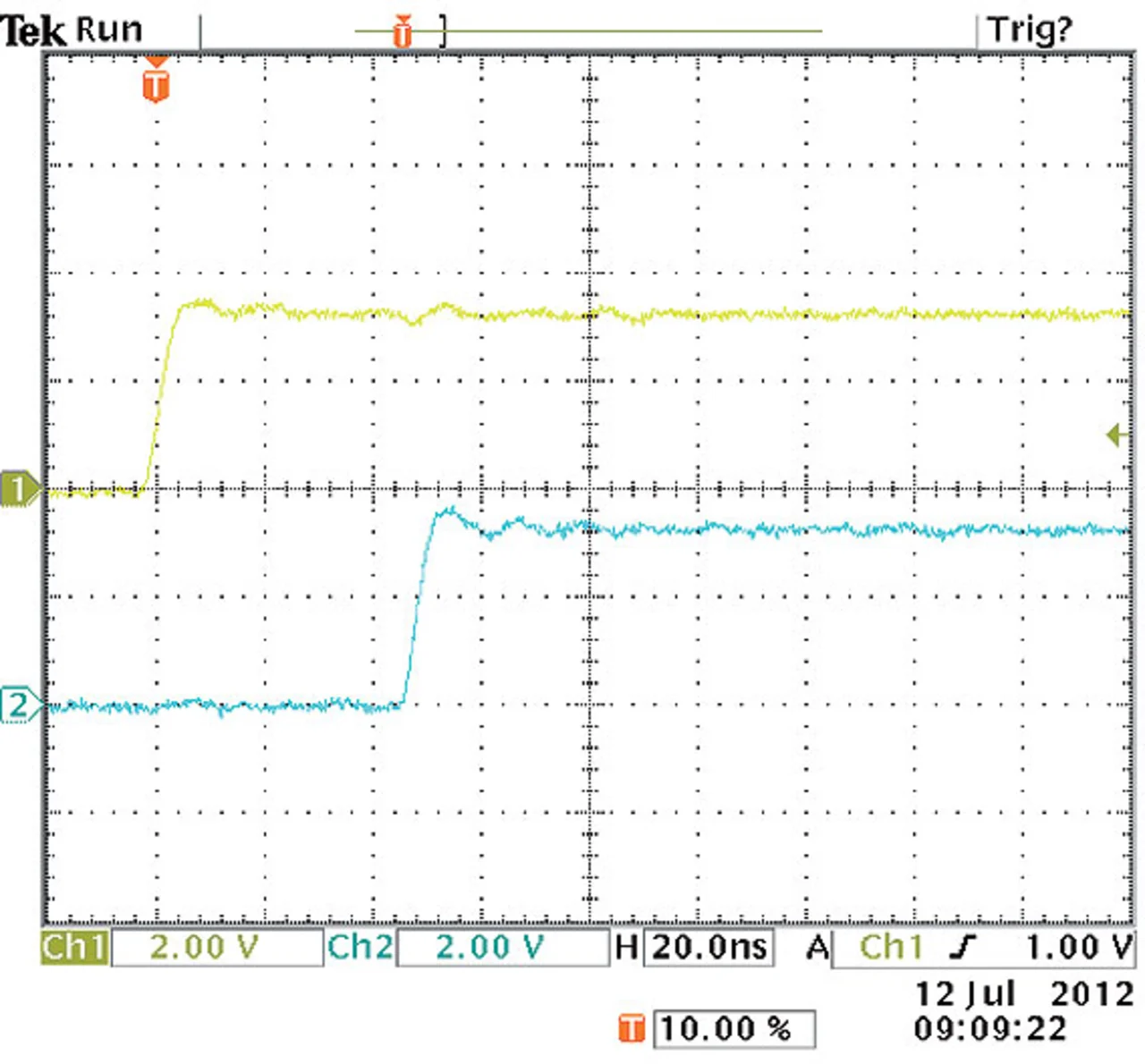

Zum Vergleich wird an derselben Hardware eine zweite Messung durchgeführt, die anstatt auf dem internen Timer auf externen Ereignissen basiert. Der Testprozess schläft, bis er von einer steigenden Flanke am Input Port geweckt wird. Auf dem Output Port wird dann entsprechend der Pegel angepasst. Wie im ersten Fall wird auch hier begleitende Last auf den übrigen Schnittstellen erzeugt. Die gemessene Latenzzeit liegt geringfügig über 40 Nanosekunden, was auf die Signallaufzeiten an den -GPIOs zurückzuführen ist (Bild 3).

Deutlicher Vorsprung bei Echtzeit-Anwendungen

XS1-Prozessoren können in vielen Projekten als direkter Ersatz für FPGAs mit bis zu 20.000 Logikelementen eingesetzt werden und erschließen gleichzeitig Möglichkeiten eines DSPs oder Mi-krocontrollers. Jeder der acht Threads je Kern kann normale Berechnungen, DSP-Code (inkl. 32×32-MAC) und I/O-Befehle steuern, jeweils mit der Möglichkeit, dies mit den internen Timern mit einer Auflösung von 10 Nanosekunden zu synchronisieren. Die Programmierung erfolgt einheitlich in C/C++ und XC (www.xmos.com/published/xmos-vs-fpga-whitepaper).

Im Gegensatz zu einfachen Mikrocontrollern erlaubt der XS1 mit acht -Threads pro Kern die parallele Bearbeitung verschiedener Ereignisse ohne zusätzlichen Aufwand (scheduling). Dadurch ist es möglich, auch komplexe Szenarien einfach zu implementieren, ohne dass zusätzliche Komponenten erforderlich werden. Bezogen auf die reine Rechenleistung ist der XS1 auch direkt mit aktuellen 32-bit-Prozessoren (ARM, x86) vergleichbar: Taktraten ab 400 MHz, ein oder mehrere Kerne, Zugriff auf verschiedene Standardschnittstellen.

In puncto Echtzeit jedoch lassen sich mit dem XS1 deutlich bessere Resultate erzielen: Während die von OSADL mit Realtime-Linux getesteten Systeme durchgängig maximale Latenzen nicht unter 50 Mikrosekunden erreichen (z.B. AMD Athlon 64 bit/1,8 GHz: 80 Mikrosekunden, www.osadl.org/Single-View.111+M516dd7f7d5b.0.html), erhält man mit dem XS1 maximale Latenzen von 40 Nanosekunden: Der Unterschied im Echtzeitverhalten liegt also bei einem Faktor von 1 zu 1.000. Hinzu kommt, dass die Werte beim XS1 direkt aus dem Prozessor-Design abgeleitet und somit garantiert werden können, während es sich bei den auf Linux basierenden Vergleichssystemen um Messwerte handelt.

Für manches Projekt wird allerdings die Tatsache von Nachteil sein, dass der XS1 nicht über einen DRAM-Controller verfügt. Aufgrund der guten Timing-Eigenschaften ist zwar der Anschluss von DRAM dennoch möglich, allerdings dann nicht direkt im Adressraum ver fügbar. Weil dadurch kein Code direkt aus dem DRAM ausgeführt werden kann, ist beispielsweise eine Portierung von Linux auf XS1 nicht machbar. Die für eingebettete Systeme erforderliche Software - verschiedene Treiber, TCP/IP-Stack und beispielweise auch ein Webserver - ist dennoch vorhanden, ebenso wie ein einfaches Betriebssystem mit dynamischer Prozessverwaltung.

- XMOS - der Echtzeit-Prozessor

- Power Management ohne Kunstgriffe

- XC: XMOS-Erweiterungen für C