Safety für Auto, Industrie und Medizin

ARM Cortex-R52 für funktionale Sicherheit

Fortsetzung des Artikels von Teil 1

Drei neue Register für Hypervisor-Modus

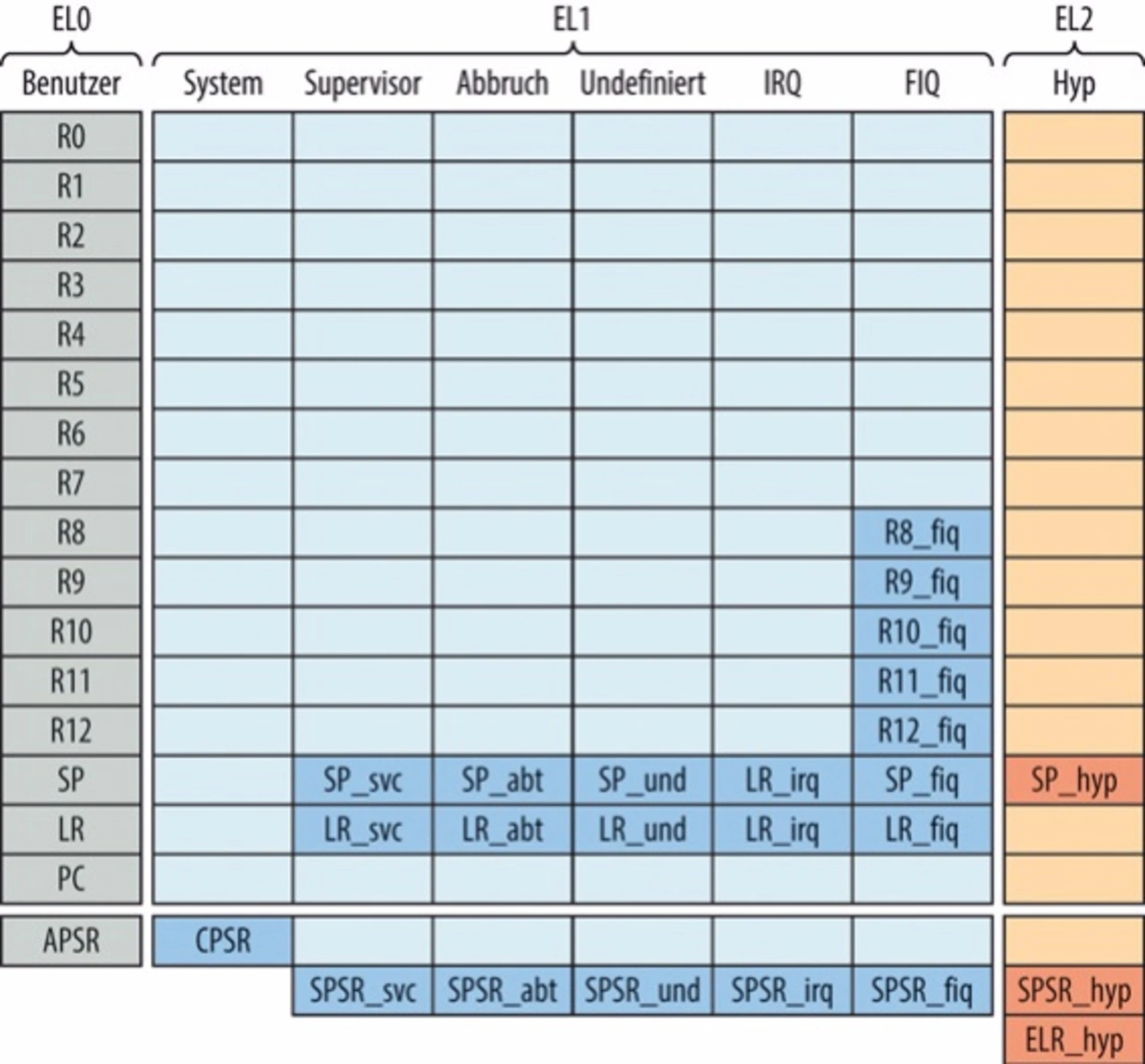

Wenn man sich den Registersatz anschaut (Bild 3), stellt man fest, dass ARM von seiner 64-bit-Architektur ARMv8 »nur« einen der beiden Modi (AARch32 für 32-bit-Kompatibilität und AArch 64 für 64-bit-Instruktionen) übernommen hat, nämlich AARch32. Dies bedeutet, dass alle 13 Allzweck-Register 32 bit breit sind, womit man Kompatibilität zu schon existierender ARMv7-R-Software sicherstellt. Dazu kommen der Stapelzeiger, der Programmzähler und das Link-Register.

Neu sind drei Register für den Hypervisor-Modus, von denen ein sogenanntes ELR-Register (Exeption Link Register) den Eintritt in den Hypervisor-Modus über Interrupts und/oder System-Fehler ermöglicht.

Auch die PMSA (Protected Memory System Architecture) der 8. Version wurde gegenüber der 7. Version, die man bei den bisherigen Cortex-R-MPUs (R5/R7/R8) findet, verbessert. Während letztere mit 8, 12 oder 16 Regionen arbeitet, deren Größe jeweils eine Potenz von 2 sein musste und die auch nur an solchen Adressen beginnen und enden können, kann eine Speicherregion unter ¬PMSAv8 an jeder Adresse beginnen und enden, die ein Vielfaches von 64 Byte darstellt. Um die Kontextwechsel zu beschleunigen, besteht jetzt auch neuerdings direkter Zugriff auf die Konfigurationsregister.

Jobangebote+ passend zum Thema

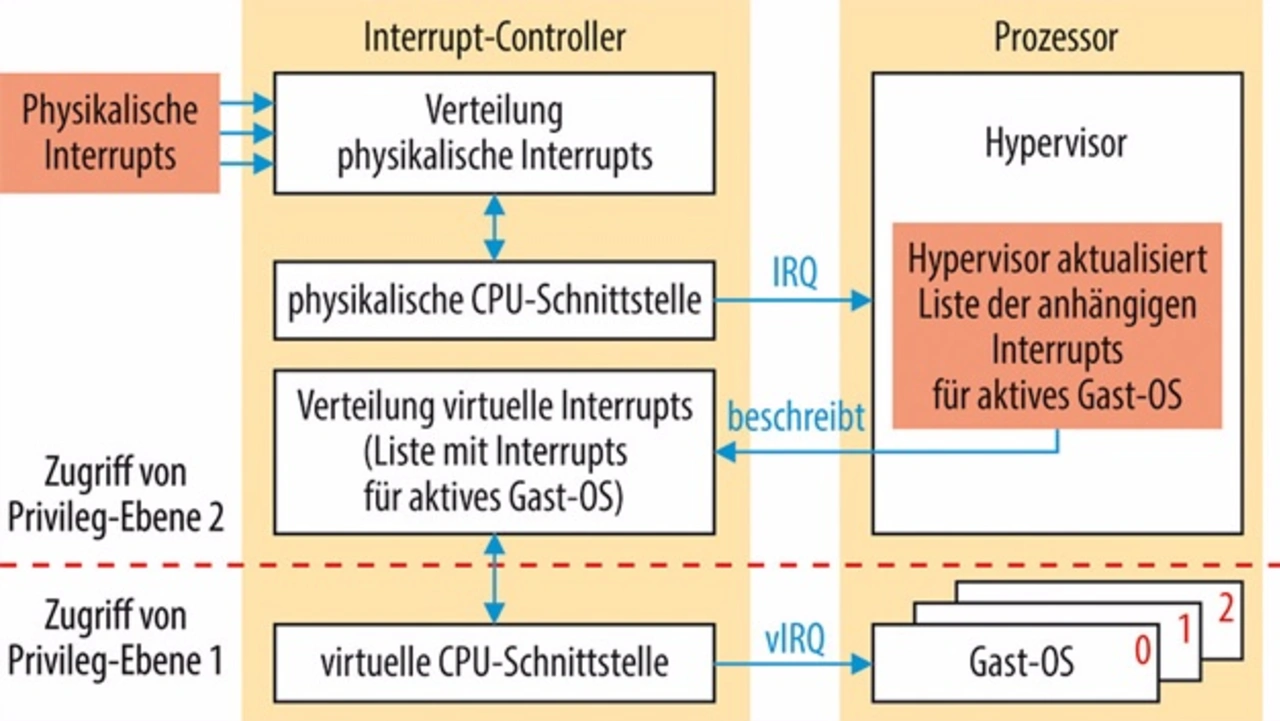

Interessant ist die Interrupt-Verarbeitung (Bild 4): Die Interrpts können, egal wodurch und von wem sie ausgelöst wurden, in den Hypervisor geroutet werden. Dieser führt für jedes Gast-OS eine Liste mit abzuarbeitetenden Interrupts, die dann quasi als virtueller Distributor die Interrupts über eine virtuelle CPU-Schnittstelle den jeweiligen Betriebssystemen zur Abarbeitung zuführen.

Mit den neuen Möglichkeiten stellt sich natürlich auch die Frage, wie diese optimal zu nutzen sind. In mehr und mehr Konsumer-Software wird z. B. auf SIMD-Operationen zurückgegriffen, die Bestandteil von ARMv7/ARMv8-A sind. ARM hat daher primär aus Kompatibilitätsgründen NEON auch in ARMv8-R integriert, d. h. Integer- und Gleitkomma-SIMD-Operationen inclusive doppelte Genauigkeit gemäß IEEE 754. Diese Instruktionen sind auch von einem RTOS nutzbar, was z. B. bei ADAS-Anwendungen wie Radar oder der Ansteuerung von Grafik-Displays und komplexen Algorithmen in der Industrie Nutzen stiftet.

Aus AARch32 wurden weiterhin zwei Instruktionen für die Checksummenberechnung (CRC32/CRC32C) übernommen, dazu gemäß IEEE 754-2008 Minimumberechnung, Maximumberechnung und die Überführung einer Integer-Zahl ins Gleitkommaformat. Nur der Vollständigkeit halber soll nicht verschwiegen werden, dass auch die besonders bei Cortex-M-Mikrocontrollern beliebten Thumb-Instruktionen (16/32 bit für eine möglichst hohe Codedichte) unterstützt werden.

- ARM Cortex-R52 für funktionale Sicherheit

- Drei neue Register für Hypervisor-Modus

- Verbessertes Interrupt-Handling

- Bis zu Quad-Core im Lockstep-Betrieb