MOSFETs auswählen

Was man wissen muss

Fortsetzung des Artikels von Teil 1

Auswahl des Nennstroms

Der zweite Schritt besteht darin, den Nennstrom für den MOSFET zu bestimmen. In Abhängigkeit von der Architektur des Schaltkreises sollte der Nennstrom dem größtmöglichen Strom entsprechen, mit dem die Last unter beliebigen Bedingungen arbeiten kann. Ähnlich wie bei der Spannung muss der Entwickler sicherstellen, dass der MOSFET mit einer entsprechenden Stromstärke zurechtkommt, selbst wenn das System Stromspitzen produziert.

Zwei Fälle sind hier zu unterscheiden: Beim Dauerimpuls befindet sich der MOSFET stabil im Ein-Zustand, sodass kontinuierlich ein Strom durch den Baustein fließt. Ein Spitzenimpuls liegt vor, wenn es durch Zunahme der Stromstärke zu Stromspitzen im Baustein kommt. Liegen diese Bedingungen fest, muss der Entwickler nur noch den Baustein auswählen, der mit der größten auftretenden Stromstärke arbeiten kann.

Jobangebote+ passend zum Thema

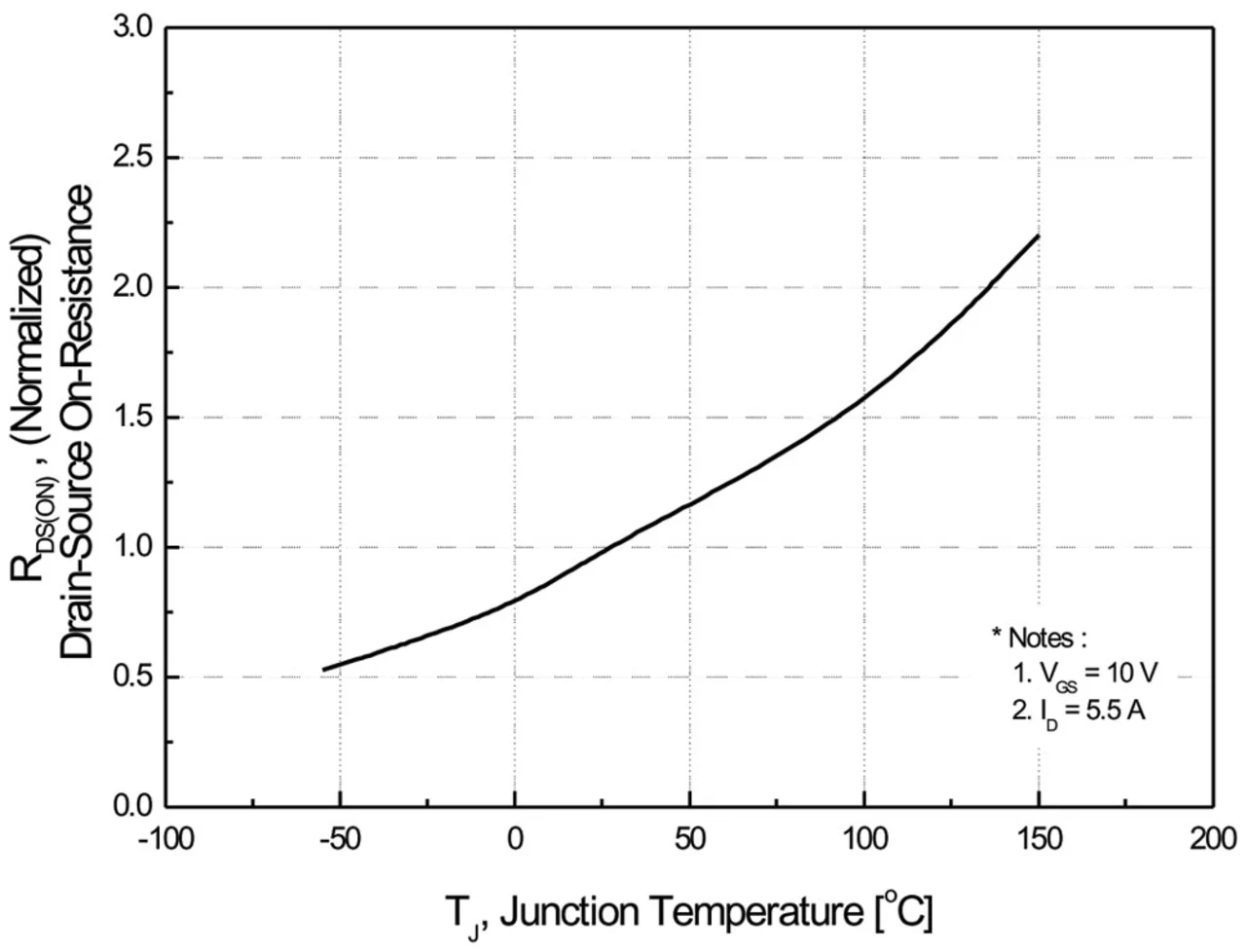

Wenn der Nennstrom ausgewählt ist, müssen die Leitungsverluste berechnet werden. Bei einem MOSFET handelt es sich nicht um einen idealen Baustein, sodass es zu ohmschen Verlusten kommt, sobald Strom den Baustein durchfließt. Verantwortlich dafür ist der Durchlasswiderstand RDS(ON), der zudem noch stark temperaturabhängig ist (Bild 4).

Berechnen lassen sich die Verluste über die Formel ILast 2 · RDS(ON). Erhöht sich die an den MOSFET angelegte Steuerspannung VGS, so verringert sich auch der Durchlasswiderstand. Gleichzeitig führt eine geringere Steuerspannung zu einem erhöhten RDS(ON).

Für Systemdesigner ist dies der Punkt, an dem in Abhängigkeit von der Systemspannung einige Kompromisse eingegangen werden müssen. Für ein tragbares Design ist es einfacher, eine geringere Spannung zu benutzen, während für industrielle Designs höhere Spannungen verfügbar sind. Des Weiteren ist beim RDS(ON) wichtig, dass sich der Wert mit der Stromstärke leicht erhöht. Die tatsächlichen Schwankungen der elektrischen Parameter, die den Widerstand beeinflussen, sind in den Datenblättern des Herstellers enthalten.

Die Prozesstechnik beeinflusst die Kennwerte eines Bausteins in hohem Maße. Bei einigen Prozessen führt der Versuch, die maximale Nennspannung VDS zu erhöhen, zu einer Erhöhung des Durchlasswiderstands. Möchte man bei Einsatz derselben Technik gleichzeitig VDS und RDS(ON) verringern, muss die Die-Größe erhöht werden. Damit steigt auch die Baugröße, die an die vorgegebene Die-Größe und die Entwicklungskosten angepasst wird. In der Branche gibt es zahlreiche Trends, um größeren Chips entgegenzuwirken, beispielsweise die Trench- und die Charge-Balance-Technik.

Bei der Trench-Technik wird ein tiefer Graben (Trench) in den Chip eingebettet, um den Durchlasswiderstand zu verringern. In der Regel ist dieser Baustein aber nur für niedrige Spannungen geeignet. Um den Einfluss von VDSmax auf den RDS(ON) zu minimieren, wurden Epitaxial/ Etched-Pillars in den Entwicklungsprozess eingebunden. Beispielsweise hat Fairchild Semiconductor die »SuperFET«-Technik entwickelt, die zusätzliche Fertigungsschritte umfasst, mit deren Hilfe sich der RDS(ON) reduzieren lässt.

Dieser Fokus auf den RDS(ON) ist wichtig, da sich dieser Wert mit einer Erhöhung der Durchbruchspannung eines Standard-MOSFET exponentiell erhöht und eine Die-Vergrößerung nach sich zieht. Beim SuperFET-Ansatz ist das Verhältnis RDS(ON) zu Chipfläche linear. Hierdurch kann der SuperFET-Baustein einen sehr beachtlichen Wert für den Durchlasswiderstand und eine geringe Die-Größe erreichen – selbst bei einer Durchbruchspannung von 600 V. Dies kann im Ergebnis um bis zu 35% niedrigere Die-Größen bedeuten. Letztendlich kann sich diese Verringerung für den Endverbraucher in einer geringeren Baugröße niederschlagen.

- Was man wissen muss

- Auswahl des Nennstroms

- Thermische Anforderungen und dynamische Kennwerte