Vorteile von Superjunction- und konventionellen Hochvolt-Bauelementen vereint

Coole MOSFETs

Fortsetzung des Artikels von Teil 2

Coole MOSFETs

Zur Unterbindung dieser Oszillationen sind daher bei schnellschaltenden Hochvolt-MOSFETs eine Bedämpfung des Gate-Kreises durch Ferritperlen sowie eine Vermeidung parasitärer Induktivitäten im Source-Kreis und parasitärer Kapazitäten im Gate/Drain-Kreis erforderlich. Alternativ kann die Schaltgeschwindigkeit durch einen erhöhten Gate-Widerstand reduziert werden. Dabei wird ein Teil des Laststroms weiterhin über den halb eingeschalteten Kanal (Miller-Phase) fließen. Die Spannung am Gate stellt sich dabei so ein, dass der über die Rückwirkungskapazität dem Gate zufließende Strom gleich dem über Treiber und Gate-Widerstand abfließenden Strom ist. Auf diese Weise wird die Spannungssteilheit über den Gate-Widerstand geregelt. Die Stromsteilheit wird über die Entladegeschwindigkeit des Gates vom Miller-Plateau bis zur Einsatzspannung über die Übertragungssteilheit des MOSFET kontrolliert. Der durch den Kanal fließende Anteil des Laststroms erzeugt jedoch Schaltverluste mit der über dem Bauelement anliegenden Spannung. Weiterhin ist zu beachten, dass hohe Werte des Gate-Widerstands zu einem faktischen Abkoppeln des Gate-Treibers vom MOSFET führen und damit die Oszillationsneigung abhängig vom Layout und den im System vorhandenen parasitären Elementen sogar noch zunehmen kann.

Jobangebote+ passend zum Thema

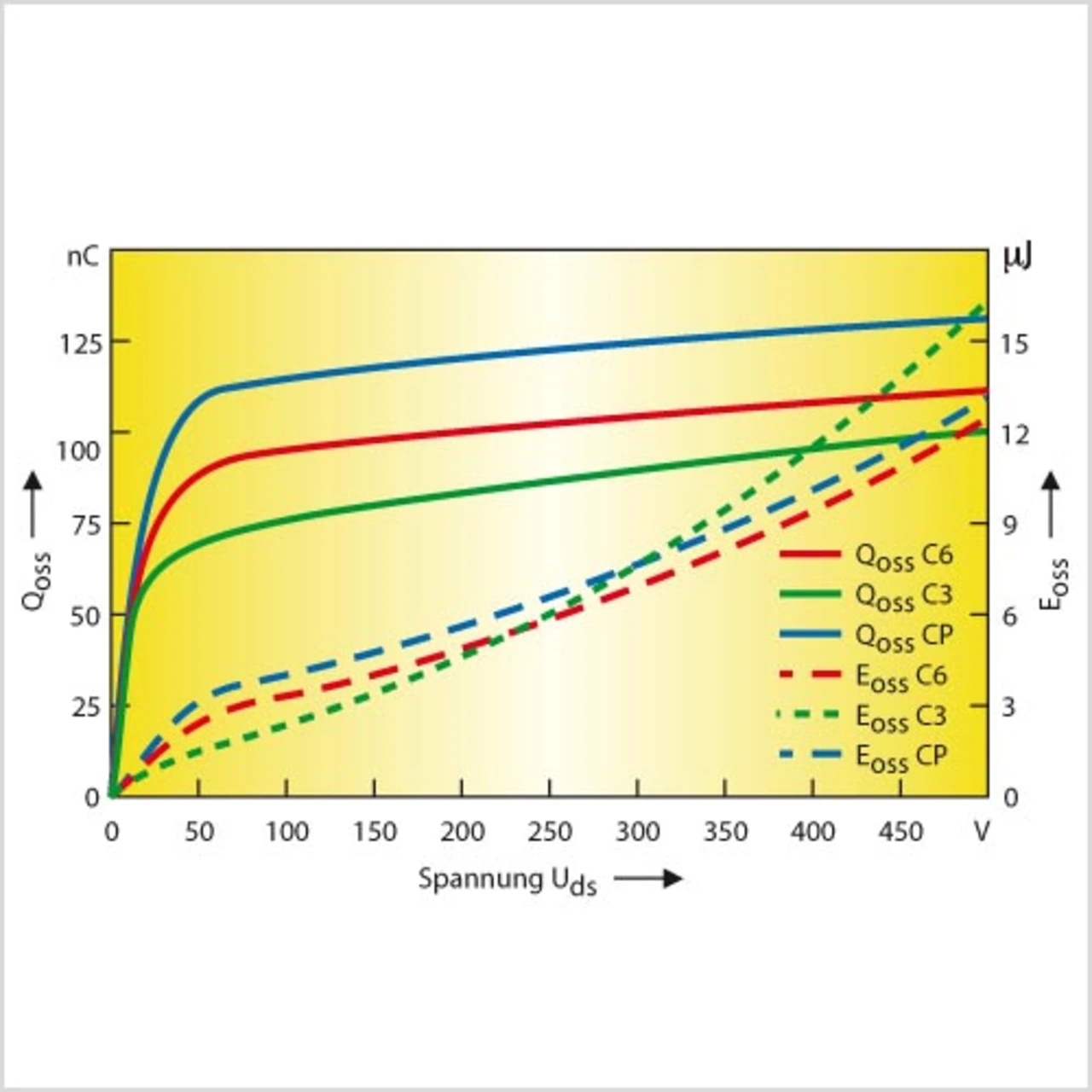

In der neuen Leistungshalbleiterfamilie CoolMOS C6 wird das Zusammenspiel aus Gate-Ladung, Übertragungssteilheit und internem verteiltem Gate-Widerstand so eingestellt, dass es selbst mit 0 Ω Gate-Widerstand zu keinen exzessiven Strom- oder Spannungssteilheiten kommt. Gleichzeitig bietet die Familie die besonders niedrigen flächenspezifischen Einschaltwiderstände der CP-Familie. Wie aus Bild 2 zu erkennen ist, wurde die in der Ausgangskapazität gespeicherte Energie Eoss sogar noch über das mit der CP-Familie erreichte Niveau verbessert. Die Energie Eoss wird beim Ausschalten in der Ausgangskapazität gespeichert und während des Einschaltens in Wärme umgewandelt. Sie trägt daher zu Verlusten bei.

In resonanten Topologien wie dem LLC-Wandler ist neben der Energie Eoss auch die Zeit für die Umladung der Ausgangskapazität wichtig. Diese Zeit kann durch die Ladung Qoss ausgedrückt werden, die sich einerseits aus dem Integral über die Ausgangskapazität und andererseits als Produkt des Umladestroms mit der Umladezeit ergibt. Wie ebenfalls aus Bild 2 ersichtlich, bringt die C6-Familie gegenüber der CP-Familie eine etwa 15%ige Verbesserung und erreicht nahezu das Niveau der C3-Familie.

Insgesamt zeigt die C6-Familie das beste Verhältnis aus geringer Energie Eoss – die entscheidend für die Erreichung des spannungslosen Schaltens bei gegebenem Laststrom und Resonanzelement ist – und vergleichsweise kurzer Umladezeit.

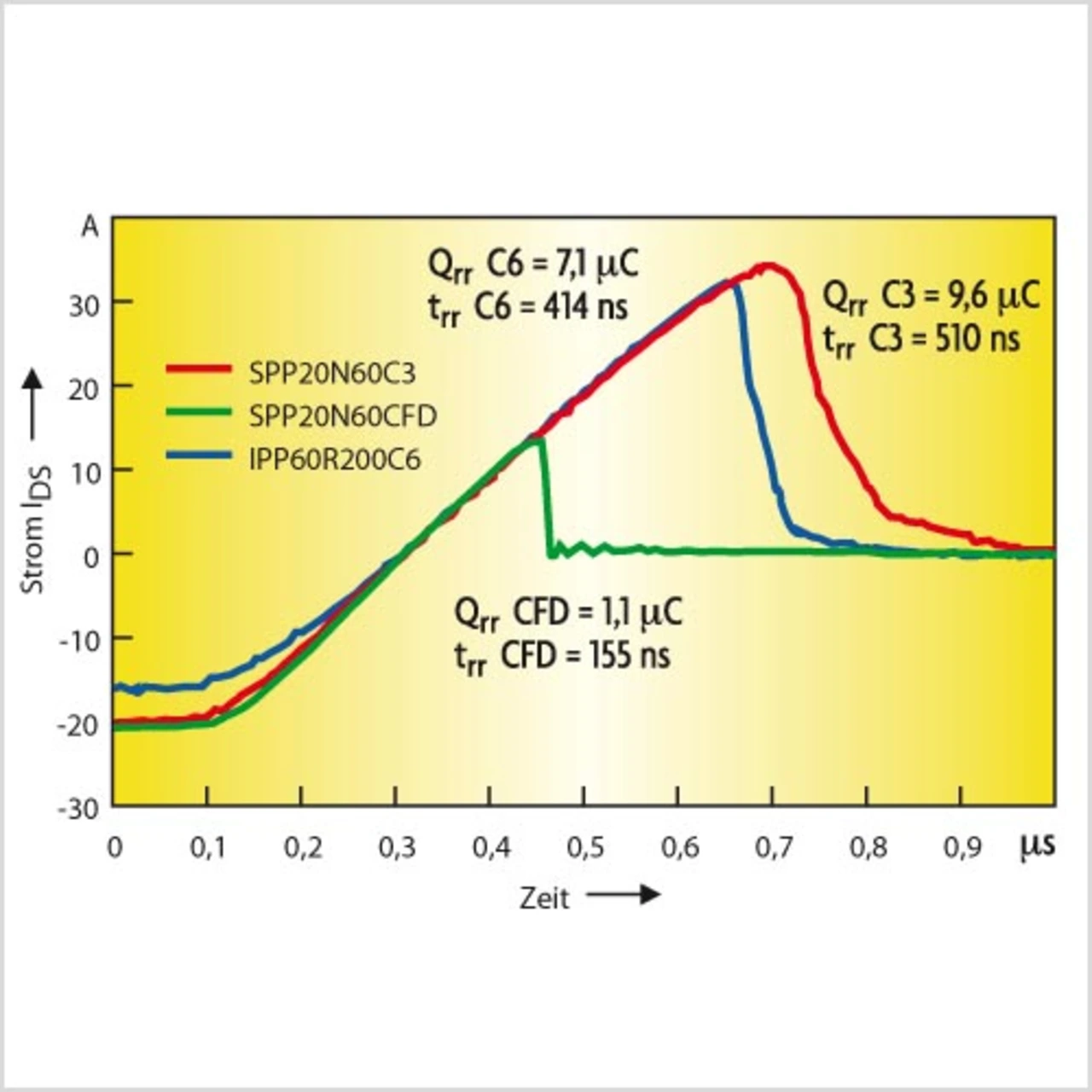

Ein weiteres wichtiges Kriterium für resonante Topologien ist das Überleben von Fehlerfällen wie der harten Kommutierung der leitenden Body-Diode. Solche Fälle können beispielsweise im LLC-Wandler in der Anlaufphase oder bei heftigen Lastsprüngen auftreten. Wie Bild 3 zeigt, ist die Speicherladung der Body-Diode beim CoolMOS C6 gegenüber der C3-Familie um etwa 25 % reduziert.

Das Bauelement zeigte sich in Versuchen bei Kommutierungsvorgängen mit zwei jeweils gleichen Bauelementen als Schalter und Freilaufdiode als außerordentlich robust und erwies sich als praktisch unzerstörbar. Damit kann auf den Einsatz der teureren, da in der Herstellung aufwendigeren Bauteile aus der Fast-Body-Diode-CoolMOS-Familie CFD verzichtet werden.

- Coole MOSFETs

- Bauelementkonzept

- Coole MOSFETs

- Experimentelle Ergebnisse

- Literatur