Vorteile von Superjunction- und konventionellen Hochvolt-Bauelementen vereint

Coole MOSFETs

Fortsetzung des Artikels von Teil 1

Bauelementkonzept

Der grundlegende Durchbruch bei Hochvolt-MOSFETs wurde durch die Einführung des so genannten Kompensations- oder Superjunction-Prinzips erreicht [1, 2]. Wie von Phillips-Forschern bereits in den 70er und 80er Jahren festgestellt wurde, lässt sich die Durchbruchspannung von Lateraltransistoren deutlich erhöhen, wenn man parallel zur stromführenden Schicht eine weitere p-leitende Schicht hinzufügt. Dieses, als Reduced-Surface-Field oder RESURF-Prinzip bekannte Konzept wurde in theoretischen Arbeiten [3] und in Patentanmeldungen [2] auf viele weitere parallele Schichten, das so genannte Multi-RESURF-Konzept, ausgedehnt und auf vertikale Bauelemente übertragen.

Jobangebote+ passend zum Thema

Allein die Herstellung dieser Bauelemente gestaltete sich schwierig und wurde mit der Einführung der Cool-MOS-Familie 1998 erstmals in kommerziellem Maßstab gelöst. Die strukturbestimmende vertikale p-Schicht wird bei der überwiegenden Mehrheit der im Markt vertretenen Bauelemente durch Abscheidung von Mehrfach-Epitaxieschichten und Implantation erzeugt. Vereinzelt und im Labormaßstab werden auch Trench-Ätzverfahren eingesetzt [6, 7].

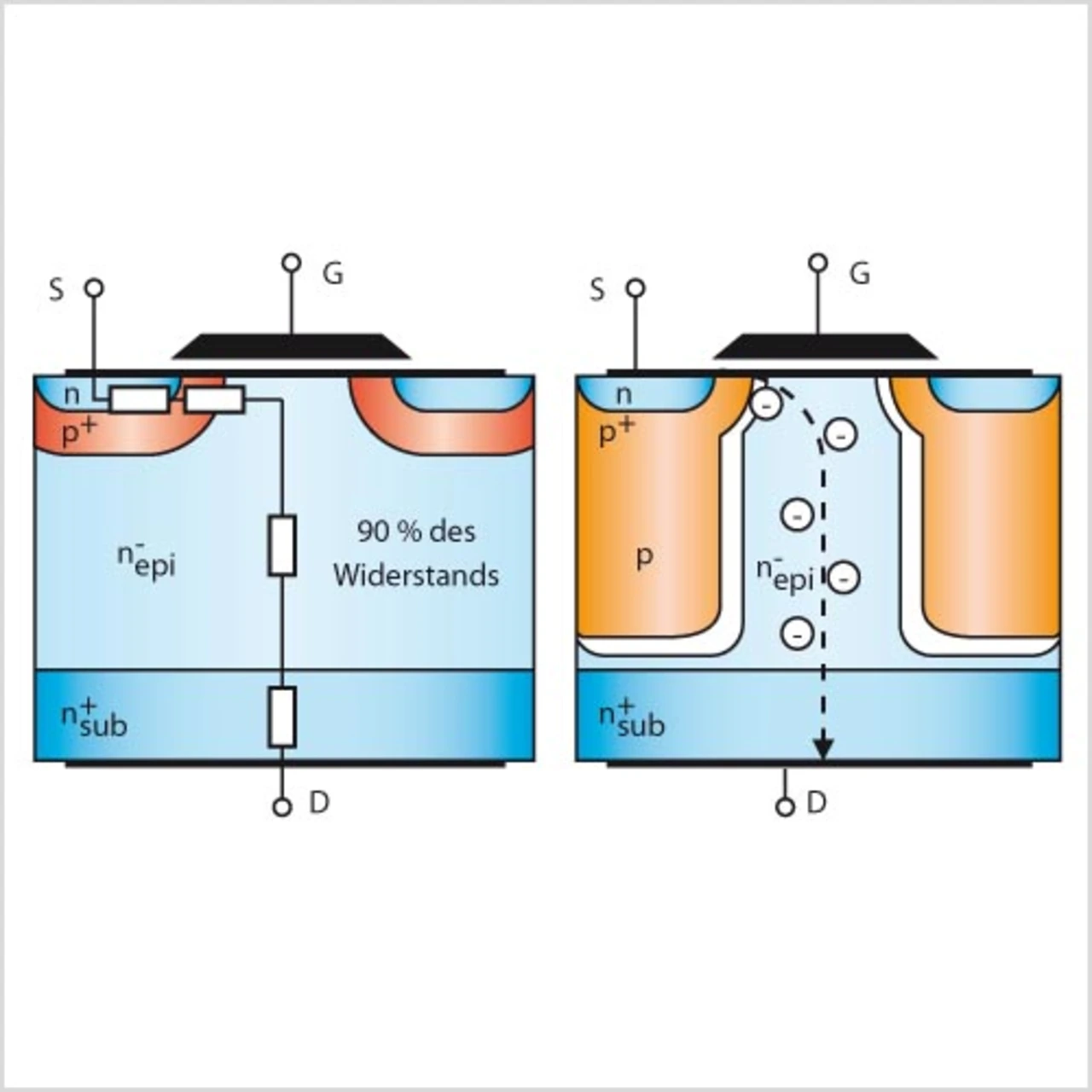

Wie in Bild 1 gezeigt, erlaubt der Einsatz der p-leitenden Zone eine deutlich höhere Dotierung der stromführenden n-leitenden Zone und damit eine dramatische Senkung des flächen-spezifischen Einschaltwiderstands. Im eingeschalteten Zustand profitiert das Bauelement von den hoch leitfähigen n-Gebieten, im Sperrfall kompensieren die in der p-Zone vorhandenen Dotieratome den Überschuss der Donatoren aus dem n-Gebiet. Damit ist eine Überwindung des von Chen und Hu abgeleiteten so genannten Silizium-Limits möglich [4, 5].

Durch die Reduktion des flächenspezifischen Einschaltwiderstands kann sowohl ein niedrigerer RDS on in einer gegebenen Gehäuseform als auch ein gegebener RDS on in einer kleineren Chipfläche hergestellt werden. Während die Verringerung des RDS on kompaktere oder verlustärmere Schaltnetzteillösungen erlaubt, dient die Chip-Verkleinerung einer Verbesserung der Kostenposition im Herstellprozess. Diese Vorteile werden jedoch mit zwei Nachteilen erkauft: einerseits der Reduktion der im Bauelement dissipierbaren Verlustleistung in Betriebszuständen wie Durchbruch, Kurzschluss oder Linearbetrieb und andererseits mit einer inhärent zunehmenden Schaltgeschwindigkeit aufgrund der Reduktion der Bauelementkapazitäten.

Im Ausschaltvorgang (hartes Schalten) bei kleinen Gate-Widerständen kommutiert der Laststrom in die Ausgangskapazität und lädt diese auf die Zwischenkreisspannung auf. Der Spannungsanstieg hängt dabei linear vom Laststrom und umgekehrt proportional vom Wert der Ausgangskapazität ab. Da die Ausgangskapazität bei hoher Spannung den kleinsten Wert annimmt, wird die höchste Spannungssteilheit kurz unterhalb der Zwischenkreisspannung erreicht. Die Stromsteilheit wird nur durch die Induktivität im Source-Kreis limitiert. Mit dieser Art des Abschaltens wird der maximale Wirkungsgrad erzielt, da die auftretenden Verluste im Idealfall bis auf die in der Ausgangskapazität gespeicherte Energie reduziert werden können. Jedoch treten bei Betriebsfällen mit Überstrom wie bei eingangsseitigem Spannungseinbruch oder sekundärseitigem Kurzschluss sehr hohe Strom- und Spannungssteilheiten auf, die zu unerwünschten Oszillationen im Source- oder Gate-Kreis bis hin zur Zerstörung des Leistungshalbleiters führen können.

- Coole MOSFETs

- Bauelementkonzept

- Coole MOSFETs

- Experimentelle Ergebnisse

- Literatur