Stromverteilung auf Systems-on-Chips

Der rechte Strom am rechten Ort

Fortsetzung des Artikels von Teil 2

Den Widerstand auskundschaften

Für die Stromnetzverifikation gibt es bereits verschiedene beweisbare Assertionen. Auch hier wird die formale Netzverifikation die dynamische Analyse von Spannungseinbrüchen nicht vollständig verdrängen. Der große Vorteil ist jedoch, dass diese Methode nicht von Testvektoren abhängt und es somit keine »übersehenen « Extremfälle gibt.

Netzanalyse in den gesamten Stromversorgungs-Designflow passt. Die meisten Fehler lassen sich frühzeitig erkennen, schon vor der statischen Analyse. Dies hängt ebenfalls mit der vektorunabhängigen Natur der Analyse zusammen. Das Power-Designteam muss nicht auf Simulationsergebnisse oder Timinginformationen von den Front-End-Leuten warten.

Mit der Zeit wird es immer mehr beweisbare Power-Grid-Assertionen geben. Ein Beispiel für eine solche Assertion ist die Begrenzung des Wirkwiderstands an beliebiger Stelle in der Schaltung.

Der Widerstand des Rückpfades zur Stromquelle an einer Stelle innerhalb des Stromverteilungsnetzes lässt sich bei kleinen Schaltungen einfach bestimmen. Das ist elektrotechnisches Grundwissen: Seriell und parallel geschaltete Widerstände werden als ein einzelner Ersatzwiderstand behandelt. In den höheren Studiensemestern wendet man dann Matrizenrechnung an, um den Ersatzwiderstand vernetzter Schaltkreise mit Millionen von Transistoren zu berechnen.

Jobangebote+ passend zum Thema

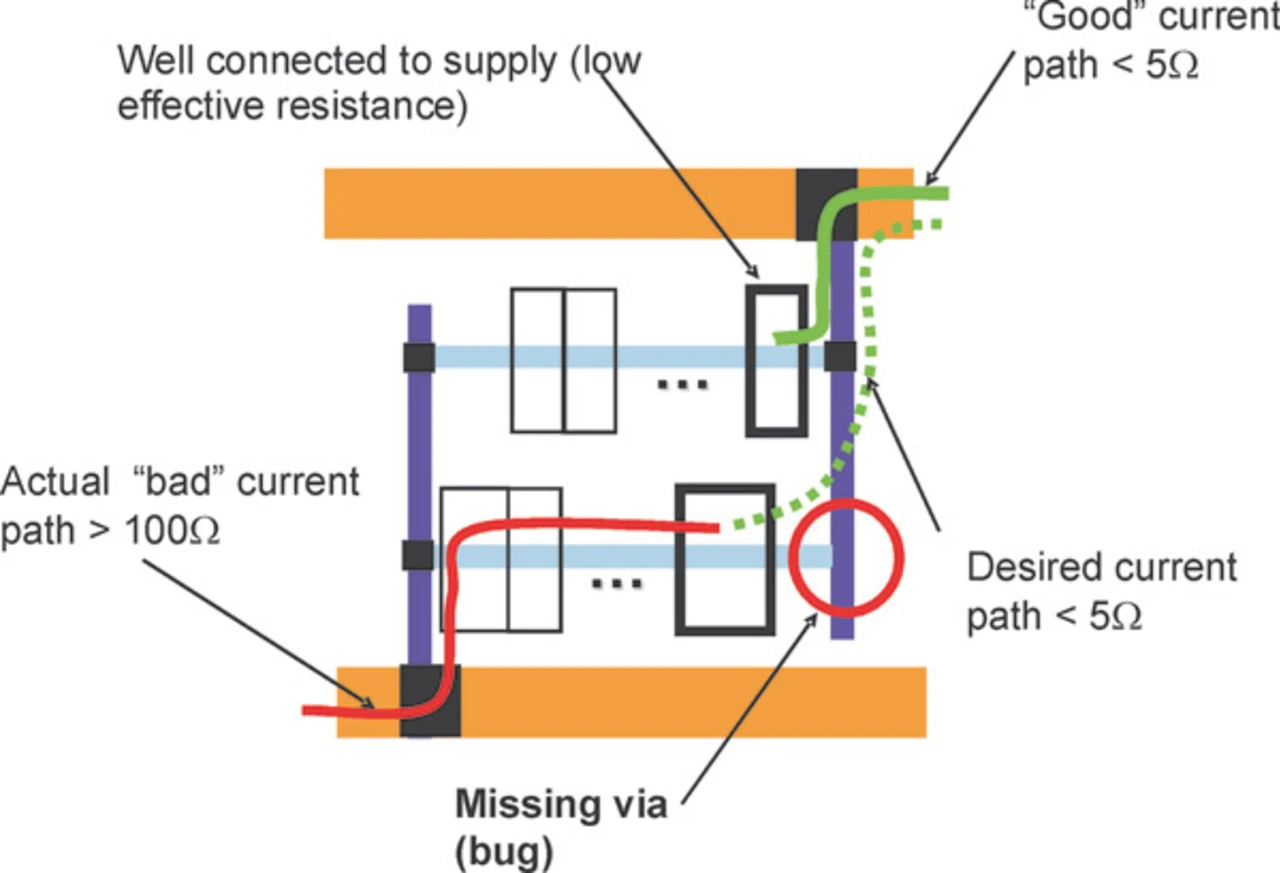

Alternativ lässt sich dieser Widerstandswert auch mit den üblichen statischen Tools zur Spannungsanalyse bestimmen. Der Anwender definiert lediglich einen Ersatzstromkreis in dem ihn interessierenden Bereich und erhält den maximalen Spannungsabfall sowie dessen Abnahme bis hin zu den Versorgungsanschlüssen, wo kein Spannungsabfall vorhanden ist. Mit dem maximalen Spannungsabfall berechnet sich der Ersatzwiderstand aus einer einzigen Multiplikation. Natürlich ist es kaum realistisch, jeden Bereich eines Designs einer vollen statischen Analyse zu unterziehen, der Aufwand an Rechenzeit wäre immens. Oft ist es offensichtlich, woher ein hoher Wirkwiderstand kommt. In anderen Fällen ist einige Detektivarbeit erforderlich. Die formale Verifikation liefert zu jeder Assertionsverletzung Informationen, auf deren Basis der Entwickler das Problem näher eingrenzen kann. Bild 2 zeigt ein solches »Traceback«.

Teil eines Ganzen

Sind nun herkömmliche statische und dynamische Analysetools eigentlich noch nötig? Vielleicht können formale Methoden die statische Analyse ablösen, doch lösen formale Stromnetzverfahren nur einen Teil der Probleme.

Generell rührt starker Spannungsabfall entweder von hohen Widerstandswerten her oder von starkem Strom. Die Methode der Ersatzwiderstände findet zwar alle widerstandsbezogenen Fehler, doch in puncto Strom ist sie nutzlos. Ein Stromnetz kann vollkommen korrekt entworfen worden sein, doch ein durch das gleichzeitige Schalten mehrerer Zellen ausgelöster Stromstoß kann zu einem Spannungsabfall führen. Solche Schwierigkeiten findet auch die statische Analyse nicht.

Dafür eignen sich jedoch automatisierte Optimierungstools, die auf Spannungsabfall spezialisiert sind. Diese Entwicklungswerkzeuge finden »Hot-Spots« und ersetzen sie automatisch durch optimierte Ersatzzellen. Solche Stromspitzen lassen sich jedoch meist nur mit Testvektoren entdecken. Ganz ohne Simualationsvektoren oder die so genannte »vektorlose« Vektorerzeugung geht es also noch lange nicht.

Sequence Design

Telefon 00 44/13 44 62 49 70

www.sequencedesign.com

Autor

Ersin Beyret ist Director of Solutions Engineering bei Sequence Design

Marcel Consèe, DESIGN&ELEKTRONIK

- Der rechte Strom am rechten Ort

- Was heißt hier »statisch«?

- Den Widerstand auskundschaften