Stromverteilung auf Systems-on-Chips

Der rechte Strom am rechten Ort

Fortsetzung des Artikels von Teil 1

Was heißt hier »statisch«?

Der Begriff »statisch« hat in verschiedenen Disziplinen der Elektronik unterschiedliche Bedeutungen. Geht es um Spannungsabfälle, so bedeutet »statisch«, dass die Stromquellen zeitlich gemittelt werden und die Kapazitäten und Induktivitäten keine Berücksichtigung finden. »Dynamische« Analyse des Spannungseinbruchs ist eine Untersuchung über die Zeit unter Einbeziehung der Effekte von Kapazitäten und Induktivitäten. In beiden Fällen wird der Schaltkreis mit spezifischen Stimuli traktiert. Verschiedene Stimuli liefern unterschiedliche Aktivitäten, also andere Ströme und somit andere Spannungseinbrüche.

Geht es hingegen um das Timing, so werden bei der statischen Analyse alle möglichen Signalpfade ohne Stimulus propagiert, um so die größste Verzögerung zu finden. Die dynamische Timinganalyse dreht sich um eine Simulation mit speziellen Vektoren, die echte Verzögerungswerte aus einer SDF-Datei nutzt. Der Designer beobachtet dann, ob der Output stimmt.

Das bedeutet, dass sowohl die statische als auch die dynamische Spannungseinbruchsanalyse der dynamischen Timinganalyse entsprechen. Alle drei nutzen einen spezifischen Satz Vektoren. Der schlimmstmögliche Fall wäre, dass in einem Grenzfall die Timing- oder Spannungs-Randbedingungen nicht erfüllt sind und die Simulationsvektoren diesen Grenzfall nicht abdecken.

Jobangebote+ passend zum Thema

»Vektorlose« oder formale Netzverifikation?

Im Timingbereich sind vektorabhängige Methoden so gut wie obsolet. Für die Spannungsanalyse bewerben zwar viele Hersteller »vektorlose Verfahren«, doch findet im Stillen dennoch eine Simulation statt. Vektorlose Methoden erzeugen zwar eine Art Testvektor, doch weiß der Anwender nicht, ob dieser tatsächlich auch den schlechtesten Fall berücksichtigt. Damit gibt es zwangsläufig sowohl falschnegative Ergebnisse als auch übersehene positive.

Manche vektorlose Algorithmen erzeugen Stimuli, die nicht erreichbar sind. So kann ein solcher Algorithmus ein sehr aktives Registermuster finden, einen Fehlerzustand einer Zustandsmaschine. Ereignet sich nun während dieses Zustands ein Spannungseinbruch, so ist das Ergebnis falsch-positiv, da der Zustand in Wirklichkeit nicht vorkommen kann. Dementsprechend wagt es kein Toolanbieter zu behaupten, dass der erzeugte Testvektorensatz echte lokale Worst-Cases finde. Möglicherweise wird es irgendwann ein perfektes vektorloses Verfahren geben, das den wirklichen schlimmstmöglichen erreichbaren Zustand findet. Immerhin muss ein solcher Vektor existieren, es geht lediglich darum, ihn auch zu finden. Heutige Designteams haben jedoch keine Zeit, um auf diesen Stein der Weisen zu warten.

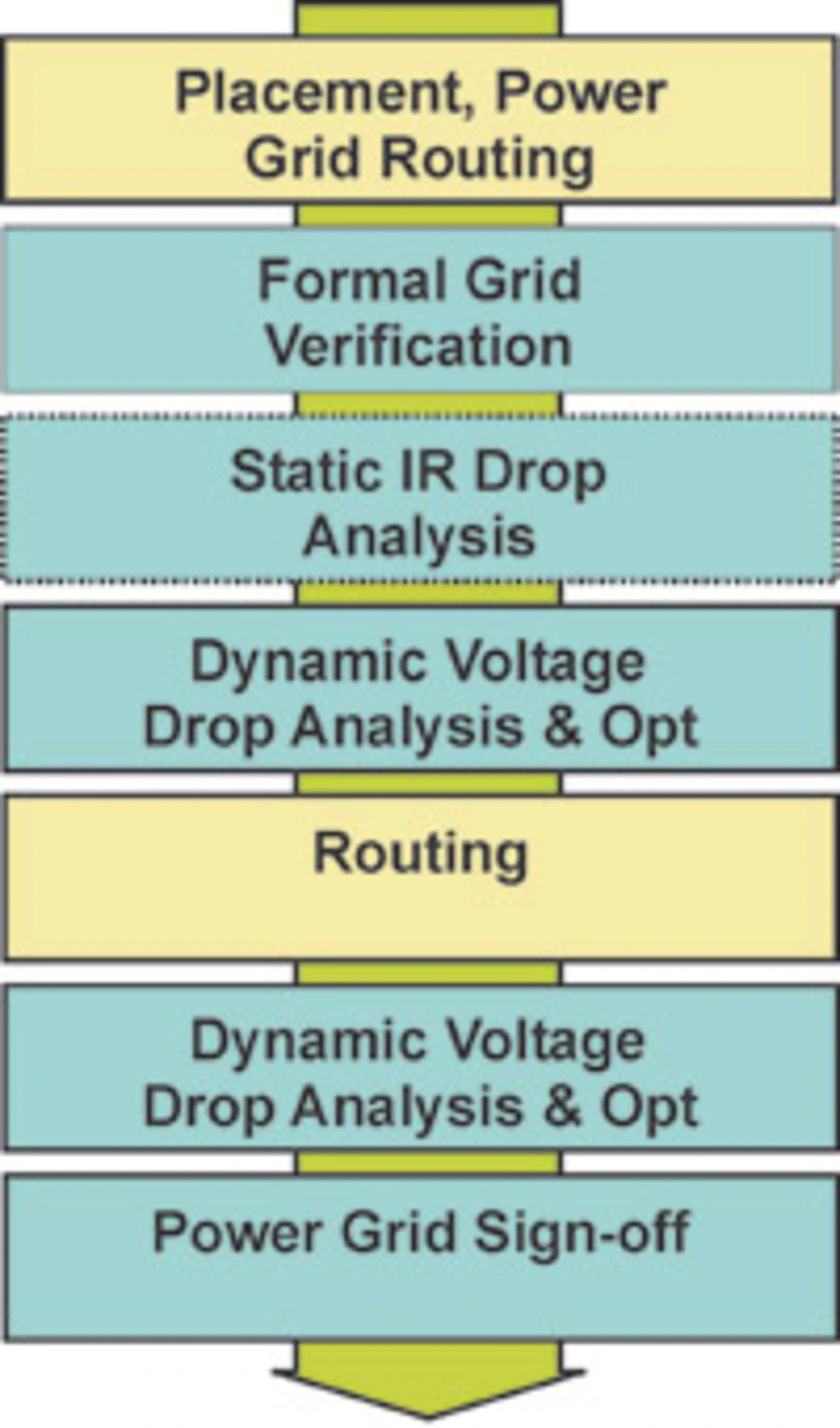

Die formale Verifikation liefert eine gute Grundlage für einen anderen Ansatz. Generell lösen in der funktionalen Verifikation formale Methoden die herkömmlichen simulationsbasierten Verfahren ab. Anstatt händisch erzeugte oder ATPG-basierte (Automated Test Pattern Generation, Automatische Erzeugung von Testmustern) Testvektoren einzusetzen, überprüft dabei ein Entwicklungstool Assertionen. Ein solches Tool kann etwa nachweisen, ob eine monostabile Zustandsmaschine wirklich monostabil ist, oder ob ein anderer Prozess vielleicht ein Schnittstellenprotokoll sperrt. Falls die Assertion widerlegt wird, verfolgt das Tool die Prozedur zurück, sodass der Anwender erkennt, warum die Assertion verletzt wurde. Natürlich ist es nicht möglich, einen wirklich vollständigen Satz von Assertionen aufzustellen, sodass die Simulation komplett überflüssig würde, doch wächst die Anzahl beweisbarer funktionaler Assertionen ständig.

- Der rechte Strom am rechten Ort

- Was heißt hier »statisch«?

- Den Widerstand auskundschaften