Ein Überblick über die Optionsvielfalt bei SRAMs

Der SRAM-Report 2004

Fortsetzung des Artikels von Teil 3

Synchrone SRAMs in der Standard-Ausführung

Diese so genannten „Standard Synchronous SRAMs“ waren die ersten synchronen SRAMs, die in Main-stream-Anwendungen Einsatz fanden. Sie waren hauptsächlich für L2-Cache-Applikationen in PCs konzipiert, kamen jedoch auch außerhalb des PC-Segments zum Einsatz, z.B. in Netzwerk- und Telekommunikations-Ausrüs-tungen, im DSP-Bereich (digitale Signalverarbeitung), in der Medizintechnik und in Prüfsystemen.

Die interne Architektur der Standard Synchronous SRAMs war so angelegt, dass zwischen Schreib- und Lesezugriffen ein „toter“ Zyklus bzw. ein „Wait State“ eingefügt werden musste. In dieser Phase werden die I/O-Signale des SRAM von Eingang auf Ausgang umgeschaltet. Derartige Zustandswechsel können zu Konkurrenzbetrieb auf dem Bus führen, wenn beide Bauelemente den Bus gleichzeitig ansteuern. Mit einem Wait State lässt sich dieses Risiko vermeiden.

Jobangebote+ passend zum Thema

Da Standard Synchronous SRAMs vorwiegend für den Einsatz als L2-Cache ausgelegt waren, in denen die SRAM-Zugriffe meist aus längeren Bursts bestehen, wirkt sich der zusätzliche Wait State nicht nennenswert auf die System-Leistung aus.

Standard Synchronous SRAMs sind auch für den Betrieb mit zwei Busmastern konzipiert. In Level-2-Cache-Anwendungen kann es sich bei diesen zwei Busmastern um den eigentlichen Prozessor und den Speicher-Controller des zugehörigen Chipsatzes handeln. Um zwei Master zu unterstützen, sieht die Architektur zwei verschiedene Steuereingänge vor, mit denen sich Lese- oder Schreibzugriffe auslösen lassen. ADSP# (Address Strobe Processor) wird in der Regel vom Prozessor zum Steuern des Speichers benutzt, während ADSC# (Address Strobe Controller) meist vom Controller verwendet wird. Zugriffe auf den Speicher sind nur möglich, wenn ADSC#, ADSP# oder beide freigegeben sind.

Standard Synchronous SRAMs unterstützen des Weiteren eine „Burst“-Funktion, die dem Controller mit nur einer einzigen Adresse den Lese- oder Schreibzugriff auf bis zu vier aufeinanderfolgende Speicherstellen im SRAM ermöglicht. Das SRAM verwendet die Erst-Adresse in Verbindung mit einem eingebauten 2-bit-Zähler, der für die Inkrementierung auf die drei folgenden Adressen sorgt. Der Anwender muss lediglich das Eingangssignal ADV# (Advance) des SRAM-Bausteins setzen, um das Weiterzählen auf die folgenden Adressen zu veranlassen. Dieses Merkmal ist speziell in Anwendungen sinnvoll, in denen mehrere Datenworte in einer vorgegebenen Sequenz abgespeichert sind (z.B. bei einer „Cache Line Fill“-Operation).

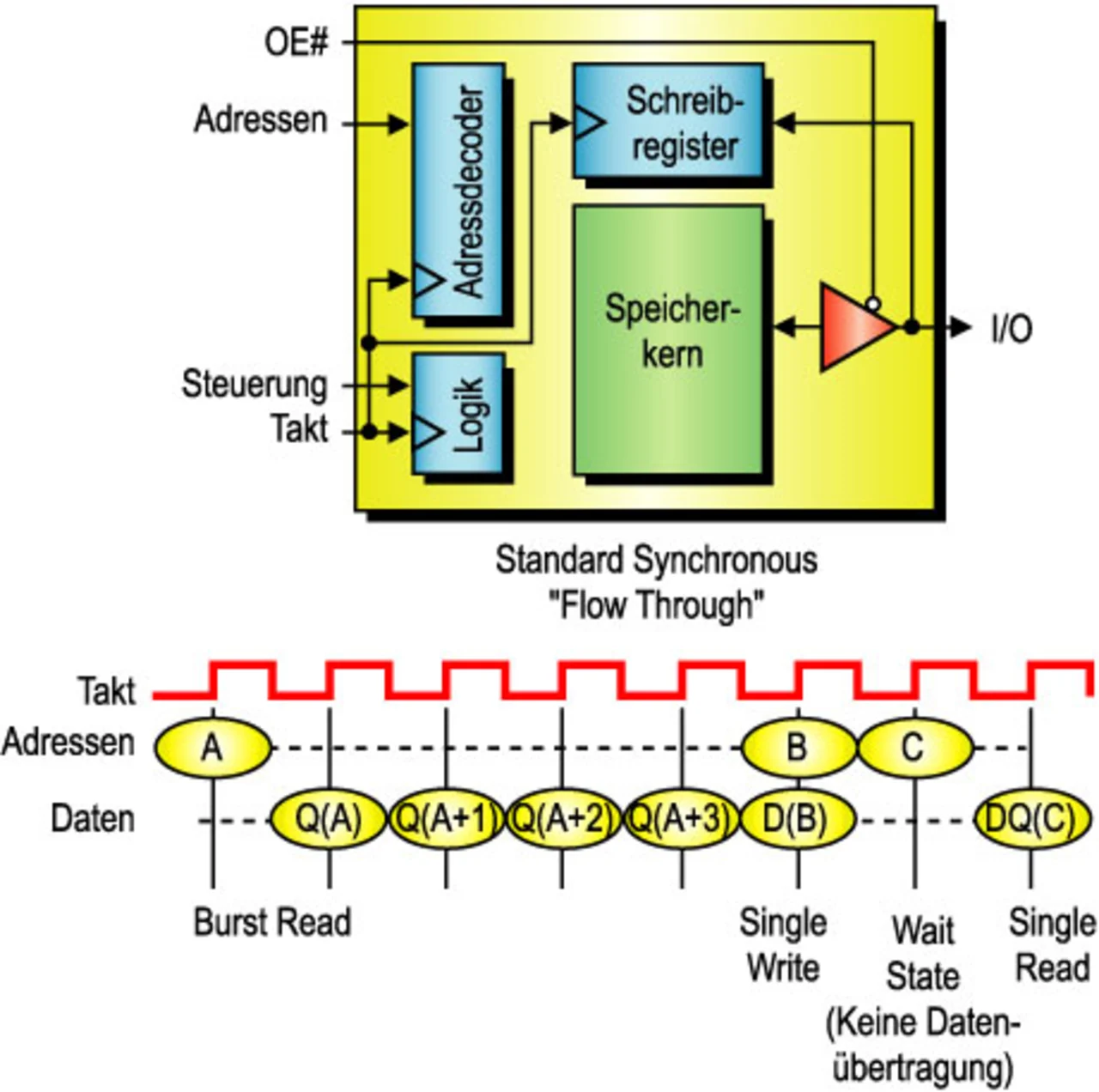

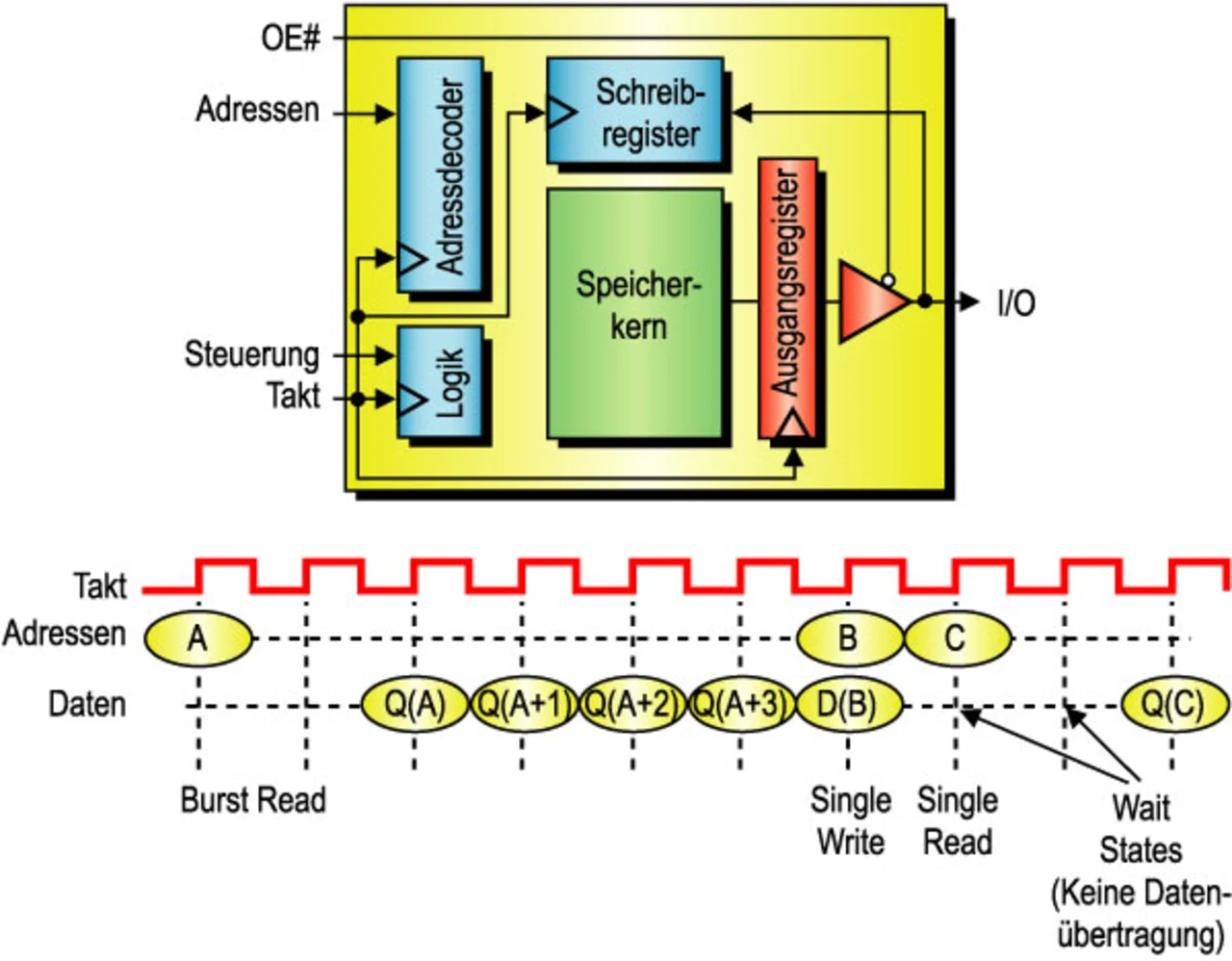

Standard Synchronous SRAMs: „Pipelined“ oder „Flow-Through“

Standard Synchronous SRAMs werden in zwei Haupt-Varianten angeboten: „Pipelined“ und „Flow-Through“.

Sämtliche synchronen SRAMs besitzen Eingangsregister, die zur Erfassung der synchronen Eingangssignale des Bausteins (Address, Data und Control) dienen. Bei Flow-Through-SRAMs sind nur die Eingänge mit Registern versehen. Sind die Address- und Steuer-Eingänge erfasst und wird ein Lesezugriff initiiert, so können die entsprechenden Daten direkt an die Ausgänge gelangen. Die Flow-Through-Architektur (Bild 2) wird bevorzugt, wenn die Anfangs-Latenzzeit (Time to First Data) wichtiger ist als die Langzeit-Bandbreite (Mbit/s).

Ein synchrones SRAM lässt sich auch mit einem Ausgangsregister ausstatten, was damit insgesamt eine zweistufige Pipeline-Struktur ergibt (Bild 3). Ein SRAM mit Eingangs- und Ausgangs-Registern wird deshalb als „Pipelined Synchronous SRAM“ bezeichnet.

Während das Hinzufügen des Ausgangsregisters die Anfangs-Latenzzeit eines Lesezugriffs um einen Zyklus erhöht, verringert sich gleichzeitig der Umfang der Aktivitäten, die verglichen mit einem Flow-Through-SRAM während eines jeden Taktzyklus ausgeführt werden müssen. Man bevorzugt deshalb Pipelined SRAMs gegenüber Flow-Through-SRAMs überall dort, wo die Bandbreite einen höheren Stellenwert hat als die Anfangs-Latenzzeit.

Sämtliche Standard Synchronous SRAMs, ob Pipelined oder Flow-Through, unterstützen bezüglich der Schreibzugriffe mehrere Optionen, nämlich Single-Cycle Writes, Two-Cycle Writes, Burst Writes und Byte Writes. Bei Single-Cycle Writes werden dem SRAM sämtliche erforderlichen Informationen (Address, Data und Control) in einem einzigen Taktzyklus zur Verfügung gestellt. Anders ist es bei Two-Cycle Writes: Hier werden im ersten Zyklus Adressen und Daten, in einem zweiten Zyklus dagegen die Steuer-Information zur Verfügung gestellt. Bei Burst Writes werden die Schreibzugriffe ähnlich wie im weiter oben beschriebenen Burst Read in einer Burst-Sequenz ausgeführt. Bei der Byte-Write-Option schließlich werden von den Byte-Write-Eingangssignalen ausschließlich bestimmte Daten-Bytes geschrieben und kontrolliert.

NoBL SRAMs (No Bus Latency)

Netzwerk-Applikationen unterscheiden sich grundlegend von einem Level-2-Cache. SRAMs können hier in verschiedenen Funktionen eingesetzt werden, so zum Beispiel als Pufferspeicher, Statistik-Puffer usw. Diese Aufgaben bringen meist keine längeren Abfolgen von Lese- oder Schreibzugriffen mit sich. Der weiter oben erwähnte Wait State, der sich auf die System-Performance eines Personal Computers kaum auswirkte, kann deshalb in Netzwerk-Anwendungen deutliche Leistungseinbußen mit sich bringen.

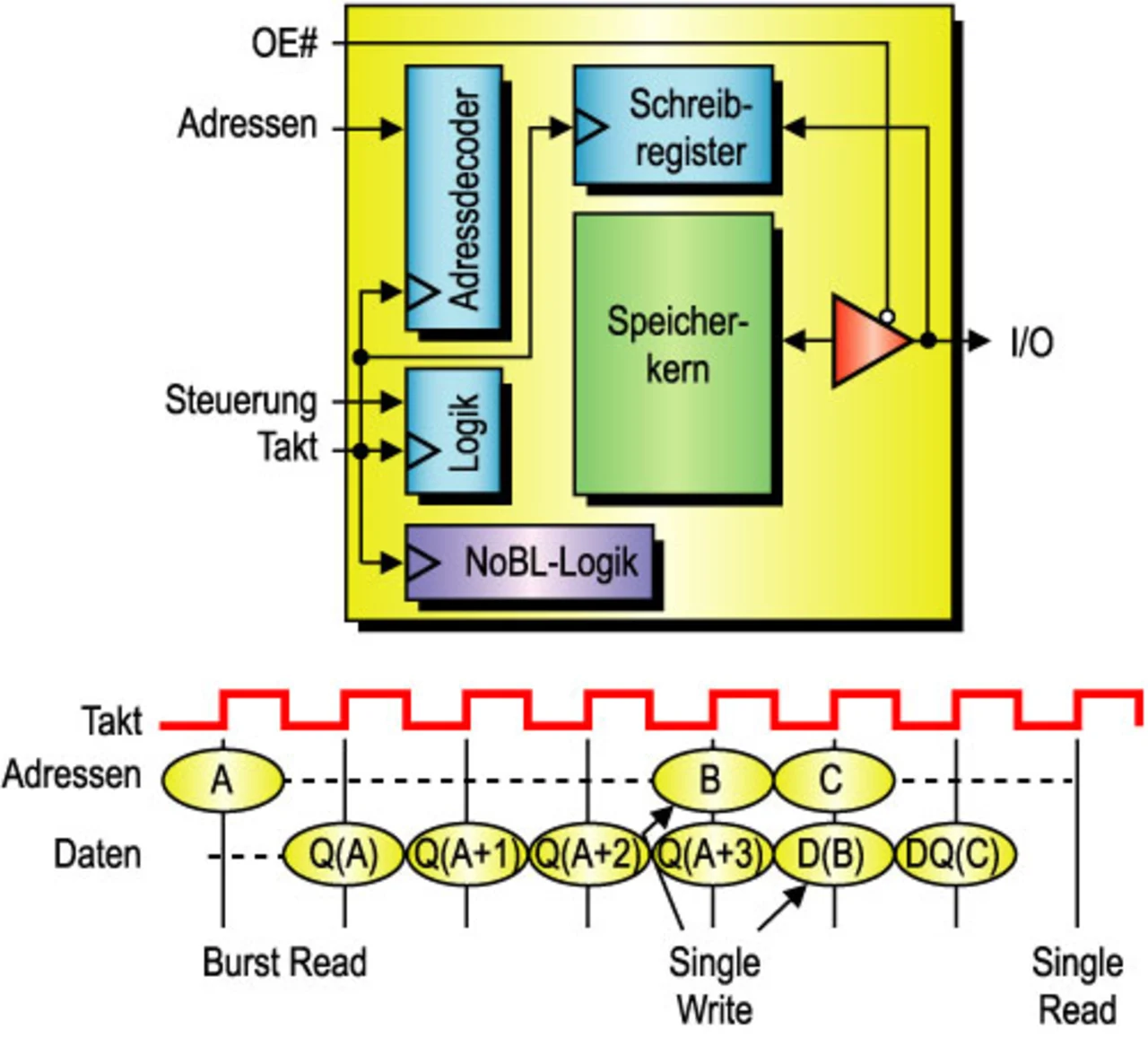

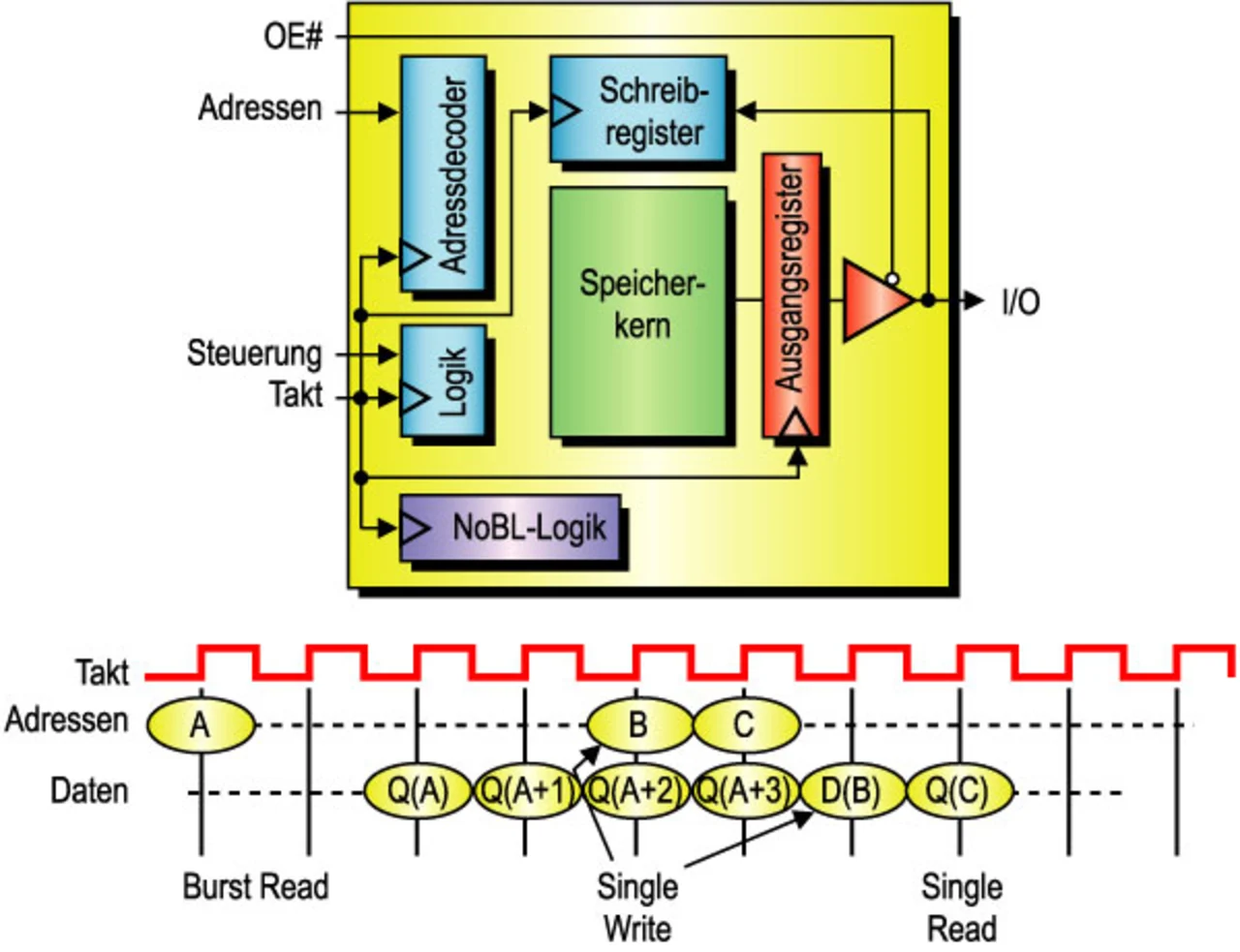

Um hier Abhilfe zu schaffen, entwickelte Cypress das No Bus Latency SRAM (NoBL). NoBL SRAMs haben Ähnlichkeit mit Standard Synchronous SRAMs, doch wird der sonst fällige Wait State durch zusätzliche Logik vermieden. Dies wiederum ergibt eine 100-prozenti-ge Bus-Auslastung unabhängig vom Schreib/Lese-Profil, denn es können mit jedem Taktzyklus Daten übertragen werden. Dieses Merkmal sorgt dementsprechend für eine drastische Verbesserung der Speicher-Performance speziell dort, wo häufig zwischen Lese- und Schreibzugriffen gewechselt wird.

Zur Vermeidung der bei Standard Synchronous SRAMs erforderlichen Wait States setzen NoBL SRAMs voraus, dass die Daten für eine Schreib-Operation symmetrisch zu einer Lese-Operation sind. Das bedeutet, dass der Offset, mit den Steuer- und Daten-Informationen auf den Datenbus gegeben werden, für Lese- und Schreibzugriffe identisch sein muss.

Flow-Through vs. Pipelined NoBL SRAM

Ebenso wie die zuvor beschriebenen Standard Synchronous SRAMs werden auch NoBL SRAMs in Flow-Through- und Pipelined-Version angeboten. Im Unterschied zu Standard Synchronous SRAMs unterstützen NoBL SRAMs keine Single-Cycle-Schreiboperationen, damit sie eine Busauslastung von 100 % erreichen können. Single-Cycle-Writes würden ebenso wie bei den Standard Synchronous SRAMs Wait States erfordern, da die Pipeline erneut geladen werden müsste. Der konstante Offset zwischen Adressen und Daten bei der Ausführung von Lese- und Schreibzugriffen ist aus den Bildern 4 und 5 ersichtlich. Wie man sieht, beträgt der Offset bei der Flow-Through-Architektur stets einen Zyklus, während es bei der Pipelined-Variante zwei Zyklen sind.

- Der SRAM-Report 2004

- Asynchrone SRAMs

- Quad Data Rate SRAMs

- Synchrone SRAMs in der Standard-Ausführung