Ein Überblick über die Optionsvielfalt bei SRAMs

Der SRAM-Report 2004

Fortsetzung des Artikels von Teil 2

Quad Data Rate SRAMs

Selbst mit der Einführung der NoBL-Architektur und der damit einhergehenden Leistungs-Steigerung gegenüber dem Standard Synchronous SRAM gibt es noch einige Systeme, denen auch diese zusätzliche Leistungsfähigkeit nicht genügt. Cypress, Renesas, IDT, NEC und Samsung haben sich deshalb zusammengetan, um die QDR SRAMs zu definieren. Mit der QDR-Architektur soll den Belangen von Systemen mit großem Bandbreitenbedarf Rechnung getragen werden, die kürzere Latenzzeiten und wesentlich höhere Bandbreiten erfordern als sie mit der NoBL-Technik möglich sind. Um die Speicherbandbreite auf der System-Ebene spürbar anzuheben, mussten mehrere Änderungen vorgenommen werden.

Jobangebote+ passend zum Thema

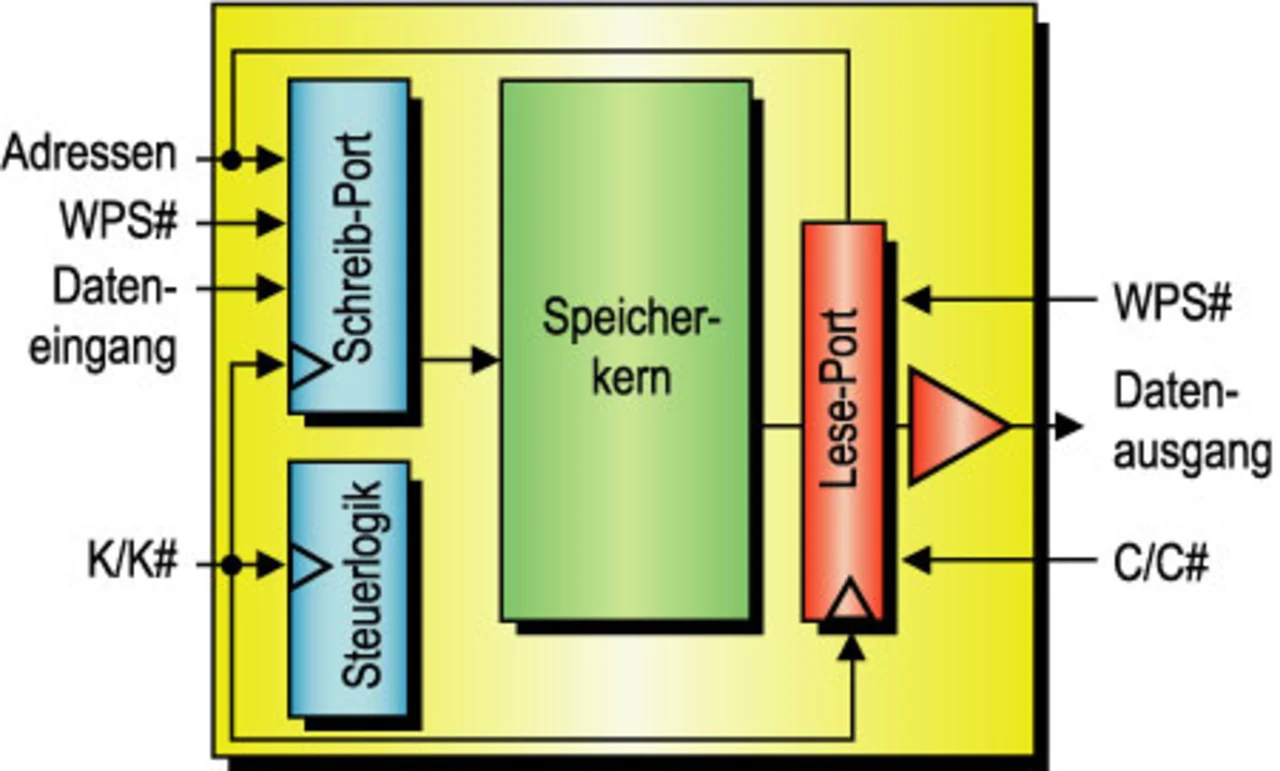

Einer der wichtigsten Unterschiede zwischen QDR und NoBL SRAMs ist, dass QDR SRAMs über separate Lese- und Schreib-Ports verfügen, die unabhängig voneinander arbeiten und gleichzeitige Lese- und Schreib-Operationen unterstützen (Bild 6). Das Risiko eines Konkurrenzbetriebs wird dadurch vollständig ausgeschlossen. Ein weiterer wesentlicher Unterschied ist, dass QDR SRAMs gleichzeitige Transaktionen zulassen. Lese- und Schreib-Operationen können somit nebeneinander in ein und demselben Taktzyklus ablaufen. QDR SRAMs haben außerdem DDR-Schnittstellen (Double Data Rate), was den Transfer von Daten sowohl bei steigenden als auch bei fallenden Taktflanken erlaubt. Ein weiterer grundlegender Unterschied zwischen QDR und NoBL SRAMs ist die „Shared Address“-Funktion der QDR-Speicher. Lese- und Schreib-Ports nutzen den Adressbus hier gemeinsam, damit das System mit weniger Pins auskommt. Schließlich unterstützen QDR SRAMs zwei Takteingänge (K und K#) als Ersatz für den bei SRAMs normalerweise verwendeten massebezogenen Eingangstakt (single ended).

Als Resultat all dieser Unterschiede können QDR SRAMs zwei Transaktionen gleichzeitig mit DDR-Transferraten unterstützen, was unter dem Strich eine Vervierfachung ergibt – daher die Bezeichnung Quad Data Rate (QDR). Diese Vervierfachung der Datenrate lässt sich erzielen, wenn Lese- und Schreib-Ports ununterbrochen aktiv sind.

Anders als Standard Synchronous SRAMs und NoBL SRAMs, die mit unterbrechbaren Bursts arbeiten, sind die Bursts von QDR SRAMs nicht unterbrechbar. Eine vorzeitige Beendigung oder Unterbrechung von Burst-Zyklen ist zwar nicht möglich, doch lassen sich bei Bedarf Teile der Schreib-Daten mit den „Byte-Write Control Pins“ ausblenden.

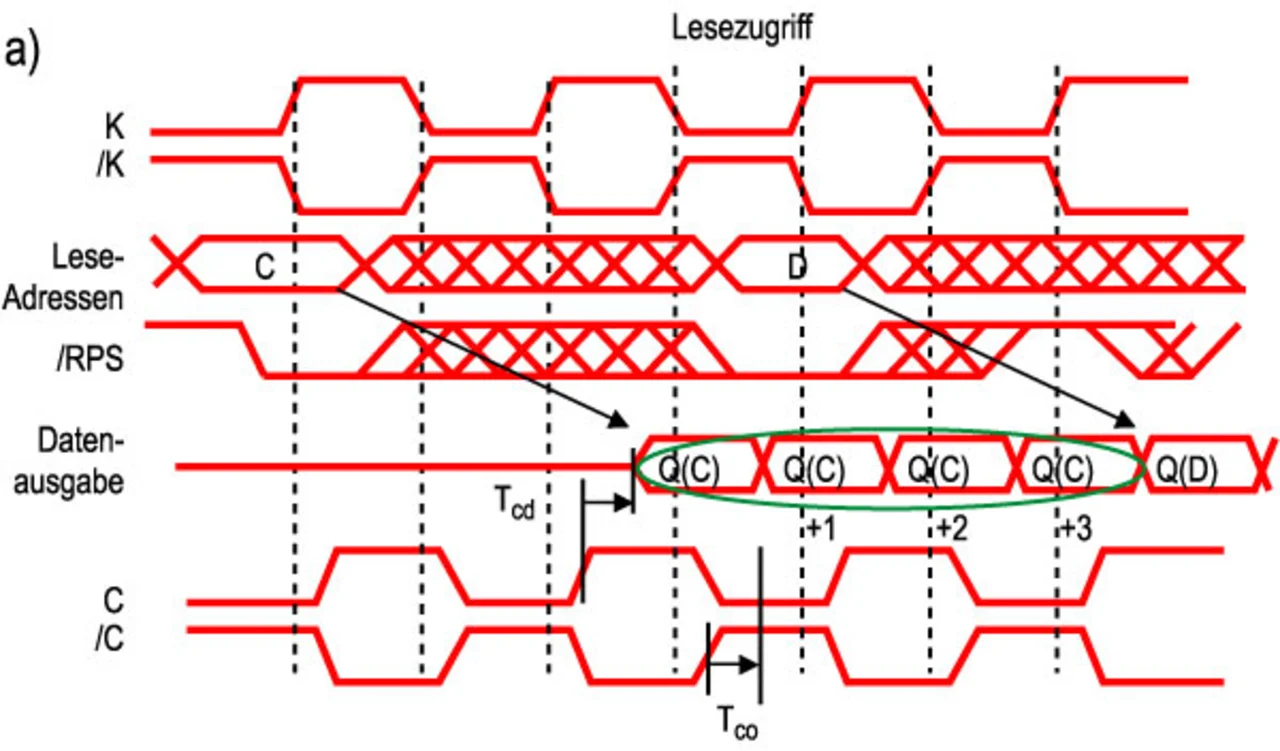

QDR SRAMs werden in zwei Haupt-Varianten angeboten: als 2-Word-Burst- und als 4-Word-Burst-Version. Sie unterscheiden sich durch die Länge der Bursts, die pro Transaktion unterstützt werden. Der Ablauf der Transaktionen beider Versionen ist nachfolgend dargestellt. Besonders interessant ist, dass die „Burst-of-2“-Version einen feinstufigeren Zugriff auf das Speicher-Array erlaubt, da jeweils nur auf 2 anstatt auf 4 byte zugegriffen wird. Andererseits sind dann auf dem Adressbus doppelt so viele Transaktionen nötig wie bei der „Burst-of-4“-Variante.

QDR-II: Die Entwicklunggeht weiter

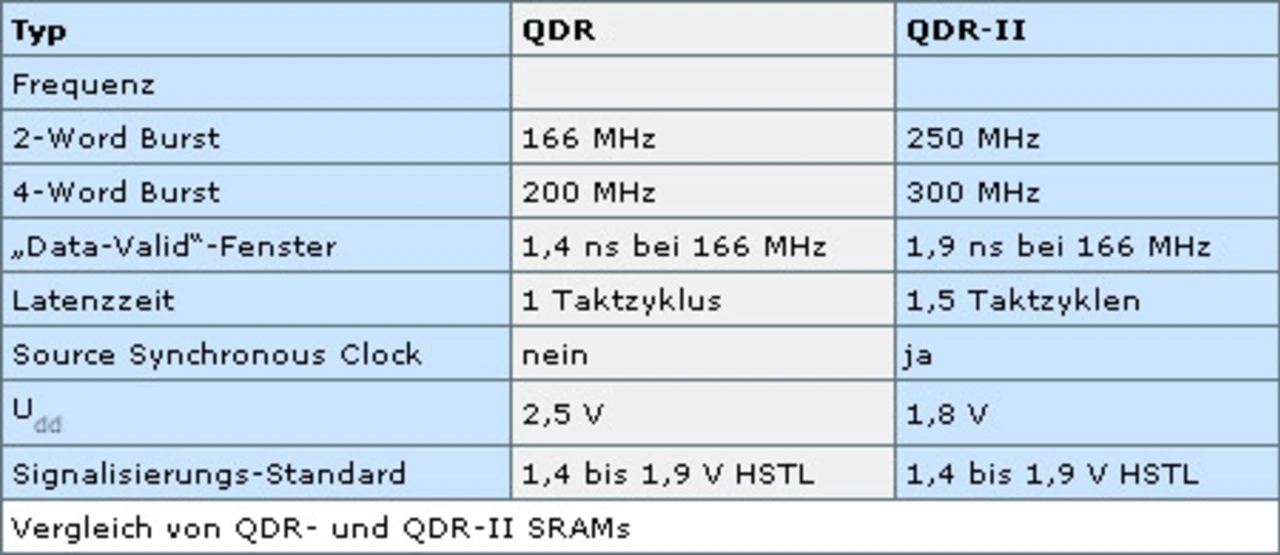

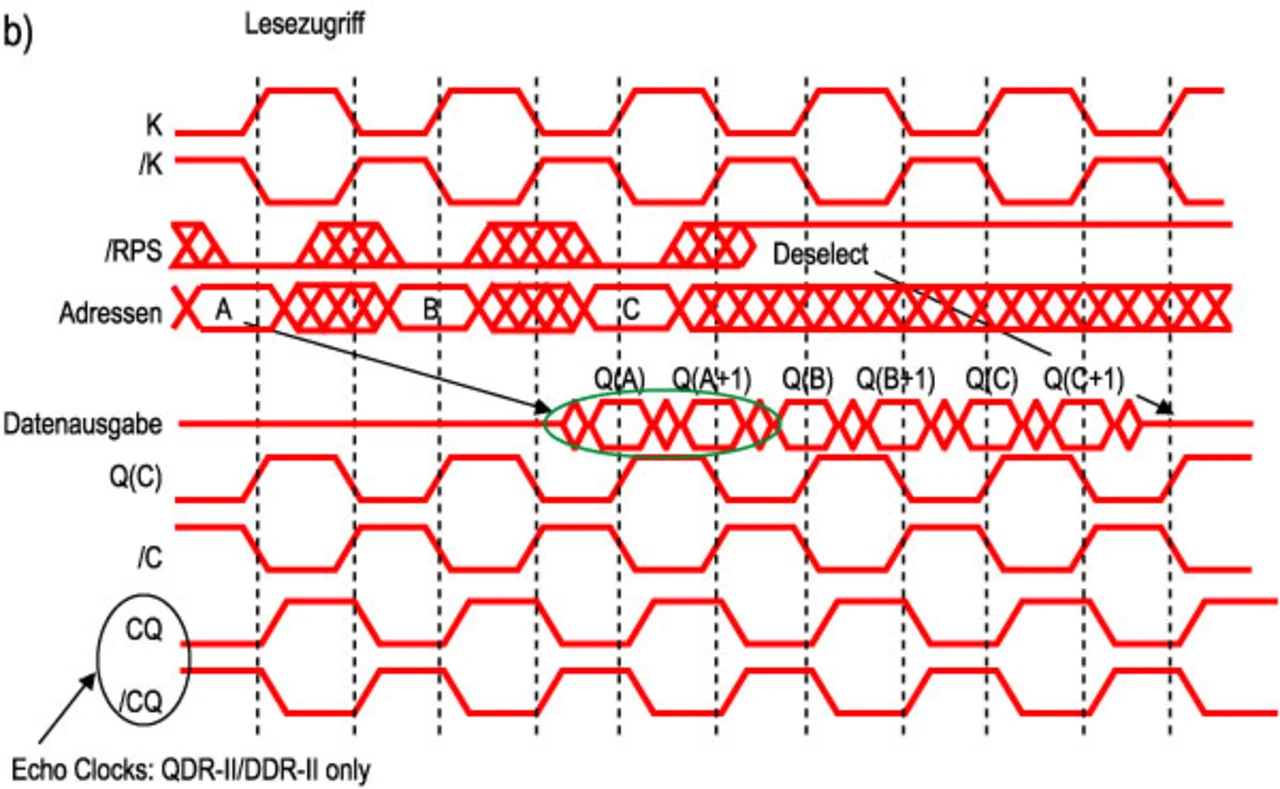

QDR-II SRAMs ähneln den QDR SRAMs, weisen jedoch einige leistungssteigernde Verbesserungen auf. Zum Beispiel verfügen QDR-II-Bausteine über ein Paar „Source Synchronous Clocks“, die beim Erfassen von Daten am Controller helfen. Diese Source Synchronous Clocks sind Ausgänge des SRAM und werden auch als „Echo Clocks“ (CQ und CQ#) bezeichnet. Die Echo-Clock-Ausgänge sind in ihrem Timing präzise an den Daten-Ausgängen ausgerichtet und können als Indikatoren für das Vorliegen gültiger Daten oder zur Triggerung des Eingangsregisters des empfangenden Bausteins verwendet werden. Das von QDR-II SRAMs produzierte „Data-Valid“-Fenster ist deshalb bei gleicher Frequenz insgesamt um etwa 35 % breiter als das von QDR-Bausteinen. QDR-II-Produkte weisen überdies verglichen mit QDR-Bausteinen eine zusätzliche Latenzzeit von einem halben Zyklus auf, was bei minimalem Einfluss auf die Anfangs-Latenzzeit wesentlich höhere Frequenzen und Bandbreiten zulässt. Einige Unterschiede zwischen QDR und QDR-II SRAMs zeigt die Tabelle.

DDR SRAMs

Während QDR SRAMs für Anwendungen mit einem ausgeglichenen Aufkommen an Lese- und Schreibzugriffen gedacht sind, bietet sich die DDR-SRAM-Architektur hauptsächlich für Anwendungen an, die ein „Daten-Streaming“ (d.h. viele Lesezugriffe, gefolgt von vielen Schreibzugriffen) erfordern und wesentlich mehr Bandbreite benötigen, als sie von Standard Synchronous oder NoBL SRAMs geboten werden.

Beim Streaming von Daten beträgt das kurzfristige Verhältnis zwischen Lese- und Schreib-Operationen entweder 100 % Lese- oder 100 % Schreibzugriffe, auch wenn sich beide Zugriffsarten langfristig die Waage halten. Bei einem QDR SRAM würde dies dazu führen, dass jeweils einer der Ports (und mit ihm die dazugehörigen Pins) ungenutzt bleiben. Dies gab Anlass zur Entwicklung des DDR SRAMs, in dem Ein- und Ausgangsdaten denselben Datenbus benutzen (Common I/O). Das beim Wechsel zwischen Schreib- und Lesezugriffen erforderliche Umschalten des Busses (Bus Turnaround) verringert zwar die verfügbare Bandbreite. In bestimmten Systemen ergeben sich jedoch unter dem Strich eine insgesamt bessere Bus-Auslastung und eine wesentliche Steigerung der Gesamt-Bandbreite, denn während der verlängerten Bursts können alle Datensignale genutzt werden, und der Datendurchsatz erreicht ein Maximum.

Ebenso wie QDR SRAMs werden auch DDR SRAMs als 2-Word-Burst- und als 4-Word-Burst-Ausführung (Bild 7) angeboten. Welcher dieser Varianten der Vorzug zu geben ist, hängt von der geforderten Feinstufigkeit der Daten und der Datenbusbreite des Speichers ab.

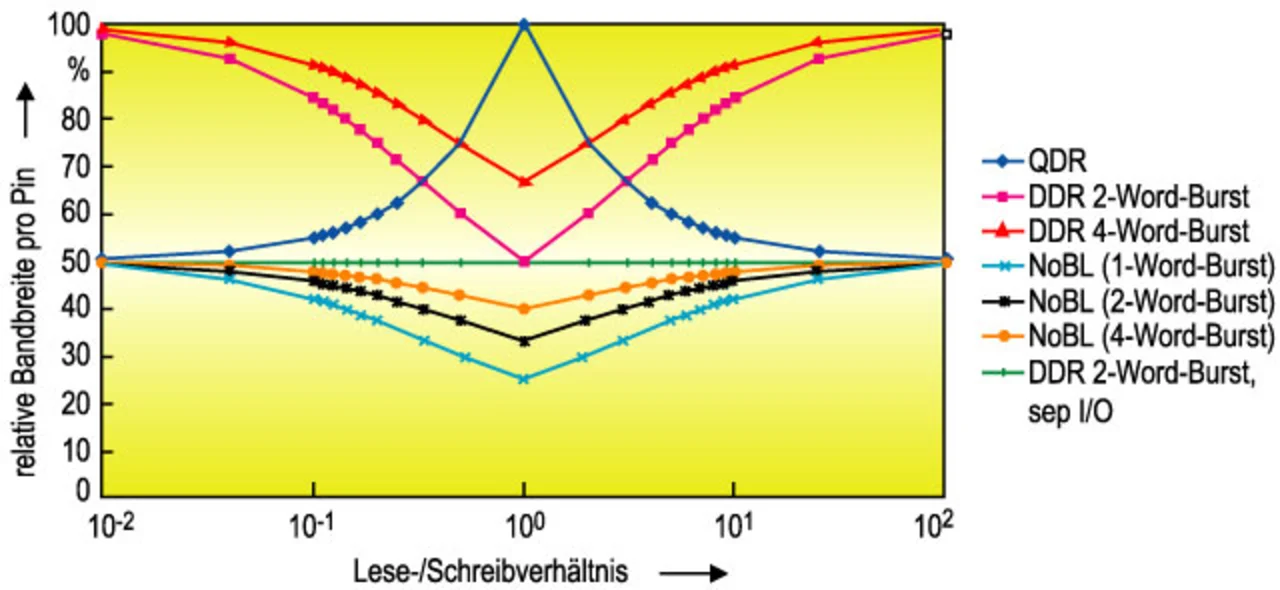

Bild 8 zeigt die Leistungsfähigkeit verschiedener synchroner SRAMs in Netzwerk-Applikationen im Hinblick auf die relative Bandbreite pro Pin.

- Der SRAM-Report 2004

- Asynchrone SRAMs

- Quad Data Rate SRAMs

- Synchrone SRAMs in der Standard-Ausführung