Ein Überblick über die Optionsvielfalt bei SRAMs

Der SRAM-Report 2004

Fortsetzung des Artikels von Teil 1

Asynchrone SRAMs

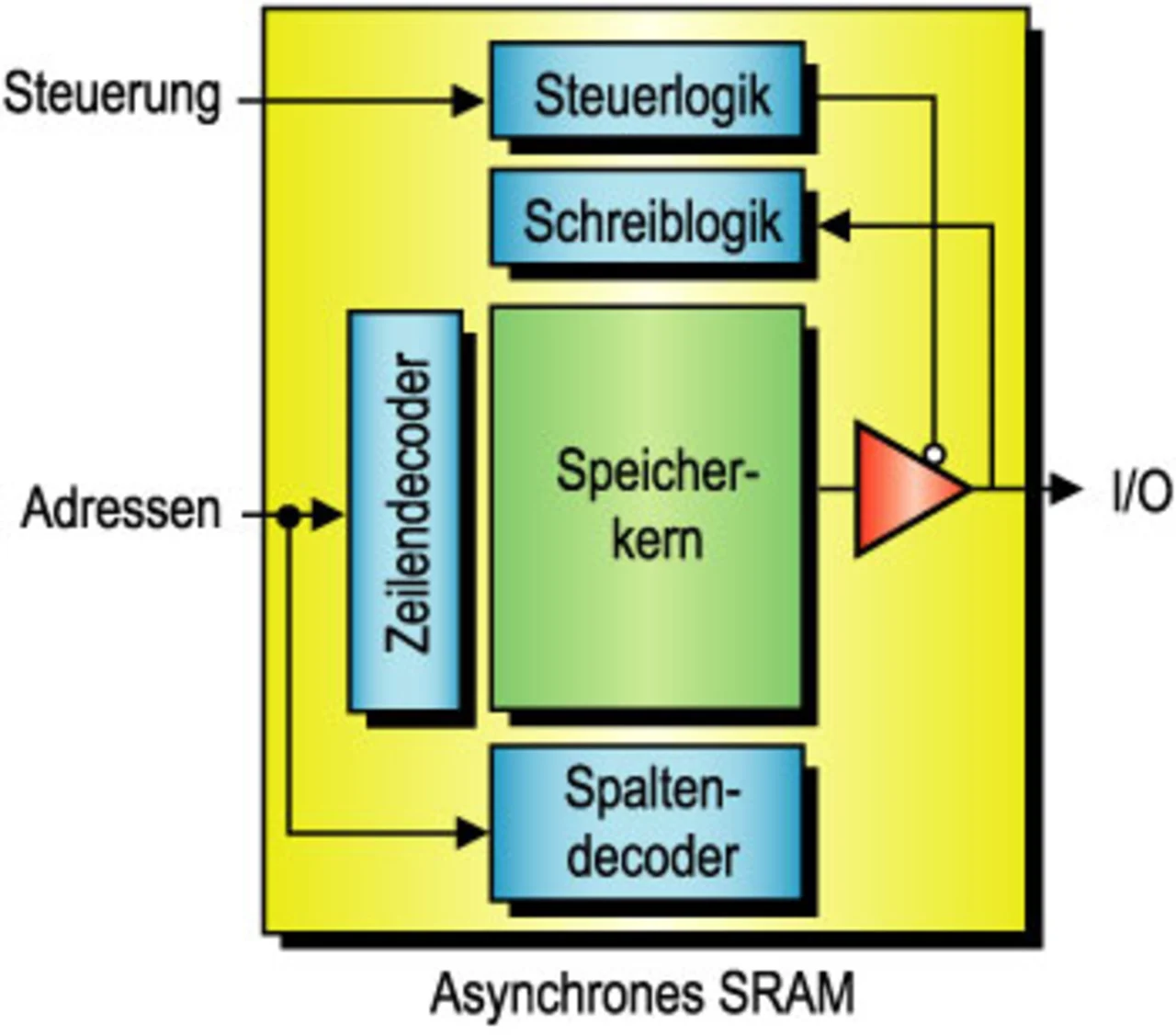

Die zweite wichtige SRAM-Kategorie sind die asynchronen SRAMs. Als asynchron bezeichnet man SRAMs, die keinen Takteingang besitzen (Bild 9). Schreib- und Lese-Operationen werden hier ausgeführt, sobald der Baustein einen entsprechenden Befehl erhält.

Jobangebote+ passend zum Thema

Zu den größten Vorteilen asynchroner SRAMs gehört die Tatsache, dass diese Bausteine seit Jahrzehnten eingesetzt werden und entsprechend vertraut sind. Da es asynchrone SRAMs bereits seit so langer Zeit gibt, sind die in vielen Standard-Prozessoren enthaltenen Speicher-Controller mit Schnittstellen für asynchrone SRAMs ausgestattet, so dass sich der Designaufwand auf ein Minimum reduziert.

Die typische Zugriffszeit asynchroner SRAM-Bausteine liegt bei 8 ns oder mehr. Deshalb werden diese Bausteine vorwiegend in Systemen mit maximalen Taktfrequenzen von 100 MHz eingesetzt.

Asynchrone SRAMs lassen sich in zwei Gruppen unterteilen: Fast Asynchronous SRAMs und Low Power Asynchronous SRAMs (MoBL).

Fast Asynchronous SRAMs

Asynchrone SRAMs mit Zugriffszeiten von 35 ns oder weniger können als „Fast Asynchronous SRAMs“ bezeichnet werden. Diese Speicher werden meist in älteren Systemen verwendet und nehmen relativ viel Leistung auf (0,5 W oder mehr sind keine Seltenheit). Typische Einsatzgebiete sind L2-Cache-Speicher in älteren PCs, Scratchpad-Speicher und Pufferspeicher in industriellen Applikationen, um nur einige zu nennen.

Low Power Asynchronous SRAMs (MoBL)

In einigen Anwendungen (z.B. Mobiltelefone oder Pager) kommt es mehr auf die Verlustleistung als auf die Performance an. Aus diesem Grund haben Anbieter wie Cypress eine SRAM-Familie mit extrem niedriger Leistungsaufnahme eingeführt. Die Strom sparenden SRAMs der MoBL-Familie (More Battery Life) arbeiten mit Zugriffszeiten im Bereich von 40 ns oder darüber, sind dafür aber auf eine niedrige Verlustleistung optimiert. Die typische Standby-Verlustleistung kann 10 µW oder weniger betragen, die aktive Leistungsaufnahme 30 mW oder weniger. Diese Speicher gibt es mit unterschiedlichsten Kapazitäten von 64 Kbit bis 16 Mbit.

Pseudo SRAMs (PSRAMs)

Wenn Kapazitäten von mehr als 16 Mbit benötigt werden, sind Pseudo SRAMs (PSRAMs) eine mögliche Lösung. Ein Pseudo SRAM ist ein Speicherbaustein mit einem DRAM-Kern und einer „SRAM-ähnlichen“ Schnittstelle. Der DRAM-Kern besteht pro Speicherzelle aus einem Transistor und einem Kondensator. Da PSRAMs auf DRAM-Technik basieren, die eine höhere Kapazität oder einen günstigeren Preis pro Bit zulässt, ist eine periodische Auffrischung erforderlich. Während sich jedoch die entsprechende Refresh-Steuerung bei herkömmlichen DRAMs außerhalb des Speichers befindet, ist sie bei PSRAMs in den Baustein integriert. Entsprechend einfach lassen sich PSRAMs nutzen, um die Kapazität anderer asynchroner SRAMs aufzustocken.

Breites Spektrum

Trotz der prinzipiell großen Auswahl an SRAM-Bausteinen werden die Wahlmöglichkeiten des Designers in einigen Fällen eingeschränkt. Die in vielen etab-lierten Prozessoren integrierten Speicher-Controller unterstützen bestimmte SRAM-Architekturen, doch sind neuere Prozessoren so flexibel konstruiert, dass sie Support für mehrere SRAM-Bauarten bieten. Für die Wahl des richtigen Typs kommt es darauf an, die Prioritäten des Speicher-Subsystems (Bandbreite, Anfangs-Latenzzeit, aktive Leistungsaufnahme, Standby-Leistungsaufnahme, Preis usw.) zu definieren und auch die Gegebenheiten des Systems (Verhältnis zwischen Lese- und Schreibzugriffen, Betriebsfrequenz usw.) zu berücksichtigen.

Auch innerhalb ein und desselben Systems werden durchaus nicht an alle Speicher die gleichen Anforderungen gestellt. Zum Beispiel beträgt das Schreib-Lese-Profil in Netzwerk-Anwendungen tendenziell nahezu 50:50, was einen Baustein der QDR-Familie am günstigsten erscheinen lässt. Bei anderen Anwendungen (sogar bei anderen Funktionen innerhalb desselben Systems) besteht dagegen möglicherweise ein ungleiches Verhältnis zwischen Schreib- und Lesezugriffen, sodass eine Common-I/O-Architektur (z.B. Standard Synchronous, NoBL oder DDR) vorzuziehen wäre.

Andere Systeme verlangen nach möglichst niedriger Leistungsaufnahme, um eine möglichst lange Batterielebensdauer zu erreichen, während wieder andere mehr Speicherkapazität erfordern, als sie von SRAM-Herstellern geboten werden kann. MoBL SRAMs und PSRAMs sind hier die aussichtsreichsten Anwärter.

Schließlich sollen auch jene Applikationen nicht unerwähnt bleiben, die hinsichtlich des SRAM-Typs keinerlei Wahlfreiheit bieten, da sie bereits über einen fest konfigurierten Speicher-Controller verfügen.

| Ritesh Mastipuram ist derzeit als Applikations-Ingenieur bei der Memory Products Division von Cypress Semiconductor tätig. Neben einem Bachelor-Diplom der Bangalore University (Indien) besitzt er ein Master-Diplom in Elektrotechnik der Wright State University. Er war bei Cypress Semiconductor in den vergangenen zwei Jahren an der Soft Error Task Force beteiligt und in der Definition neuer Produkte sowie der System-Analyse tätig. E-Mail: REF@cypress.com |

Verwandte Artikel:

- Der SRAM-Report 2004

- Asynchrone SRAMs

- Quad Data Rate SRAMs

- Synchrone SRAMs in der Standard-Ausführung