Blick ins Kerngehäuse

Der Cortex-M3 im Vergleich zu ARM 7 – Stromverbrauch

Fortsetzung des Artikels von Teil 1

Wie der STM32 den Stromverbrauch drosselt

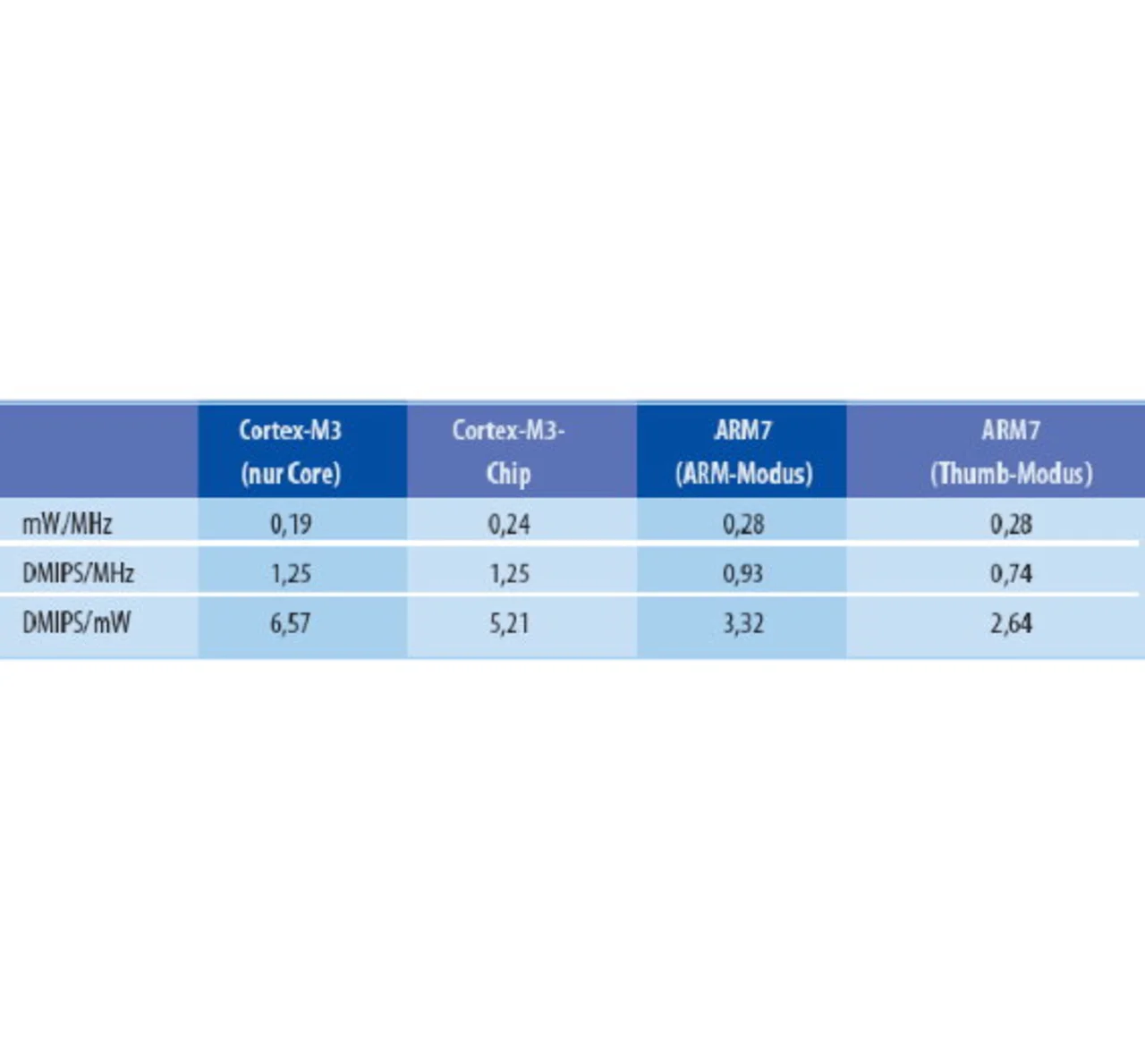

Beim Cortex-M3-basierenden STM32- Mikrocontroller wurde gegenüber ARM7 bereits im Core sehr viel Wert auf Stromoptimierung durch Low- Power-Modi gelegt (Tabelle 1). Die Gesamtstromaufnahme eines Mikrocontrollers setzt sich aus der dynamischen Stromaufnahme, verursacht durch die Schaltaktivität der Logikkreise, und der statischen Stromaufnahme durch Leckströme sowie der statischen analogen Ströme zusammen. Werden nicht benötigte Mikrocontrollerkomponenten einfach vom Takt abgeschaltet, so reicht das nicht unbedingt für Low-Power aus, da die statischen Anteile noch vorhanden bleiben.

Um auch diese zu reduzieren, muss die Versorgungsspannung für diese Komponenten reduziert oder noch besser komplett abgeschaltet werden. Hierfür sind verschiedene „Power Domains“ nötig. Der wichtigste ist ein kleiner Bereich, der immer angeschaltet bleiben muss und in der Lage ist, die anderen Bereiche selektiv ab- oder anzuschalten. Wird ein Bereich komplett von der Spannung abgeschaltet, kann dies Datenverlust bedeuten: Eine CPU oder ein RAM verliert dann den Inhalt der Register oder Speicherzellen, was dann wieder auf den Aufweckvorgang Einfluss hat. Der Bereich, der immer angeschaltet bleibt, sollte einen sehr niedrigen statischen Stromverbrauch haben. Beim STM32 sind hier im Wesentlichen drei verschiedene Bereiche implementiert:

Der Bereich „VDD Backup Master Voltage“ basiert auf hochspannungsfesten Transistoren. Da hier eine sehr kleine statische Stromaufnahme erzielt werden soll, werden hier Transistoren mit dicker Gateoxid-Schicht eingesetzt. Sie werden direkt mit der Versorgungsspannung UDD gespeist. Dieser Bereich enthält die Steuerung für die Stromsparmodi sowie einen sparsamen RC-Oszillator und einen Watchdog („independent Watchdog“). Die Anzahl der Gatter ist absichtlich sehr klein gehalten.

Der Bereich „Slave Main Core Voltage“ erfasst die übrigen Bereiche, d.h. CPU, Speicher und die meisten Peripherieeinheiten. Diese werden, um den dynamischen Stromverbrauch zu reduzieren, mit geringerer Spannung betrieben. Hier wurde auf kleinen Stromverbrauch bei hoher Performance optimiert.

Der Bereich „RTC-Voltage Domain“ ist ein gesonderter Bereich, der durch eine Knopfbatterie betrieben werden kann. Er sorgt dafür, dass die Echtzeituhr und die Backup-Register (ein kleiner Speicherbereich von 40 16-bit- Registern) auch ohne Stromversorgung weiterhin funktionieren. Eine entsprechende Logik sorgt dafür, dass bei anstehender Stromversorgung der Bereich durch diese versorgt und damit die Knopfzelle entlastet wird. Dadurch kann eine Batterielebensdauer von mehreren Jahren erreicht werden. Dieser Bereich verbraucht ca. 1,4 µA bei 3,3 V.

Für das Einschalten der Low- Power-Modi wurden zwei besondere Befehle geschaffen: „Wait for interrupt“ (WFI) und „Wait for event“ (WFE). WFI schaltet in den Low-Power-Modus und setzt die Befehlsabarbeitung erst bei einem Interrupt (der fähig ist, in den Run-Modus zu schalten) fort. Tritt in der Wartephase ein Interrupt auf, dann wird die Interrupt Service Routine (ISR) bedient. Bei Beendigung der ISR gibt es zwei Möglichkeiten. Erstens: Die Befehlsausführung wird nach dem WFI-Befehl ganz normal fortgesetzt, d.h., der Controller bleibt nach der ISR im Run-Modus. Ist das „Sleep on exit“-Bit im System- Control-Register gesetzt, so wird die zweite Möglichkeit aktiviert, und der Controller wird nach Beendigung der ISR wieder in den Low- Power-Modus gesetzt. Hiermit ist eine rein interruptbetriebene Low- Power-Applikation möglich.

Das „Aufwecken“ und wieder „Einschlafen“ ist hier direkt im Controller implementiert und benötigt keinen zusätzlichen Software-Code. Der Befehl WFE steuert die Fortsetzung der Befehlsausführung, ausgelöst durch ein Ereignis. Hiermit kann durch einen „Wake-up event“ direkt in den Run-Modus geschaltet werden, ohne dass Interrupts benötigt werden. Technisch umgesetzt wird dies durch eine Interrupt-Leitung eines Peripheriegeräts, dessen Interrupt-Aktivierung im Interrupt-Controller deaktiviert ist. Zusätzlich wurde im System-Control- Register noch ein „Sleepdeep“-Bit (siehe auch weiter unten) realisiert. Ist es gesetzt, dann signalisiert die Low- Power-Logik der CPU den Power- Down-Modus auch an die Peripherie und die PLL, damit auch diese ausgeschaltet werden können. Diese tief in den Cortex-M3-Kern integrierte Logik zum Steuern der Stromsparmodi konnte beim ARM7 vom Chiphersteller nicht so effektiv realisiert werden.

Jobangebote+ passend zum Thema

- Der Cortex-M3 im Vergleich zu ARM 7 – Stromverbrauch

- Wie der STM32 den Stromverbrauch drosselt

- STM32-Powermodi: Stromsparen in allen Betriebszuständen

- Darstellung der Stromsparmodi mit dem STM32-PerformanceStick